Samsung and TSMC Roadmaps: 8 and 6 nm Added, Looking at 22ULP and 12FFC

by Anton Shilov on May 5, 2017 9:30 AM ESTBeyond 10 nm at Samsung: 8 nm and 6 nm

Samsung’s 7 nm manufacturing technology is still expected to be the company’s first process to use extreme ultraviolet lithography (EUVL) for high-volume manufacturing (HVM) and that is going to happen sometimes in 2019 or later (risk production starts in the second half of 2018). In fact, the next several years down the road is where things will start to get interesting as Samsung announced another two new production technologies it has not talked about before: the 8 nm and the 6 nm processes.

| Industry FinFET Lithography Roadmap, HVM Start Data announced by companies during conference calls, press briefings and in press releases |

||||||||||||

| 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | |||||||

| 1H | 2H | 1H | 2H | 1H | 2H | 1H | 2H | |||||

| GlobalFoundries | 14LPP | 7nm DUV | 7nm with EUV* | |||||||||

| Intel | 14 nm 14 nm+ |

14 nm++ 10 nm |

10 nm+ 10 nm++ |

|||||||||

| Samsung | 14LPP 14LPC |

10LPE | 10LPP | 8LPP 10LPU |

7LPP | 6 nm* (?) | ||||||

| SMIC | 28 nm** | 14 nm in development | ||||||||||

| TSMC | CLN16FF+ CLN16FFC | CLN10FF CLN16FFC |

CLN7FF CLN12FFC |

CLN12FFC/ CLN12ULP |

CLN7FF+ | 5 nm* (?) | ||||||

| UMC | 28 nm** | 14nm | no data | |||||||||

| *Exact timing not announced **Planar |

||||||||||||

Officially, Samsung says that both technologies will offer “greater scalability, performance and power advantages when compared to existing process nodes,” which obviously means that they are across the board better than Samsung’s current-gen 14 nm and 10 nm offerings. What is important is that Samsung also says that the “8 nm and the 6 nm will inherit all innovations from the latest 10 nm and the 7 nm technologies” respectively. This means that the 8 nm is set to keep using DUV and multi patterning (triple patterning or even quad patterning to be exact, but Samsung has not confirmed usage of the latter) for critical layers, whereas the 6 nm will come after 7 nm and will be Samsung’s second-generation EUV technology.

The only thing that Samsung confirms about its 8LPP manufacturing technology right now is the fact that this is a DUV-based process technology designed to shrink die size (i.e., increase transistor density) and frequency compared to the 10LPP fabrication process. Given the name of the technology and its key advertised advantages over direct predecessor, it is highly likely that the 8LPP will be used to make high-performance SoCs in 2019.

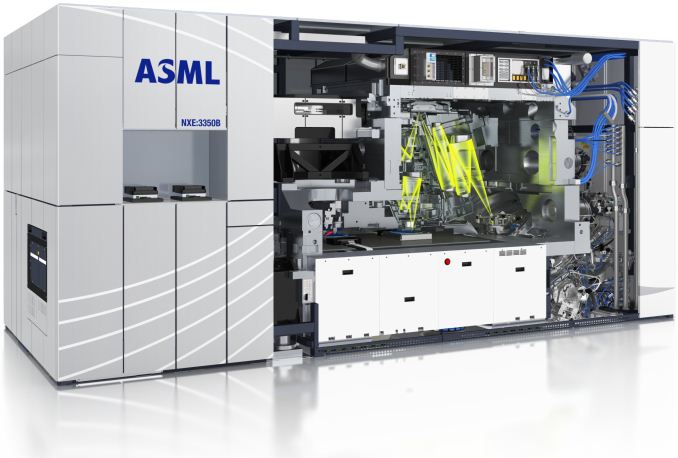

Since Samsung plans to start risk production using the 7LPP in the second half of 2018, the technology is hardly going to be used for high-volume manufacturing before the second half of 2019. Keeping in mind that Samsung now begins HVM using its leading-edge process technologies in October, it is possible that it is going to kick-off 7LPP HVM in fall 2019, but the 8LPP will be Samsung’s most advanced process technology for the better part of the year. Samsung does not mention timeframes for its 6 nm process technology and what to expect from it, but it is logical to assume that it will require more layers to be processed using ASML's EUV tools (like the NXE:3350B pictured above) in a bid to provide PPA advantages and it not be used for high-volume manufacturing before late 2020.

In March, Samsung only made brief announcements regarding its 10LPU, 8LPP and 6 nm process technology without disclosing their exact specifications or even PPA improvements targets. The addition of at least two more DUV technologies (the 10LPU and the 8LPP) in general may indicate that EUV may not be the best choice for all applications in 2019 – 2021, which is perfectly logical. Then again, we do not know how DUV and EUV technologies will co-exist early in the EUV era.

We are going to learn more about Samsung’s plans in the foundry industry in late May, when the company hosts its 2017 U.S Samsung Foundry Forum. So, we will have to wait for a couple of months for Samsung to disclose the whole picture regarding its upcoming process technologies.

89 Comments

View All Comments

Demon-Xanth - Friday, May 5, 2017 - link

A silicon atom's width is about 110pm, so they are literally going into widths that are only double digit numbers of atoms wide.MananDedhia - Friday, May 5, 2017 - link

Processes that deposit single atomic layers are already used commonly in processes - even in 28nm.....For some layers, atomic layer deposition is the only way to go. The complexity increased here because we are now increasing the number of layers and devices that need to be defined at those scales.bug77 - Friday, May 5, 2017 - link

Yes, but you can't take 3 atoms, call then source, drain and gate and assemble them into a transistor.ddriver - Friday, May 5, 2017 - link

Why not? IBM have already demoed atomic assembly. The downside - it is very slow, it is one atom at a time VS etching septillions of atoms with acid at the same time.BTW I finally get how they will get to 5 nm - by lying about it. How much of a 10nm chip's features are at 10nm resolution? Not many. Area decrease is already falling behind the process scale number and it is only going to get worse.

On the upside - no biggie - we already have enough performance to run terminators. So our extinction is well assured.

philehidiot - Friday, May 5, 2017 - link

Don't you go worrying about terminators. I've already started work on the first of many. I was just so sick of not being able to get a seat on the bus. Was thinking no one wants to sit next to a cybernetic killing machine so I can send that to the earliest bus stop, get it to reserve a seat and I can ride to work without the smell of unwashed, practically rotting human being next to me.Far safer than one of those self driving car things. Bloody death traps.

Kevin G - Sunday, May 7, 2017 - link

Are you Sarah Conner?Xajel - Sunday, May 7, 2017 - link

Yeah they're actually moving these actual atoms... atom by atom like a legoKevin G - Sunday, May 7, 2017 - link

The node size is mostly marketing now which is why Intel went out of their way to define some new metrics ~6 weeks ago. While I wasn't a fan of that marketing spiel, there is a point that there needs to be a new metric as traditional node shrinks are few and far between going forward.What I think the foundries are waiting on is a new big break through as they realize that they cannot currently continue on the existing path indefinitely. Germanium can come in as an exotic material as a substitute for silicon but wafer prices are extremely expensive. Even then, germanium doesn't even solve the node problem but rather just provides better material properties at existing nodes. Carbon nanotubes and graphene are two related materials seen as potential for replacing silicon as we get even closer to the atomic level. Both have some good properties for circuit design but no one has found a means of economical mass production.

Both Intel and IBM has invested heavily into silicon photonics. So far their efforts have lead to advancements in IO but not raw processing but optical logic gates do exist. Much like other exotic solutions, these suffer from mass production problems to bring them out of the research lab. (Notice a trend starting here?)

I think strategies like interposers and EMIB are emerging to side step the absolute need for shrinks in the sense of limiting transistor counts. Granted interposers/EMIB do nothing with regards to power consumption. The one nice thing about these techniques is that they do potentially allow for mixing some of the more exotic solutions with bulk processes. For example, a die with slicon photonics could interface with some high speed optical circuits in the package and also interfaces with more traditional bulk processes for its SRAM cache. Very expensive but worth considering when there are other new node alternatives available. Granted, such choices are not going to happen tomorrow but they're clearly on the horizon.

eachus - Sunday, October 1, 2017 - link

My read is that the first application of nanotubes or graphene will be laying down a copper layer, then growing graphene on top of it. The trick will be to get the graphene to align on top of the copper, which will probably take another layer in between, perhaps silver. Could silver be substituted for copper in bulk? Good question. It is a better conductor and solves the alignment problem.You may think of silver as a precious metal along with gold and platinum, but over fifty per cent of the silver mined goes into silver solder for brazing or soldering metals together. Most silver solder is used for brazing, go figure. Silver is also used in thermal compounds for getting a good seal between a CPU chip and the heat sink. Obviously replacing a few grams of copper with silver inside the chip won't raise prices significantly.

Getting copper to bond to the graphene is not a problem--even if the reverse is a significant problem. However high-temperature processes may damage the graphene. Best is probably a "wet" process to put a thin layer of copper on the graphene before building the next litho layer. Putting the graphene in a copper sandwich like this should significantly improve the characteristics of the layer. This will show up as a reduced capacitance with adjacent conducting traces--less cross-talk and faster signal propagation.

beginner99 - Monday, May 8, 2017 - link

"BTW I finally get how they will get to 5 nm - by lying about it"Process tech numbering hasn't been about feature size for the past 2 decades.