Intel's Process Roadmap to 2025: with 4nm, 3nm, 20A and 18A?!

by Dr. Ian Cutress on July 26, 2021 5:00 PM ESTSidebar on Intel EUV

In all of these announcements, one thing to highlight is Intel mentioning its relationship with ASML, the sole company that manufactures the EUV machines powering production of leading edge semiconductor manufacturing.

ASML is a unique company in that it is the only one that can produce these machines, because the technology behind them is often tied up with its partners and research, but also because all the major silicon manufacturers are heavily invested in ASML. For any other company to compete against ASML would require building a separate network of expertise, a decade of innovation and design, and a lot of capital. None of the major silicon vendors want to disturb this balance and go off on their own, lest it shuts them out of the latest manufacturing technology, and no research fund sees competing against the embedded norm as a viable opportunity. This means that anyone wanting EUV specialist technology has to go to ASML.

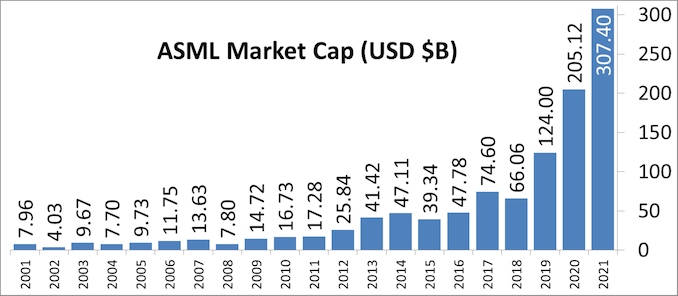

In 2012, it was reported that Intel, Samsung, and TSMC all invested in ASML. This was, at the time, to jumpstart EUV development along with migrating from 300mm wafers to 450mm wafers. While we haven’t moved to 450mm wafers yet (and there are doubts we will any time in the next decade), EUV is now here. Intel’s 2012 investment of $2.1 billion gave them a 10% stake in ASML, with Intel stating that it would continue investing up to a 25% stack. Those stakes are now below the 5% reporting threshold, but all three of the major foundry customers are still big owners, especially as ASML’s market cap has risen from $24 Billion in 2012 to $268 Billion in 2021 (surpassing Intel).

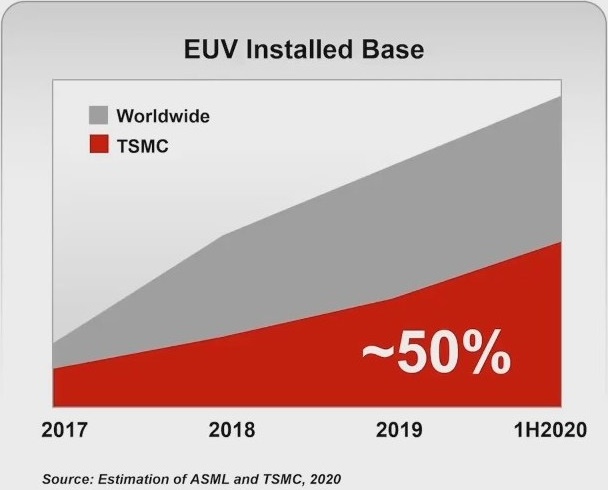

As major investors but also ASML’s customers, the race has been on for these foundries to acquire enough EUV machines to meet demand. TSMC reported in August 2020 that it has 50% of all EUV machines manufactured at ASML for its leading edge processes. Intel is a little behind, especially as none of Intel’s products in the market yet use any EUV. EUV will only intercept Intel’s portfolio with its new Intel 4 process, where it will be used extensively, mostly on the BEOL. But Intel still has to order machines when they need them, especially as there are reports that ASML currently has backorders of 50 EUV machines. In 2021, ASML is expected to manufacture around 45-50 machines, and 50-60 in 2022. The exact number of machines Intel has right now, or has ordered from ASML, is unknown. It is expected that each one has a ~$150m price tag, and can take 4-6 months to install.

With all that being said, Intel’s discussion point today is that it will be the lead customer for ASML’s next generation EUV technology known as High-NA EUV. NA in this context relates to the ‘numerical aperture’ of the EUV machine, or to put simply, how wide you can make the EUV beam inside the machine before it hits the wafer. The wider the beam before you hit the wafer, the more intense it can be when it hits the wafer, which increases how accurately the lines are printed. Normally in lithography to get better printed lines, we move from single patterning to double patterning (or quad patterning) to get that effect, which decreases yield. The move to High-NA would mean that the ecosystem can stay on single patterning for longer, which some have quoted as allowing the industry to ‘stay aligned with Moore’s Law longer’.

| ASML's EUV Shipments | |||||||||||||||||||||

| 2015 | 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | |||||||||||||||

| Actual | 2 | 4 | 10 | 3 | 4 | 5 | 6 | 4 | 7 | 7 | 8 | 4 | 7 | 14 | 8 | 7 | 9 | - | - | ||

| Target (Total) | - | - | - | 20 (18) | 30 (26) | 35 (33) | 45-50 | ||||||||||||||

| 2018 and beyond is split per quarter for actual shipped numbers Data taken from ASML's Financial Reports |

|||||||||||||||||||||

Current EUV systems are NA 0.33, while the new systems are NA 0.55. ASML’s latest update suggests that it expects customers to be using High-NA for production in 2025/2026, which means that Intel is likely going to be getting the first machine (ASML NXE:5000 we think) in mid-2024. Exactly how many High-NA machines ASML intends to produce in that time frame is unknown, as if they flood the market, having the first won’t be a big win. However if there is a slow High-NA ramp, it will be up to Intel to capitalize on its advantage.

326 Comments

View All Comments

nandnandnand - Monday, July 26, 2021 - link

https://hplusmagazine.com/2011/11/01/femtocomputin...GauravMunjal - Monday, July 26, 2021 - link

First, it's femtometer, then picometer. Second, given that most atoms are bigger than 1 angstrom, I doubt we'll ever need a smaller unit.martinpw - Monday, July 26, 2021 - link

Given that the number bears no relationship to feature size, I think we will one day be in the interesting position that the headline number used to name the process will actually be smaller than the spacing between silicon atoms (which would happen at 5A)Unashamed_unoriginal_username_x86 - Monday, July 26, 2021 - link

Nano: 10^-9Pico: 10^-12

Femto: 10^-15

I agree with your second point though

ishould - Monday, July 26, 2021 - link

Nuh uhcolaman - Monday, July 26, 2021 - link

Lol no, pico is larger than femto. Double check before you call someone out.Kevin G - Monday, July 26, 2021 - link

Marketing and switching to picometers makes the mantissa that much larger than the previous nanometer figures. Going from 3 nm to 2000 pm makes the later seem much much larger to those who don't know metric suffixes that well.Realistically you'd think that there marketing departments would do when they switched from microns to nanometers: the first few sub-micron generations were expressed as a decimal micron: 0.8 um, 0.65 um, then they switches to nanometers. Main point here is that there is a firm bottom limit to how low these numbers can go.

There is also the problem that we're up against atomic size limitations. A single silicon atom is ~118 pm wide. The difference between the 20A process and 18A process if they fully represented physical characteristics would simply be two Si atom's width.

mode_13h - Monday, July 26, 2021 - link

This only matters if they actually deliver. Intel has a gaping credibility problem. The bar is high for them to convince customers & investors they've actually fixed the root problems behind prior delays.KAlmquist - Monday, July 26, 2021 - link

If they deliver on this roadmap, that will do a lot to fix their credibility issues. Their tick-tock strategy had the following schedule:32nm 2010

22nm 2012

14nm 2014

10nm 2016

4nm 2018

2nm 2020

Things went a little off the rails with 14nm, which was about six months late. 10nm was nominally delivered in 2018 (two years late), but given that Rocket Lake, released earlier this year, used 14nm, I don't think you can really claim that 10nm was fully there prior to this year. Intel now plans to deliver a new process every year, but the changes between are smaller, so that's similar to their previous goal of a new process every two years. So you add five years to the original tick-tock road map, giving:

10nm 2021

4nm 2023

2nm 2025

That's ambitious. Time will tell whether they can pull it off.

mode_13h - Monday, July 26, 2021 - link

I'd give them 10 nm in 2019. Volumes were low, but Ice Lake was a real product (unlike Canon Lake). 10 nm SF reached comparable volumes in 2020.