The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTThe Future of Lakefield

Lakefield as a product is a lateral move for Intel. The company is taking some of its new and popular IP, and placing it into a novel form factor that has required a significant amount of R&D from a manufacturing and construction perspective. The goal of Lakefield was to meet particular customer requirements, which we understand to be around battery life, performance, and multi-screen support, and according to Intel, those goals have been met, and they will be producing future generations of Lakefield products.

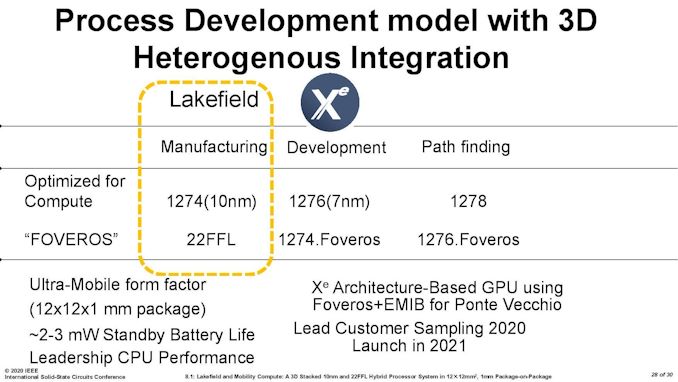

In particular, Intel has produced this slide at a couple of conferences.

This slide essentially states that Lakefield product in the yellow box has two silicon die – one optimized for compute on Intel’s P1274 process (10+ nm) and the Foveros layer (the active interposer layer) on Intel’s 22FFL process.

The next product with heterogeneous manufacturing integration will be Intel’s big Xe-HPC product, Ponte Vecchio, which will use Intel’s P1276 process (7nm) as a compute die and Intel’s P1274 (10+) process as a base interposer layer.

Beyond this, Intel looks to continue with its multi-layered products by having the compute layer on the most advanced process node, with the interposer layer one generation behind, on a ‘Foveros’ optimized variant.

So the first generation Lakefield is essentially a product that combines P1274 and 22FFL, and a future product is likely to be built on P1276 on the compute layer and P1274 for the interposer layer. Keeping this sort of cadence makes a lot of sense. However, Intel is going to have to learn from Lakefield in a number of ways, especially as we look at ways in which the heterogeneous layering concept can expand. I’ve split this into several areas that I feel is critical to where layered processors can really make a difference.

Growing a Stacked Die to Higher TDP and Core Count

I’ve combined these two points because they essentially go together. Implementing two simple silicon die together in a small form factor product, while is interesting on the power side of the equation, doesn’t probe the question of scaling the product up. It’s easy enough to scale the product out by adding in some form of connectivity to the stack and then connecting them together (which is what’s happening in Ponte Vecchio), but at some point the stack has to move to a higher level of power consumption if it wants to move upwards in power.

This means that thermals become a bigger issue if it wasn’t already. If we take the current Lakefield design, with one compute die over an active interposer, with the right routing then moving to a physically larger floorplan and a higher power shouldn’t be too much of an issue – if anything, making the base die larger should help spread a lot of that IO about, making the interposer a functionally less active interposer. Or Intel will implement the next generation of its die-to-die stacking technology, where the top dies can be larger than the base dies, in a cantilevered fashion.

The bigger deal with the thermals is going to be on the top, with the stacked PoP memory. We go more into the memory communications aspect in a bit, but ideally that memory needs to be on the side so the compute die can have access to a proper heatspreader. The only reason it is stacked in Lakefield is because of the size constraints and attempting to get everything into that small form factor. For anything larger, there needs to be a memory controller that looks outside the chip, which is kind of what we’re expecting from Ponte Vecchio with HBM. A desktop-class product would likely be in the middle.

Growing a Stacked Die to More Stacks

The other angle for a stacked silicon product is to put more stacks in place. This again brings about the question on cooling between the stacks, depending on what is actually there. Lakefield is only two stacks right now, with one high-powered stack and one low-powered stack. Intel would have to prove that it could manage multiple high-powered stacks in order to expand compute in the vertical dimension, but that brings about its own problems.

To start, with Lakefield, the main power to the top compute die is provided with TSVs going through the active interposer layer. For each compute die in a multi-die stack, there would have to be TSVs for each one in order to provide individual power. Unless the active interposer also acted as a PMIC, this could become difficult depending on what other TSVs or data paths need to be put in place between the layers.

Note, when we spoke with Intel’s Ramune Nagisetty at IEDM last year, when asked if Intel would ever discuss if a stacked product would use ‘dummy’ layers to help in cooling, we were told that this would unlikely be mentioned, focusing only on the layers that actually do any work. But ultimately there could be cause for dummy layers to aid in cooling, such that they can provide mass and distance between thermal hotspots between compute dies involved. As the number of layers increases, however, something like Lakefield would have to move the PoP memory off the top, as already mentioned.

Memory Communications

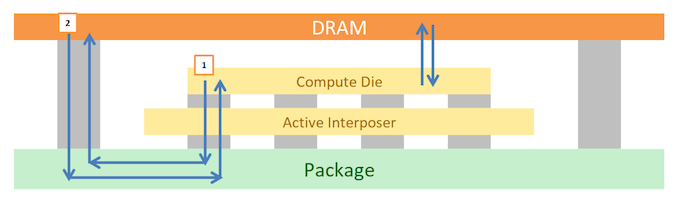

One element to the Lakefield design we haven’t really covered here is how the memory communicates. In the current Lakefield design, the compute cores and the memory controllers are located on the compute die. In order for a portion of main memory to be read into the compute die, the communication has to travel down through the active interposer, go into the package, and then loop back up to the stacked memory.

In the following diagram, on the left, we have (1) going from Compute Die to DRAM, and (2) DRAM back to Compute Die.

This path is a lot longer than simply going from the compute die straight up into the memory, which would be theoretical on the right hand side if the two were bonded and had appropriate pathways.

If a future Lakefield product wants to continue down the memory-on-top route, one optimization could be to bond that top memory die in a Foveros-like fashion. One could argue that it means Intel would have to bond the memory on at the manufacturing stage, but this already happens with the current generation of Lakefield designs. The only downside would be getting the bonding pads on the top of the compute die and the bottom of the memory die to line up, and then manage the communications from there. The power for the memory would have to also come through on TSVs.

But if we’re bonding the memory into the stack, then technically it could go at any layer – there are likely benefits to keeping the compute die/dies on top. This could lead to multiple layers of memory as needed.

Power Management

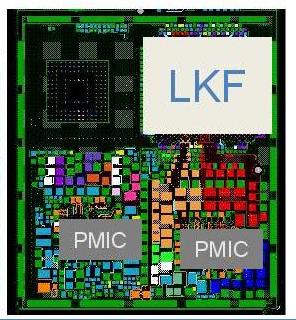

With the current Lakefield design, both the compute die and the active interposer die have their own power management IC (PMICs) in order to help deliver power. Based on Intel’s own diagrams, these PMIC designs take up more physical PCB space than Lakefield itself.

At some level, Intel is going to have to figure out to create a unified PMIC solution to cover every layer on the product. It likely reduces board space and would make things a lot simpler, as it does with laptops that can manage power to the CPU and GPU on the same die with an onboard power controller. A PMIC that can scale with layer counts is obviously going to be a plus.

Cooling

Through all of this, as I’ve mentioned several times, cooling is going to be a major concern. There’s no easy way around the physics of dissipating 5-10 W in such a small space, or over 100 W if the product scales up into something in a form factor that has a wider appeal. Previously in the article I mentioned that we had discussed this with Intel, and how areas such as microfluidic channels have obviously had some research put into, but nothing to the point where it could be done commercially and at scale. It’s a paradigm worth solving, because the benefits would be tremendous.

Beyond Windows and Enabling 5G

One thing to note is that Intel's Lakefield is only planned with Windows 10 support right now. Linux is currently not in the plan for this product, but it would have to be if Intel wants wider adoption of the technology.

Not only this, but as most people are comparing these devices to Qualcomm's hardware, appropriate 5G support will need to be applied - the current generation Lakefield is not part of Intel and Mediatek's collaboration on 5G, which only applies to Tiger Lake and beyond. Lakefield customers will have to rely on 4G as an optional extra, or 5G through an external modem.

The Future Of Lakefield

Even if this first generation version of Lakefield gets slammed pretty hard in performance-focused benchmark reviews for being slower than a dual-core Whiskey Lake, Lakefield marks some very big steps for Intel. Hybrid CPU designs, and stacked die-to-die connectivity, are going to feature in Intel’s future roadmaps – at what points will depend on how much Intel is willing to experiment but also how well Intel can execute. There have been discussions on Intel perhaps looking at an 8+8 hybrid CPU design in the future, although nothing we can substantiate, but we do know that Ponte Vecchio with stacked die is coming in late 2021.

One of the key ingredients in all of this is going to be at what points Intel’s technology portfolio is going to intersect its product portfolio. Some of these technologies might find their way better suited to aspects such as 5G networking, or automotive, rather than something we can consume on the desktop. As far as Lakefield goes, this first generation is going to be a rough challenge for Intel – they are pitching a low performance product in a high-cost segment based on technology (and to a certain extent, battery life). Die-to-die stacking will get easier to do as scale ramps, and hopefully new process node technologies will drive the power efficiency of those big cores lower to enable 2+4 or bigger designs when in a stacked form factor.

We eagerly await a chance to test 1st Gen Lakefield, but we’re also keeping an eye on what might be in the second and third generations.

221 Comments

View All Comments

EthiaW - Tuesday, July 7, 2020 - link

How can we expect something that stingy on silicon area (don't have place for a single more large core) to compete with a snapdragon 9cx (likely with two Cortex-X1)or apple a14? Actually it has no edge over apple a12 from 2018 even the latter faces some 40% performance lost in x86 simulation.Wilco1 - Wednesday, July 8, 2020 - link

It doesn't even compete with the 18 month old 8cx... It will be interesting to see a side by side Book S review with benchmarks and battery life.serendip - Tuesday, July 14, 2020 - link

https://www.notebookcheck.net/Samsung-Galaxy-Book-...Here it is. It barely competes against the 8cx but gets almost half the battery life running at 5W TDP. Samsung is supposed to release an update to allow running at 7W but that would kill battery life even more.

Wilco1 - Wednesday, July 15, 2020 - link

Ouch... Thanks for that link!reggjoo1 - Tuesday, July 7, 2020 - link

Just manipulating the scheduler, won't be enough. They're gonna have to work on the governor more.808Hilo - Sunday, July 12, 2020 - link

Headline:Intel expanded its turd business!

We successfully, and at great cost, replicated the Atom processor and are only 10 years late with our consumer grade chip. The improvements are amazing: 1 slow processor supported by 3 superslow processors in a revolutionary new 4 processor die. The chip, designed for warheads, is exclusively down binned and handselected for exacting consumer standards. Support our military. Desining low performance is not cheap. Getting effed - Intel inside!

throAU - Monday, July 13, 2020 - link

So, unless this can compete with the iPad Pro processor of the day, I just don't see the market. Windows 10 on ultra portable tablet type devices already sucks. So your realistic choices are android and iOS. Android has a suite of decently performing, already existent SOCs on the market, likely at far less cost than intel will no doubt try to charge for this. And no AVX-512? Only a single performance core? I just don't see it working out.I would have thought they'd be far better off not neutering the Sunny Cove core, and working with Microsoft/others on an API for workload queuing to the relevant core for a relevant code fragment. Treat the performance core as you would any other co-processor. Use thread affinity to bind specific UI threads to it. I'm sure there are methods that could be used but no - in order to run on unmodified platforms (that suck for the market segment they are aiming at anyway) - they crippled it.

serendip - Tuesday, July 14, 2020 - link

Notebookcheck has a review comparing the Intel Lakefield and ARM models of the Galaxy Book S:mhttps://www.notebookcheck.net/Samsung-Galaxy-Book-...The results aren't pretty. For the same price of around $1000, the Lakefield version loses LTE in some markets, has equal or slightly less performance for CPU and GPU, but it has <10 hour battery life compared to the 8cx model's 16 hours. Despite all the fancy packaging, Lakefield is still half as efficient as Qualcomm's best, which makes it outclassed by Apple's silicon.

The worst part about Lakefield on Windows is how it essentially performs as a quad core Atom chip most of the time. Ian's fears were realized.

throAU - Tuesday, July 14, 2020 - link

This is pretty much exactly what I expected. Except the modern ARM processors have a better feature set than a crippled Lakefield chip. And there's less fragmentation in what they will/will not support vs. other ARM processors of the day.I expected Qualcomm to outclass it. It won't even be anywhere near close an A12Z and that's a processor from 12-18 months ago, which will no doubt be outclassed itself by whatever apple release late this year.

ballsystemlord - Wednesday, July 22, 2020 - link

Spelling and grammar errors:"For those that are interested, Lakefield's PMICs are under the codenames Warren Cove and Castro Cover, and were developed in 2017-2018."

I think you misspelled "cove":

"For those that are interested, Lakefield's PMICs are under the codenames Warren Cove and Castro Cove, and were developed in 2017-2018."

"Even those these CPUs are a 1+4 configuration,..."

"though" not "those":

"Even though these CPUs are a 1+4 configuration,..."

"Another thing to note, which Intel glossed over, that most people are going to be really concerned about."

Missing "is" and concerned about what?

"Another thing to note, which Intel glossed over, is that most people are going to be really concerned about."