The AMD 3rd Gen Ryzen Deep Dive Review: 3700X and 3900X Raising The Bar

by Andrei Frumusanu & Gavin Bonshor on July 7, 2019 9:00 AM ESTSection by Gavin Bonshor

X570 Motherboards: PCIe 4.0 For Everybody

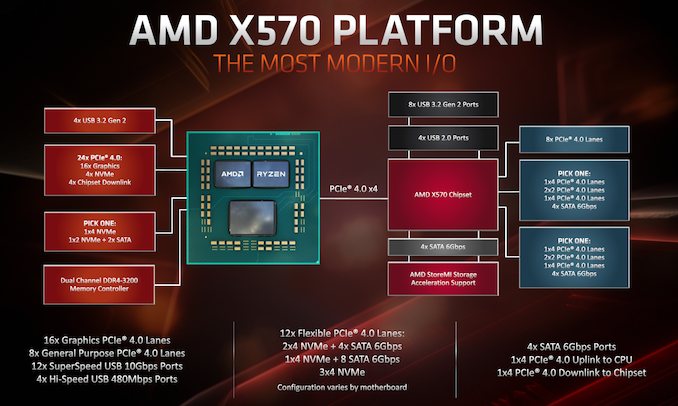

One of the biggest additions to AMD's AM4 socket is the introduction of the PCIe 4.0 interface. The new generation of X570 motherboards marks the first consumer motherboard chipset to feature PCIe 4.0 natively, which looks to offer users looking for even faster storage, and potentially better bandwidth for next-generation graphics cards over previous iterations of the current GPU architecture. We know that the Zen 2 processors have implemented the new TSMC 7nm manufacturing process with double the L3 cache compared with Zen 1. This new centrally focused IO chiplet is there regardless of the core count and uses the Infinity Fabric interconnect; the AMD X570 chipset uses four PCIe 4.0 lanes to uplink and downlink to the CPU IO die.

Looking at a direct comparison between AMD's AM4 X series chipsets, the X570 chipset adds PCIe 4.0 lanes over the previous X470 and X370's reliance on PCIe 3.0. A big plus point to the new X570 chipset is more support for USB 3.1 Gen2 with AMD allowing motherboard manufacturers to play with 12 flexible PCIe 4.0 lanes and implement features how they wish. This includes 8 x PCIe 4.0 lanes, with two blocks of PCIe 4.0 x4 to play with which vendors can add SATA, PCIe 4.0 x1 slots, and even support for 3 x PCIe 4.0 NVMe M.2 slots.

| AMD X570, X470 and X370 Chipset Comparison | |||

| Feature | X570 | X470 | X370 |

| PCIe Interface (to peripherals) | 4.0 | 2.0 | 2.0 |

| Max PCH PCIe Lanes | 24 | 24 | 24 |

| USB 3.1 Gen2 | 8 | 2 | 2 |

| Max USB 3.1 (Gen2/Gen1) | 8/4 | 2/6 | 2/6 |

| DDR4 Support | 3200 | 2933 | 2667 |

| Max SATA Ports | 8 | 8 | 8 |

| PCIe GPU Config | x16 x8/x8 x8/x8/x8* |

x16 x8/x8 x8/x8/x4 |

x16 x8/x8 x8/x8/x4 |

| Memory Channels (Dual) | 2/2 | 2/2 | 2/2 |

| Integrated 802.11ac WiFi MAC | N | N | N |

| Chipset TDP | 11W | 4.8W | 6.8W |

| Overclocking Support | Y | Y | Y |

| XFR2/PB2 Support | Y | Y | N |

One of the biggest changes in the chipset is within its architecture. The X570 chipset is the first Ryzen chipset to be manufactured and designed in-house by AMD, with some helping ASMedia IP blocks, whereas previously with the X470 and X370 chipsets, ASMedia directly developed and produced it using a 55nm process. While going from X370 at 6.8 W TDP at maximum load, X470 was improved upon in terms of power consumption to a lower TDP of 4.8 W. For X570, this has increased massively to an 11 W TDP which causes most vendors to now require small active cooling of the new chip.

Another major change due to the increased power consumption of the X570 chipset when compared to X470 and X370 is the cooling required. All but one of the launched product stack features an actively cooled chipset heatsink which is needed due to the increased power draw when using PCIe 4.0 due to the more complex implementation requirements over PCIe 3.0. While it is expected AMD will work on improving the TDP on future generations when using PCIe 4.0, it's forced manufacturers to implement more premium and more effective ways of keeping componentry on X570 cooler.

This also stretches to the power delivery, as AMD announced that a 16-core desktop Ryzen 3950X processor is set to launch later on in the year, meaning motherboard manufacturers needed to implement the new power deliveries on the new X570 boards with requirements of the high-end chip in mind, with better heatsinks capable of keeping the 105 W TDP processors efficient.

Memory support has also been improved with a seemingly better IMC on the Ryzen 3000 line-up when compared against the Ryzen 2000 and 1000 series of processors. Some motherboard vendors are advertising speeds of up to DDR4-4400 which until X570, was unheard of. X570 also marks a jump up to DDR4-3200 up from DDR4-2933 on X470, and DDR4-2667 on X370. As we investigated in our Ryzen 7 Memory Scaling piece back in 2017, we found out that the Infinity Fabric Interconnect scales well with frequency, and it is something that we will be analyzing once we get the launch of X570 out of the way, and potentially allow motherboard vendors to work on their infant firmware for AMD's new 7nm silicon.

447 Comments

View All Comments

shakazulu667 - Sunday, July 7, 2019 - link

Is there a compilation test coming for chromium or another big source tree, that would show if new IO arch brings wider benefits for such CPU+IO workloads?Andrei Frumusanu - Sunday, July 7, 2019 - link

We'll be re-adding the Chromium compile test in the next few days - there were a few technical hiccups when running it.shakazulu667 - Sunday, July 7, 2019 - link

Thanks, I'm looking forward to it, especially curious if AMD can utilize NVMe better for this kind of workload.Andrei Frumusanu - Sunday, July 7, 2019 - link

Unfortunately we don't test the CPU suite with different SSDs for this.shakazulu667 - Sunday, July 7, 2019 - link

Is there another test in your suite that could show improvements with IO , incl NVMe?RSAUser - Monday, July 8, 2019 - link

But one of the big features is PCIe 4 support, so testing with an nvme drive as well to show difference would be important? People spending $490 on a CPU only are probably going to be buying an Nvme SSD.A5 - Monday, July 8, 2019 - link

There aren't any PCIe 4 SSDs for them to test with.0ldman79 - Monday, July 8, 2019 - link

Yep, PCIe 4.0 NVME is going to be beta at this point at best.Last I read the first 4.0 NVME to be released is essentially running an overclocked 3.0 interface, which the list of NVME that can saturate 3.0 is pretty short as it is.

RSAUser - Tuesday, July 9, 2019 - link

That's because these are the first PCIe 4 slots that exist, can't release a product that can't even be used.Using an overlocked drive in lieu of a 4 one is the proper thing to do.

Kevin G - Tuesday, July 9, 2019 - link

For consumers yes but the first PCIe 4.0 host system was the IBM POWER9 released ~18 months ago. As such there are a handful of NIC and accelerators for servers out there today.The real oddity is that nVidia doesn’t support PCIe 4.0. Volta’s nvLink has a PHY based upon PCIe 4.0. Turing should as well though nVidia doesn’t par those chips with the previously mentioned POWER9.