AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome

by Dr. Ian Cutress on June 10, 2019 7:22 PM EST- Posted in

- CPUs

- AMD

- Ryzen

- EPYC

- Infinity Fabric

- PCIe 4.0

- Zen 2

- Rome

- Ryzen 3000

- Ryzen 3rd Gen

Fetch/Prefetch

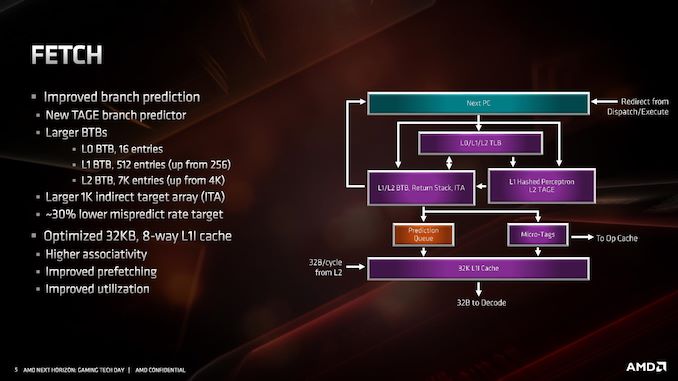

Starting with the front end of the processor, the prefetchers.

AMD’s primary advertised improvement here is the use of a TAGE predictor, although it is only used for non-L1 fetches. This might not sound too impressive: AMD is still using a hashed perceptron prefetch engine for L1 fetches, which is going to be as many fetches as possible, but the TAGE L2 branch predictor uses additional tagging to enable longer branch histories for better prediction pathways. This becomes more important for the L2 prefetches and beyond, with the hashed perceptron preferred for short prefetches in the L1 based on power.

In the front end we also get larger BTBs, to help keep track of instruction branches and cache requests. The L1 BTB has doubled in size from 256 entry to 512 entry, and the L2 is almost doubled to 7K from 4K. The L0 BTB stays at 16 entries, but the Indirect target array goes up to 1K entries. Overall, these changes according to AMD affords a 30% lower mispredict rate, saving power.

One other major change is the L1 instruction cache. We noted that it is smaller for Zen 2: only 32 KB rather than 64 KB, however the associativity has doubled, from 4-way to 8-way. Given the way a cache works, these two effects ultimately don’t cancel each other out, however the 32 KB L1-I cache should be more power efficient, and experience higher utilization. The L1-I cache hasn’t just decreased in isolation – one of the benefits of reducing the size of the I-cache is that it has allowed AMD to double the size of the micro-op cache. These two structures are next to each other inside the core, and so even at 7nm we have an instance of space limitations causing a trade-off between structures within a core. AMD stated that this configuration, the smaller L1 with the larger micro-op cache, ended up being better in more of the scenarios it tested.

216 Comments

View All Comments

stance_changer - Sunday, June 23, 2019 - link

Does IF use PCI E? I thought it used the wiring in 2p epyc systems, and IIRC PCI E doesn't double the bus width every gen, but I would love to be proven wrong.SlitheryDee - Friday, June 28, 2019 - link

I've been using intel for a few years now, but I must say I can't describe how much I love what AMD is doing these days. I go where the performance per dollar is generally, so the best complement I can pay them is to say my next upgrade will be based on an AMD chip.SlyNine - Sunday, July 7, 2019 - link

So, what time exactly do these new cpus launch. I mean. The hour.Dodozoid - Sunday, July 7, 2019 - link

Yeah, I was also trying to find that information with no success.Do the reviewers know already or are they waiting for a release instruction from AMD?

ilux.merks - Sunday, July 7, 2019 - link

What nobody is talking about is how are the fixes for meltdown and spectre on these new amd processors?Korguz - Sunday, July 7, 2019 - link

simple.. they dont exist, from what i have seen.. those issues.....are intels only ...