AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome

by Dr. Ian Cutress on June 10, 2019 7:22 PM EST- Posted in

- CPUs

- AMD

- Ryzen

- EPYC

- Infinity Fabric

- PCIe 4.0

- Zen 2

- Rome

- Ryzen 3000

- Ryzen 3rd Gen

Integer Units, Load and Store

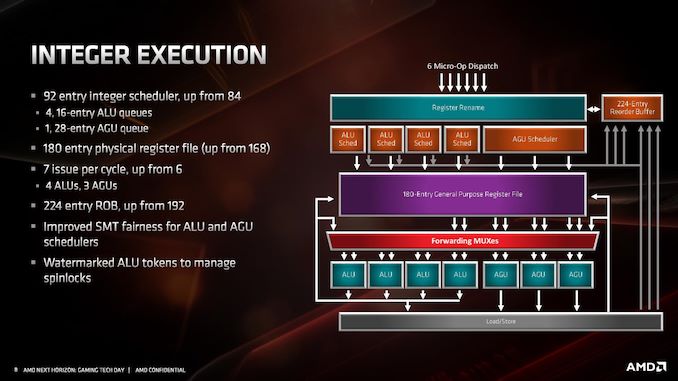

The integer unit schedulers can accept up to six micro-ops per cycle, which feed into the 224-entry reorder buffer (up from 192). The Integer unit technically has seven execution ports, comprised of four ALUs (arithmetic logic units) and three AGUs (address generation units).

The schedulers comprise of four 16-entry ALU queues and one 28-entry AGU queue, although the AGU unit can feed 3 micro-ops per cycle into the register file. The AGU queue has increased in size based on AMD’s simulations of instruction distributions in common software. These queues feed into the 180-entry general purpose register file (up from 168), but also keep track of specific ALU operations to prevent potential halting operations.

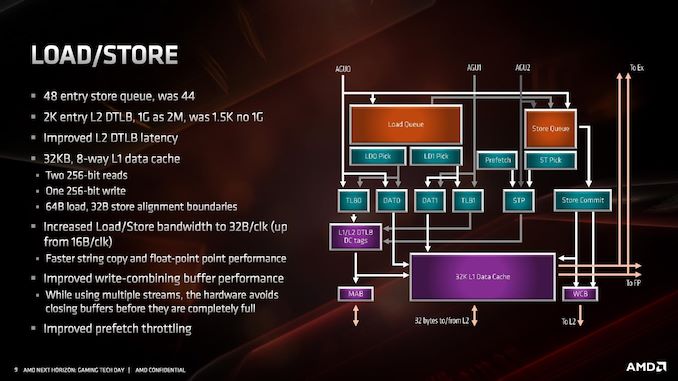

The three AGUs feed into the load/store unit that can support two 256-bit reads and one 256-bit write per cycle. Not all the three AGUs are equal, judging by the diagram above: AGU2 can only manage stores, whereas AGU0 and AGU1 can do both loads and stores.

The store queue has increased from 44 to 48 entries, and the TLBs for the data cache have also increased. The key metric here though is the load/store bandwidth, as the core can now support 32 bytes per clock, up from 16.

216 Comments

View All Comments

Thunder 57 - Sunday, June 16, 2019 - link

It appears they traded half the L1 instruction cache to double the uop cache. They doubled the associativity to keep the same hit rate but it will hold fewer instructions. However, the micro-op cache holds already decoded instructions and if there is a hit there it saves a few stages in the pipeline for decoding, which saves power and increases performance.phoenix_rizzen - Tuesday, June 11, 2019 - link

From the article:"Zen 2 will offer greater than a >1.25x performance gain at the same power,"

I don't think that means what you meant. :) 1.25x gain would be 225% or over 2x the performance. I think you meant either:

"Zen 2 will offer greater than a 25% performance gain at the same power,"

or maybe:

"Zen 2 will offer greater than 125% performance at the same power,"

or possibly:

"Zen 2 will offer greater than 1.25x performance at the same power,"

phoenix_rizzen - Tuesday, June 11, 2019 - link

From the article:"With Matisse staying in the AM4 socket, and Rome in the EPYC socket,"

The server socket name is SP3, not EPYC, so this should read:

"With Matisse staying in the AM4 socket, and Rome in the SP3 socket,"

phoenix_rizzen - Tuesday, June 11, 2019 - link

From the article:"This also becomes somewhat complicated for single core chiplet and dual core chiplet processors,"

core is superfluous here. The chiplets are up to 8-core. You probably mean "single chiplet and dual chiplet processors".

scineram - Wednesday, June 12, 2019 - link

No, becausethere is no single chiplet. It is the core chiplet that is either 1 or 2 in number.phoenix_rizzen - Tuesday, June 11, 2019 - link

From the article:"all of this also needs to be taken into consideration as provide the optimal path for signaling"

"as" should be "to"

thesavvymage - Wednesday, June 12, 2019 - link

A 1.25x gain is the exact same as a 25% performance gain, it doesnt meant 225% as you stateddsplover - Tuesday, June 11, 2019 - link

So in other words Anadtech no longer receives engineering samples but tells us what everyone else is saying.Still love coming here as reviews are good, but boy oh boy yuze guys sure slipped down the ladder.

Bring back Anand Shimpli.

Korguz - Wednesday, June 12, 2019 - link

the do still get engineering samples... but usually cpus...not likely.. hes working for apple now....

coburn_c - Wednesday, June 12, 2019 - link

What the heck is UEFI CPPC2?