Samsung and TSMC Roadmaps: 8 and 6 nm Added, Looking at 22ULP and 12FFC

by Anton Shilov on May 5, 2017 9:30 AM ESTBeyond 10 nm at Samsung: 8 nm and 6 nm

Samsung’s 7 nm manufacturing technology is still expected to be the company’s first process to use extreme ultraviolet lithography (EUVL) for high-volume manufacturing (HVM) and that is going to happen sometimes in 2019 or later (risk production starts in the second half of 2018). In fact, the next several years down the road is where things will start to get interesting as Samsung announced another two new production technologies it has not talked about before: the 8 nm and the 6 nm processes.

| Industry FinFET Lithography Roadmap, HVM Start Data announced by companies during conference calls, press briefings and in press releases |

||||||||||||

| 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | |||||||

| 1H | 2H | 1H | 2H | 1H | 2H | 1H | 2H | |||||

| GlobalFoundries | 14LPP | 7nm DUV | 7nm with EUV* | |||||||||

| Intel | 14 nm 14 nm+ |

14 nm++ 10 nm |

10 nm+ 10 nm++ |

|||||||||

| Samsung | 14LPP 14LPC |

10LPE | 10LPP | 8LPP 10LPU |

7LPP | 6 nm* (?) | ||||||

| SMIC | 28 nm** | 14 nm in development | ||||||||||

| TSMC | CLN16FF+ CLN16FFC | CLN10FF CLN16FFC |

CLN7FF CLN12FFC |

CLN12FFC/ CLN12ULP |

CLN7FF+ | 5 nm* (?) | ||||||

| UMC | 28 nm** | 14nm | no data | |||||||||

| *Exact timing not announced **Planar |

||||||||||||

Officially, Samsung says that both technologies will offer “greater scalability, performance and power advantages when compared to existing process nodes,” which obviously means that they are across the board better than Samsung’s current-gen 14 nm and 10 nm offerings. What is important is that Samsung also says that the “8 nm and the 6 nm will inherit all innovations from the latest 10 nm and the 7 nm technologies” respectively. This means that the 8 nm is set to keep using DUV and multi patterning (triple patterning or even quad patterning to be exact, but Samsung has not confirmed usage of the latter) for critical layers, whereas the 6 nm will come after 7 nm and will be Samsung’s second-generation EUV technology.

The only thing that Samsung confirms about its 8LPP manufacturing technology right now is the fact that this is a DUV-based process technology designed to shrink die size (i.e., increase transistor density) and frequency compared to the 10LPP fabrication process. Given the name of the technology and its key advertised advantages over direct predecessor, it is highly likely that the 8LPP will be used to make high-performance SoCs in 2019.

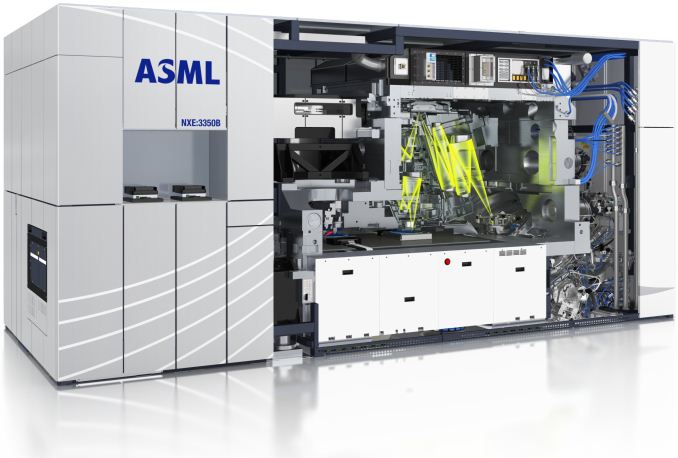

Since Samsung plans to start risk production using the 7LPP in the second half of 2018, the technology is hardly going to be used for high-volume manufacturing before the second half of 2019. Keeping in mind that Samsung now begins HVM using its leading-edge process technologies in October, it is possible that it is going to kick-off 7LPP HVM in fall 2019, but the 8LPP will be Samsung’s most advanced process technology for the better part of the year. Samsung does not mention timeframes for its 6 nm process technology and what to expect from it, but it is logical to assume that it will require more layers to be processed using ASML's EUV tools (like the NXE:3350B pictured above) in a bid to provide PPA advantages and it not be used for high-volume manufacturing before late 2020.

In March, Samsung only made brief announcements regarding its 10LPU, 8LPP and 6 nm process technology without disclosing their exact specifications or even PPA improvements targets. The addition of at least two more DUV technologies (the 10LPU and the 8LPP) in general may indicate that EUV may not be the best choice for all applications in 2019 – 2021, which is perfectly logical. Then again, we do not know how DUV and EUV technologies will co-exist early in the EUV era.

We are going to learn more about Samsung’s plans in the foundry industry in late May, when the company hosts its 2017 U.S Samsung Foundry Forum. So, we will have to wait for a couple of months for Samsung to disclose the whole picture regarding its upcoming process technologies.

89 Comments

View All Comments

Lodix - Friday, May 5, 2017 - link

Samsung's 10nmLPP has a 15% reduction in power consumption compared to the LPE version.Also the 10nmLPE numbers about performance and power 27/40% are compared to the previous 14nmLPE not the Plus version.

Lodix - Friday, May 5, 2017 - link

And the 10nmLPU version is aimed to Area reduction.Anton Shilov - Friday, May 5, 2017 - link

Thank you for the corrections. You are right about the 10LPP, they made and appropriate announcement a couple of weeks ago, but somehow I've missed it. Fixed.Regarding the 10LPE vs 14LP*, I am not sure.

They state the following:

"Samsung’s new 10nm FinFET process (10LPE) adopts an advanced 3D transistor structure with additional enhancements in both process technology and design enablement compared to its 14nm predecessor, allowing up to 30-percent increase in area efficiency with 27-percent higher performance or 40-percent lower power consumption."

http://www.anandtech.com/show/10765/samsung-10nm-m...

If you look at the picture there (http://images.anandtech.com/doci/10765/dac.png), they mention ~30% performance increase at the same leakage power, which can considered as 27%... But if you happen to see some more up to date slides from Samsung, please link them.

As for the 10LPU, I guess, they are going to make an announcement in late May.

Lodix - Friday, May 5, 2017 - link

I see the arrow joining the 14nmLPE version with 10nmLPE.Lodix - Saturday, May 6, 2017 - link

In this pdf from Samsung they specified that the improvements stated are from 14nmLPE and not from 14nmLPP.https://www.semiwiki.com/forum/attachments/f293/18...

MajGenRelativity - Friday, May 5, 2017 - link

I know AMD will be using GF 7nm for their GPUs after Vega 10/11, but I wonder what NVIDIA will be using after this current Pascal generation. Does anyone have any clues?haukionkannel - Friday, May 5, 2017 - link

If They Are vice They use at least two different distributors just like Apple.melgross - Saturday, May 6, 2017 - link

Apple has moved away from that model. I doubt they wanted to do it, but neither Samsung nor TSMC could produce all the SoCs they needed that year, so they had to.It's also interesting to note that while Apple had to tune their designs to both processes, the TSMC 16nm was 20% more efficient than the Samsung 14nm process. We saw results of those tests either here or on arstechnica, I don't remember which now. But the total device efficiency advantage was under 5% once everything was taken together.

But still, it shows that we can't go by theory when extrapolating these supposed numbers to the real world. I'd still rather see Apple on intel.

The_Assimilator - Friday, May 5, 2017 - link

I would be extremely surprised if it was anyone except TSMC. Especially since TSMC has just announced 10nm is ready for H2 this year - which, not coincidentally, is when NVIDIA is rumoured to drop the first Volta products.The only GPU that NVIDIA has ever sourced from a company other than TSMC is GP107 from Samsung at 14nm. Even though Sammy's 14nm node is worse than TSMC's 16nm, GP107 is such a (relatively) small and simple chip that it didn't really matter. We'll probably see a similar story with Volta: TSMC gets the big Pascals, Samsung gets the small ones.

There is, of course, always the possibility that NVIDIA will stick with the now-mature (and cheaper) 16nm for Volta - I imagine it will depend on whether Volta is more (10nm) or less (16nm) powerful clock-for-clock compared to Pascal.

Kevin G - Sunday, May 7, 2017 - link

nVidia has been flirting with Samsung of late. I doubt they'd just exclusively to Samsung but they'll likely continue to have small/medium chip there as a testing vehicle if they need to quickly switch their entire line up over.