AnandTech Year in Review 2018: CPUs

by Ian Cutress on December 27, 2018 3:30 PM ESTAnandTech Year in Review 2018: CPUs

October: Announcements

The start of Q4 always comes with new vigor. It’s around this time we start to see product announcements for the end-of-the-year, or the ‘holiday’ period. For some companies this can mark the biggest volume of sales all year, so it’s important to get it right. Intel came out all guns blazing with its Fall PC Desktop Event.

The big announcement was that the 9th Generation Core CPUs would be coming to market, although with no microarchitecture changes. Intel used the event to announce the Core i9-9900K, the new flagship processor with eight cores, and using solder between the core and the heatspreader rather than paste to improve thermal performance. The fact that this is an 8-core means that Intel is matching the best high-end desktop processor from only a couple of years before. The 9900K was also announced with the i7-9700K and the i5-9600K, showing that Intel is moving away from Hyperthreading for most of its desktop processor line in order to keep some performance separation between the family of parts. We reviewed the processors later in the month when the embargo lifted, showing Intel’s new halo consumer processor is certainly the Core i9-9900K. These processors also have several of the Spectre/Meltdown hardware mitigations, which we also compared to the previous family to show that despite the fixes being in hardware, the performance clock-for-clock is the same.

Also at the event Intel announced a refresh of the high-end desktop platform, the major difference being that these parts will also be soldered, along with some cache updates for the lower down members of the stack. The new halo part, the Core i9-9980XE, had a 15% base frequency gain over the part it was replacing, with Intel going after the 32-core competition by offering better per-core performance in most benchmarks.

We also got some new information about that unlocked 28-core high-end desktop processor that Intel showed at Computex. Intel will be naming it the Xeon W-3175X. Out of the box the processor would have a base frequency of 3.1 GHz, a peak turbo frequency of 4.3 GHz, and a TDP of 255W. The socket, LGA3647, means that special motherboards designed for the consumer market will be needed. At present, it looks like ASUS and GIGABYTE will both be producing one board each. Pricing was not disclosed, however Intel said it would be available by the end of the year. As it is now the end of December, we expect to see it January.

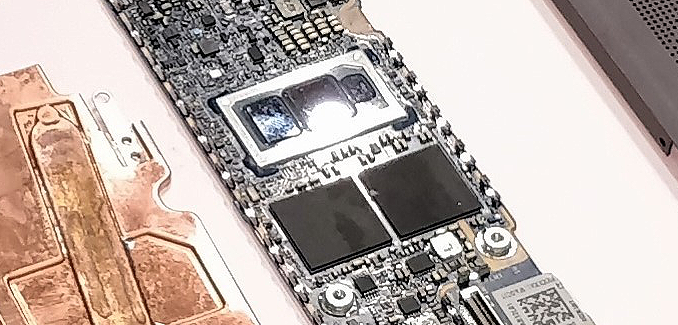

Aside from the Fall PC event, we also saw something interesting from Intel and HP. The new HP Spectre Folio for Q4 was listed with an Amber Lake-Y processor however on a breakdown of the hardware with PC World, it was noticed that the CPU package has three dies on it rather than two. Normally we expect to see a CPU and a chipset, so this third package was a mystery. Initially it was decided that this was the LTE modem that HP was using to make the package have wireless connectivity, and this seemed to be confirmed, however Intel threw that idea under the bus but refused to say exactly what it was. This is still somewhat of a mystery.

Image via PC World

Aside from the review of Intel’s 9th Generation Core processors, we also saw the launch of two more AMD Ryzen Threadripper parts – this time the 24-core 2970WX and the 12-core 2920X. These processors were not as exciting as the previous review, and mirrored a lot of the characteristics of the 32-core and 16-core just at lower price points. The 24-core excelled at rendering, but often regressed in other benchmarks due to its bifurcated memory strategy. The 12-core is a good allrounder, but the 16-core processor still stands out.

During this month we also posted a review about managing Threadripper’s Core 0 on the 2990WX. We were tipped off by Wendell at Level1Techs, who saw that managing Core 0 gave him an increase in performance in certain tasks because of the bifurcated memory setup. We went through our benchmark suite to see the difference – we did see a 20% bump in results in LuxMark, but most tests were equal or down 10%, overall making it a worse performing chip.

To end the month, AMD did a thing with an old microarchitecture. We saw the company launch a new FM2+ Carrizo APU, the A8-7680. We’re pretty sure this was due to a customer request to replace a chip already in a number of deployed systems.

November: Next Horizon and Supercomputing

One of the busiest months of the year was November. Not only did we have AMD’s Next Horizon event detailing 7nm, but also plenty of product launches as well as the Supercomputing trade show right in the middle of it all. It was this month I was destined to cart 20-30kg of hardware testing to be able to benchmark in hotels across the US.

Starting with Intel, November saw our Core i9-9900K review and Core i9-9980XE reviews go live, which I mentioned in the October section. We also published our review of Intel’s Xeon E six-core processors: the Xeon E-2186G, E-2176G, E-2146G, and E-2136. Xeon E is Intel’s enterprise/commercial versions of the mainstream processors, but different to vPro enabled parts as Xeon E is focused more for servers and datacenters rather than office machines. That being said, Xeon E is a relatively small portion of Intel’s market and revenue, but one they have to cater to.

We also published a report into what Intel means by its TDP metrics, how this plays into Turbo modes, and how consumer motherboard manufacturers don’t listen to any of it. This came about due to a number of reviewers getting different results in the 9900K review, given that the processor can peak above 170W during load even though Intel’s official TDP rating is 95W, and it’s peak power based on the specifications documents should be ~120W. I used the opportunity to describe what Intel means by a range of variables, including PL1, PL2, Tau, and everything in between. On the basis of this testing, we also published our analysis of when we fixed the 9900K to 95W, to see what the performance would be if the CPU was in a power limited scenario.

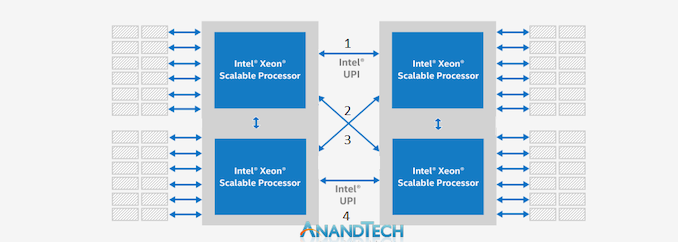

It was also during November that Intel announced it would be bolstering its Cascade Lake processor launch in 2019 with a new line of Cascade Lake-AP processors. These would be two 24-core silicon dies paired together over QPI links in a single package, offering 48 cores and 12 memory channels but limited to 2S deployments. At Supercomputing Intel gave some performance metrics it expected Cascade-AP to hit, and also confirmed the QPI layouts which confirm that what Intel is really doing is building a dense 4S system in two sockets. The company also said that the AP processors would be launched at the same time as the regular Cascade Lake parts.

It should also be noted that during Supercomputing, one of Intel’s partners disclosed the Cascade Lake launch window. That magic time is March to May 2019.

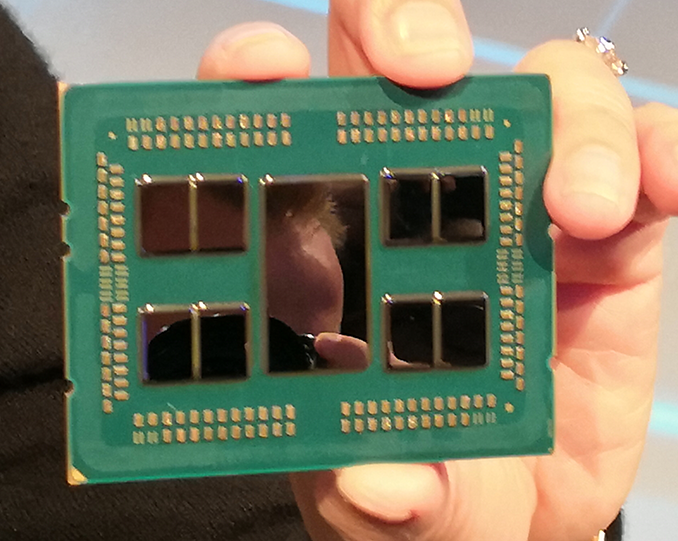

At AMD’s Next Horizon event, the company focused on its plans around 7nm. The highlight of the presentation was showing off the second generation AMD EPYC ‘Rome’ processor, with eight chiplets built on TSMC’s 7nm and a large 14nm IO die from GlobalFoundries. The processor is set to be socket compatible with current Naples systems, however new motherboards will be needed to take advantage of its PCIe 4.0 capabilities. The first products to use Rome’s PCIe 4.0 connectivity would be the Radeon Instinct accelerators that AMD also showed off at the event, powered by 7nm Vega. As part of the presentations, AMD also confirmed that alongside Zen 2 in 2019, and Zen 3 in 2020, it has already started process on the next generation after that: Zen 4.

At the event we had a chance to interview AMD’s CTO, Mark Papermaster, about the announcements. He confirmed where the chiplets would be made at TSMC for 7nm and GF for 14nm, that the new memory layout would offer better overall latency, and that the chiplets communicate with the IO die rather than directly with each other. It was also stated that Rome will remain price competitive in the market, and that the same socket will still be present in the generation of EPYC after Rome, called Milan. There were lots of specifics I asked that he said we would have to wait for the official announcement before they would lift the lid. Realistically, we expect Rome to come up for air sometime in the second half of 2019.

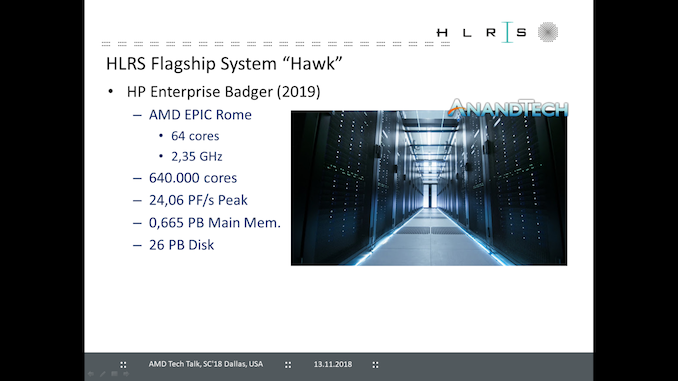

AMD had a few interesting moments at Supercomputing as well. We learned that they have scored some HPC design wins, such as being part of Cray’s Shasta system, but also being involved in a deployment at HLRS in Germany, where slides during a presentation stated a 2.35 GHz clock for 64 cores. The Shasta system is to be deployed at NERSC as part of its upcoming ‘Perlmutter’ supercomputer, slated for delivery in late 2020.

If that wasn’t enough, AMD officially launched a new EPYC 7371 processor as its fastest EPYC processor to date. This 16-core part was developed due to customer request, running at 3.6 GHz across all cores while still offering 128 PCIe 3.0 lanes and 8-channel memory. I want to get one in for review.

Supercomputing also had some other interesting CPU related news. We saw a system from GIGABYTE based on Qualcomm’s Centriq processors – the family of CPUs with no follow up and no roadmap. We were told that GIGABYTE is the only official vendor allowed to sell the systems on the market, and we’ve asked for a review sample when they are ready. We also saw Huawei advertise that they are using bigger server-focused cores in its new Hi1620 server processor, although details on exactly what were hard to come by.

December: New Technologies

Normally at this point we wind down for the year, and take some time to recuperate before CES in early January. No such luck: after attending Qualcomm’s Tech Summit where the company announced the Snapdragon 855 for 2019 flagship smartphones, and an interview with Qualcomm President Cristano Amon, it was straight to arguably Intel’s most anticipated press event in a long long time: Intel’s Architecture Day.

I want to put this event into context. Intel scheduled 4.5 hours of presentations from the senior engineers: Raja Koduri, Jim Keller, Ronak Singhal, to name a few. Murthy Renduchintala also made an appearance. The presentations finished at around 5:20pm with a couple of hours of networking. Rather than do that, Paul Alcorn from Tom’s Hardware and I took a taxi back to our hotel and starting writing the event up in order to make the 6am embargo the next morning. We ordered some food in, and I finished around 4am, 6000 words lighter, which gave me a couple of hours to pack and sleep before leaving for the airport. You can read the report into the Architecture Day in all its glory here.

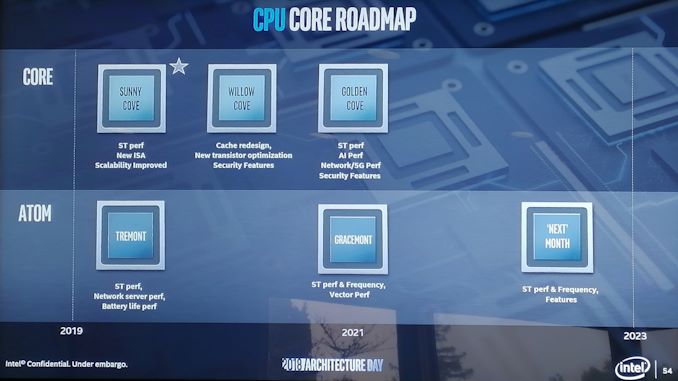

The cliff notes of the day are these: Intel gave us roadmaps. Intel hasn’t done that for consumer parts for what feels like years. For both Core and Atom, we were given names for the next two/three generations, as well as expected timeframes. The next generation Core microarchitecture will be called Sunny Cove, with Willow Cove and Golden Cove to follow. Sunny Cove will be on 10nm.

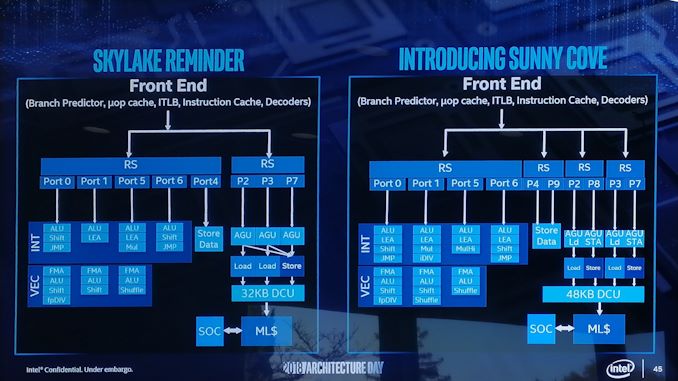

If that wasn’t all, Intel lifted the lid slightly on Sunny Cove’s microarchitecture. Technically they only discussed some of the back-end of the design, showing that the new part had AVX-512 units as well as an increased L1 Data cache, an increased L2 cache, and a larger micro-op cache. The decoder has been widened, the number of execution ports has increased, and the L1 store bandwidth is doubled. The per-port resources on some of the ports have increased as well.

Intel also spoke about graphics. They put a name to their newest generation of graphics that will span from the integrated graphics up to the discrete graphics: Xe. Until then, we will get ‘Gen11’ graphics which will be paired with Sunny Cove. For these graphics, Intel is boosting up the ‘standard’ GT2 execution unit count from 24 to 64, scaling resources appropriately and supporting a few new features.

Demonstrations of both Sunny Cove and Gen11 were done in the demo area.

We were also treated to new packaging technology. Intel will be using Foveros, a hybrid active interposer design where the interposer is also the chipset, and on top will be the cores and the graphics connected through TSVs to the package underneath. Apparently Foveros translates as ‘awesome’, and Intel is still playing with the technology, hoping to apply it in many areas, such as SoCs and FPGAs. Jim Keller said that the company was having fun with it.

Intel’s first Foveros product also has another first: it will be Intel’s first ever chip which has both Core and Atom CPUs in it working together. The design, aiming for 7W devices, has a single Core CPU and four Atom cores, with separate L2 arrangements but a shared L3 cache. The design uses Sunny Cove in the Core, as well as Gen11 GT2 graphics. Intel stated that this CPU came about because a customer requested a 2mW sleep power state in their CPU, and this is the result of that research. It sounds really good for a first product on Foveros, so it will be interesting to see where the product ends up.

We also had a Q&A session with Raja, Jim, and Murthy. It’s clear that this trio have ambitious ideas for the company, but they are also grounded enough to identify where problems might lie in the design chain.

Final Thoughts

Truth be told, this has been my busiest year ever at AnandTech, which includes almost 200k miles travel and benchmarking on the road with suitcases full of kit. One of my highlights has been my newest ‘2019’ automated benchmark test suite and database – we currently have 70+ processors for users to search through, with tests on CPU, integrated graphics, and discrete GPU on almost a dozen games at four resolutions a piece.

You can see and search our benchmark database at this link: https://anandtech.com/bench

Both AMD and Intel have made bold claims about their 2019 outlook, and both companies have keynote presentations at CES around the corner. AMD will be looking to execute on 7nm for both consumer CPU, enterprise CPU, and GPU, while Intel is still pushing to ramp its current 10nm technology for products by the end of the year, so we’ll still be on 14nm until then. It will be interesting to see if the company launches another round of consumer processors in the middle there. All I know is: it’s going to be another busy year.

42 Comments

View All Comments

damonlynch - Thursday, December 27, 2018 - link

The lowpoints involving CTS-Labs and Krzanich demonstrate the enduring importance treating others with respect. In these instances selfishness and dishonesty were not rewarded. Moreover, one has to wonder what the medium to long-term cost will be of Krzanich's slashing Intel's research expenditures. That has to hurt.Oxford Guy - Friday, December 28, 2018 - link

Respect, like when Google hacked iOS and Safari to install spyware payloads (evercookies)?Or, when it helps with metadata-using algorithms to target US citizens for drone elimination?

Or, when it lied to its own people over China's Dragonfly? Shall I continue?

Reality is that when someone stomps their feet and points fingers when anyone, whether it's a journalist or a self-described security company, exposes flaws in products that have been sold in the market — the blame for those flaws rests solely on the company that created them and put them into the marketplace. Do not shoot the messenger, no matter how much of the guilty company's stock you own.

Google isn't your friend either. No corporation is. They're all out for one thing and one thing only: profit for their people.

Wild-eyed cries, demands for censorship, place the world at greater risk than transparency does. People are owed the knowledge of defects in their products, immediately. It should always be assumed that bad actors have the information during these blackout periods. CTS did the right thing by refusing to have a long one so the guilty party (AMD) could diminish its accountability with PR machinations.

Public outrage is maximized when knowledge is given to them immediately. That's why coverups last for such a long time. We get to find out about the bad deeds decades later, like how the government settled with the family of an intelligence worker who was apparently pushed out of a tall building to keep him from blowing the whistle. Muzzling the so-called free press is not the way to go but there is so much clamor in the tech community for exactly that. The ideological difference between us Westerners and the Chinese is what, exactly?

Respect is earned, not given. Companies that sell defective products have the responsibility to find the problems, make the knowledge public immediately, and fix the problems with maximum haste. They don't have the responsibility to lazily wait for PR-friendly media blackouts arbitrarily chosen by random third parties (particularly those intent on devouring the Internet like Google) expire, after those random unelected third parties find them.

Lord of the Bored - Friday, December 28, 2018 - link

Man, I thought the CTS shills died when their blatant stock-shorting scheme collapsed on its face.tamalero - Saturday, December 29, 2018 - link

They probably have a contract for botters that act like shills to defend the brand. It happens a lot lately.Oxford Guy - Sunday, December 30, 2018 - link

The same ad hominem can be applied to posts like yours. Post a rebuttal and refrain from posting spam.Oxford Guy - Sunday, December 30, 2018 - link

No rebuttal, just an ad hominem. Par for the course.kd_ - Friday, December 28, 2018 - link

LolOxford Guy - Sunday, December 30, 2018 - link

The idea of a free press is humorous in some circles.The idea that consumers should be informed when the products they have been sold are defective is humorous in some circles.

The idea that companies shouldn't be able to collude with unelected third parties to muzzle the tech press, so that PR damage control campaigns can minimize accountability is humorous in some circles.

If any of you truly believe that it's a good thing to have press censorship to protect the reputations and stock prices of companies from ordinary people (rather than insiders) that sell defective goods, then I suggest codifying that with an elected and accountable body rather than blithely enabling for-profit corporations, which do not have a mandate to work in the public interest, to control the narrative and the flow of information with whatever arbitrary processes they dream up to help with their quest for profit and dominance. This means things like standardization in procedures (such as the apparently very beloved first-amendment-quashing blackout periods), standards that are voted on and vetted by a larger community than various corporations' executives.

(Oh, look, it's a bot! It's not the person posting "Lol" or the brainless ad hominem one-two sentence troll posts that so many in the tech community think are impressive enough to masquerade as a rebuttal.)

gteichrow - Thursday, January 24, 2019 - link

Well said.Flunk - Saturday, December 29, 2018 - link

Good luck with the word-salad of irrelevant whataboutism. OP didn't say a word about Google.