Intel’s 11th Gen Core Tiger Lake SoC Detailed: SuperFin, Willow Cove and Xe-LP

by Dr. Ian Cutress on August 13, 2020 9:01 AM EST- Posted in

- CPUs

- Intel

- SoCs

- Tiger Lake

- 10+

- Xe-LP

- Willow Cove

- Intel Arch Day 2020

- SuperFin

- 10SF

Tiger Lake Performance and Products

For Tiger Lake, Intel has made some substantial changes over its previous Ice Lake design. If you’ve skipped to the end of this article without reading the pages in between, then in my opinion you should know that new 10nm SuperFin is what I would consider one of the big talking points.

SuperFin and Willow Cove Frequencies

Intel has done away with the 10+ and 10++ naming, and 10nm SuperFin (10SF) has replaced 10+.

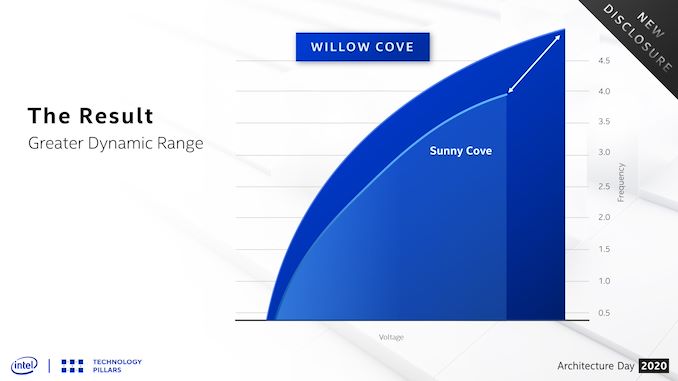

It is called SuperFin because Intel has refined its next generation transistor fins and the metal stack in its manufacturing in order to enable a wider range of performance and efficiency compared to the base 10nm process. What this means is that Intel claims that at the same power as Ice Lake, Intel shows Tiger Lake as having a +10% frequency uplift, going from 4.0 GHz up to 4.5 GHz. Not only this, but because the new 10SF allows a wider range, when the core is pushed, Tiger Lake should move within a hair of 5.0 GHz.

That would be a +20% direct frequency uplift in peak performance, bigger than a traditional intra-node manufacturing update, before we even talk about any microarchitecture improvements.

On the core design front, comparing the new Willow Cove core to the Ice Lake core, we have very few changes. Most of it is identical, except for the L2 cache (+150%, now non-inclusive) and the L3 cache (+50%) getting bigger and new memory security measures being implemented. Intel has quoted that it went after frequency rather than IPC, as +20% frequency is more akin to a node change in performance, whereas chasing IPC in this product would not have produced the same change. As it stands, we predict a small single digit uplift in IPC. We will have to wait until the next generation product to see IPC increase again.

Xe Graphics

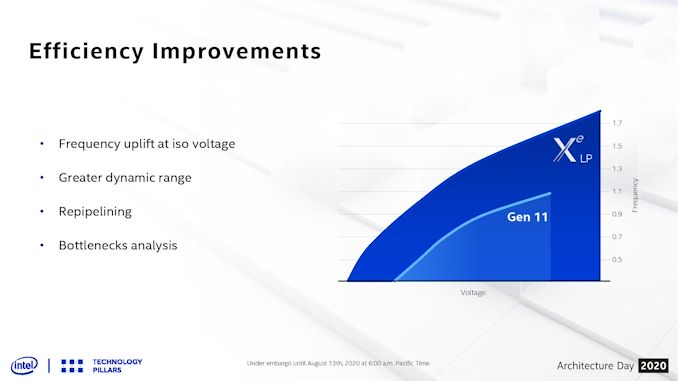

Tiger Lake will also be the launch vehicle for Intel’s Xe Graphics strategy. Onboard we get 96 Xe-LP execution units, up 50% from 64, running at a frequency at least 50% higher, at 1600+ MHz.

Intel is advertising the graphics performance increase over Ice Lake of around 2x all-in. Tiger Lake supports not only DDR4-3200 and LPDDR4X-4267, but LPDDR5-5400 as well, which will be good for 86.4 GB/s of bandwidth that would be great for the integrated graphics. Though it should be noted that laptop vendors aren’t jumping on the LPDDR5 bandwagon immediately, as prices are high and volumes are low / going into smartphones. LPDDR5 is going to be more of a mid-cycle update for Tiger Lake.

The Rest

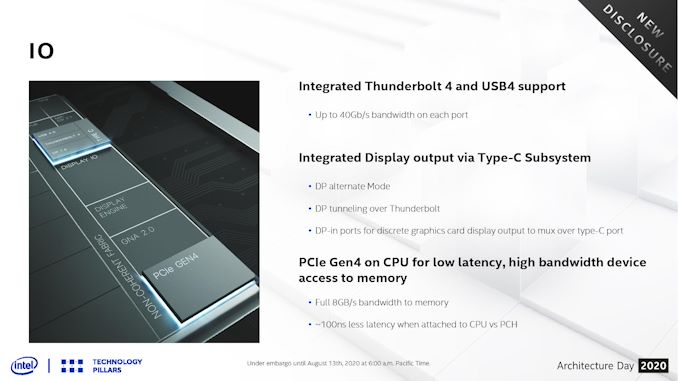

On top of performance, Tiger Lake also expands its IO and Display capabilities, enabling Thunderbolt 4 natively, as well as four 4K displays and support for AV1 decode among other things. Intel states that TGL supports PCIe 4.0, and the amount of lanes will scale with core count (numbers point to an 8-core Tiger Lake in the future). Intel didn’t go into lane counts, but based on a number of pointers on Intel’s slides, we believe the four core version of the chip has a 4.0 x4 link.

The official launch for the Intel’s 11th Gen Core Mobile processors (Tiger Lake) is going to be on September 2nd. At that time we expect to see some of Intel’s OEM partners showcase product designs ahead of Q4 launches in time for the holiday season. There are still a number of questions on the chip, Intel’s ability to manufacture it, how it will compete against AMD, and so forth, which we expect to learn closer to that time.

Tiger Lake on 10 W to 65 W CPUs

As a final thought – one of the first comments made by Intel as part of our briefings was that the Tiger Lake design is going to be scalable, from 10 watts to 65 watts. The current processor we know about today is a four core processor at 15 watts. We’ve already surmised that Intel is preparing an eight core variant, with double the L3 cache, which we suspect to go up to that 65 W mark - however there is a question of where that product would end up. Traditional mobile processors tend to have a ceiling of 45-54 W TDP, and the 65 W space is usually reserved for desktop / socketed processors. Intel previously launched 65 W versions of its Broadwell mobile CPU on the desktop in 2015, and I wonder if we might see something similar here, which would enable Willow Cove, 10SF, and integrated Xe-LP on the desktop.

All of our information today came from Intel’s closed door Architecture Day 2020, held less than 48 hours prior to when this goes public. Aside from my article on Tiger Lake, and Ryan’s article on Intel’s Xe Portfolio, a number of other topics were covered, which we’ll dive into over the next few days.

71 Comments

View All Comments

Mark242 - Thursday, August 13, 2020 - link

Is the SuperFin tech really a generational impovement of the 10nm process or is it a backport from 7nm?Sahrin - Thursday, August 13, 2020 - link

So basically Intel had to re-engineer the entire technology stack to get 10nm to work.Are they still using EUV on all layers?

IanCutress - Thursday, August 13, 2020 - link

EUV for Intel is on 7nm. There's no EUV on 10 or 10SF.trivik12 - Thursday, August 13, 2020 - link

Does the comment that 10 SFE is optimized for DC and so Alderlake will not see any xtor improvements from TGL and its just microarchitecture changes to improve performance.Thunder 57 - Thursday, August 13, 2020 - link

"As for the L3 cache on a quad-core Willow Cove system, Intel has moved from an 8 MiB non-inclusive shared L3 cache to a 12 MiB shared L3 cache."Pretty sure you meant inclusive L3, which the "Cache Comparison" chart got right.

WaltC - Thursday, August 13, 2020 - link

Ian eating more silicon...ah...like a breath of fresh air...;) I find silicon wafers are best enjoyed with a set of Unobtanium™ dentures topped with the diamond tooth inserts and platinum alloy tips--chews up nice, goes down smooth! I have to agree in this really nice write up making the most of the sparseness Intel supplied, that all of this stuff looks incremental to me. Bits and pieces improved. Reading between the lines it looks like Intel is still struggling with its process nodes--the fact that they cannot ship even this right now is certainly telling...nor can they even supply a ship date, apparently.Eliadbu - Thursday, August 13, 2020 - link

I sure hope to see TGL scaled to 8 cores CPUs. I feel like the biggest drawback of ICL is it was scaled up to 4 cores only making it underpowered to even comet lake u (with up to 6 cores).harobikes333 - Saturday, August 15, 2020 - link

"If you’ve skipped to the end of this article without reading the pages in between,...."^ You caught me - I'm a sucker for summaries. If I have time, I go back & read through the full articles. Alas, there's only so much time in a day!

ksec - Saturday, August 15, 2020 - link

In the previous driver update I was under the impression AV1 decode is only partly ASIC accelerated. But the slides here seems to imply it is fully Hardware Decoded.Farfolomew - Saturday, August 15, 2020 - link

What's Intel playing at here with ignoring the 8-core offering of Renoir Mobile and just going for 4-core with Tiger Lake? This will be in effect for an entire generation (11th Gen) of mobile products, that they'll have a 50% core deficit. I get that Tiger Lake will have ~20% better ST performance over Renoir, and it could be argued that 4 cores is all one needs nowadays on Mobile, but still, it seems like a calculated and potentially dangerous move by Intel to ignore AMD's core-count advantage.