The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTLakefield in Terms of Laptop Size

In a traditional AMD or Intel processor designed for laptops, we experience two to eight processing cores, along with some graphics performance, and it is up to the company to build the chip with the aim of hitting the right efficiency point (15 W, or 35/45 W) to enable the best performance for a given power window. These processors also contain a lot of extra connectivity and functionality, such as a dual channel memory controller, extra PCIe lanes to support external graphics, support for USB port connectivity or an external connectivity hub, or in the case of Intel’s latest designs, support for Thunderbolt built right into the silicon without the need for an external controller. These processors typically have physical dimensions of 150 square millimeters or more, and in a notebook, when paired with the additional power delivery and controllers needed such as Wi-Fi and modems, can tend towards the board inside the system (the motherboard) totaling 15 square inches total.

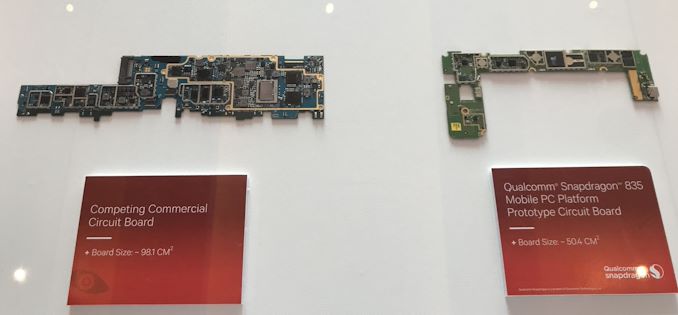

One of Qualcomm’s examples from 2018

For a Qualcomm processor designed for laptops, the silicon is a paired down to the essentials commonly associated with a smartphone. This means that modem connectivity is built into the processor, and the hardware associated with power delivery and USB are all on the scale of a smartphone. This means a motherboard designed around a Qualcomm processor will be around half the size, enabling different form factors, or more battery capacity in the same size laptop chassis.

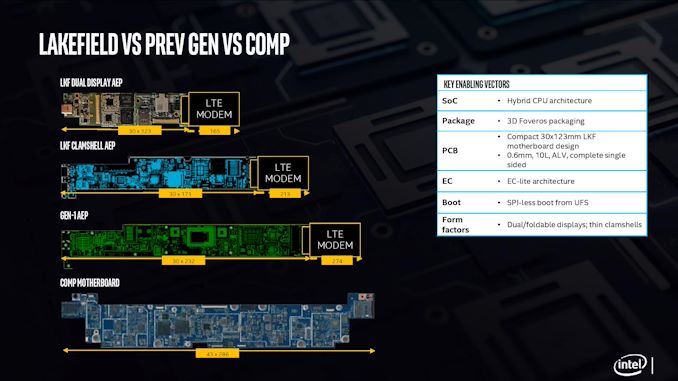

With Intel’s new Lakefield processor design, the chip is a lot smaller than previous Intel implementations. The company designed the processor from the ground up, with as much included on the CPU as to not need additional chips on the motherboard, and to fit the dimensions similar to one of Qualcomm’s processors. Above is a slide showing how Intel believes that with an LTE modem included, a Lakefield motherboard can move down to 7.7 square inches, similar to a Qualcomm design. This leaves more room for battery inside a device.

When Intel compares it against its own previous low power CPU implementations, the company quotes a 60% decrease in overall board area compared to its first generation 4.5 W processors.

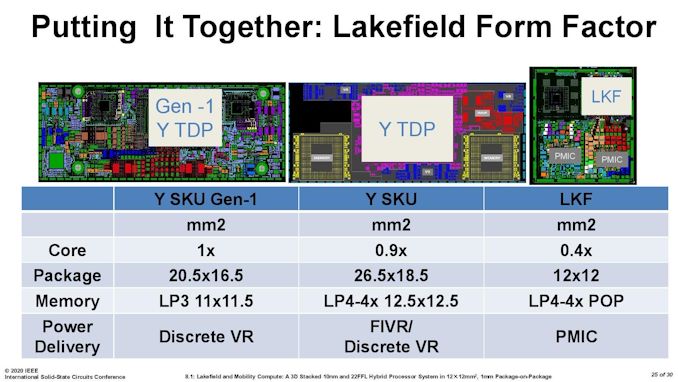

It is worth noting that for power delivery, Intel placed MIMCAPs inside the Lakefield silicon, much like a smartphone processor, and as a result it can get by on the power delivery implementation with a pair of PMICs (power management ICs). The reason why there is two is because of the two silicon dies inside – they are controlled differently for power for a number of technical reasons. If each layer within an active stacked implementation requires its own PMIC, that would presumably put an upper limit on future stacked designs – I fully expect Intel to be working on some sort of solution for this for it not to be an issue, however that wasn’t implemented in time for Lakefield.

For those that are interested, Lakefield’s PMICs are under the codenames Warren Cove and Castro Cover, and were developed in 2017-2018.

221 Comments

View All Comments

AhsanX - Thursday, July 2, 2020 - link

The Sunny Cove has AVX-512 but Tremont cores don,t have any AVX. So Intel disabled AVX on the Sunny Cove core too, as heat was gonna be a problem if they let it enabled.ikjadoon - Thursday, July 2, 2020 - link

Did we read the same article? AVX-512 was completely removed (i.e., physically) from the Sunny Cove dies because of Windows 10 compatibility problems.Windows was never built for x86 heterogeneous processing and still cannot do anything close now in 2020 (perhaps that would've been a smarter investment than going all-in on touch in 2008!).

Intel & Microsoft remain stuck in late 2010s for their low-power / mobile-first / thin-client transition caused by the dominating success of smartphones & ARM-based architectures wiping out anything of interest in low-power x86.

There's a reason Intel just nearly stopped all development on Atom: nobody give a crap about the Pentium Silver & Celeron CPUs.

ikjadoon - Thursday, July 2, 2020 - link

*gaveJorgp2 - Thursday, July 2, 2020 - link

>There's a reason Intel just nearly stopped all development on Atom: nobody give a crap about the Pentium Silver & Celeron CPUs.Lol, no

ProDigit - Friday, July 3, 2020 - link

The $160 laptop I purchased from hp, with an N5000 in it, works really well!Would have been better if used on a desktop, and the core count was quadrupled.

extide - Thursday, July 2, 2020 - link

It's not a windows issue. Even if you ran Linux or any other OS on here you would have to run with CPU's all supporting the same ISA. ARM specifically designs cores to pair up together such that they have the exact same ISA (instruction support) so this isn't an issue in cell phones.I mean theoretically you could have the processors support a slightly different ISA and have it throw an interrupt if it tried to execute an instruction that the current core didn't support but a different one did and then the scheduler would have to move that thread to the other core. That could get really janky though, which is why nobody has talked about doing this yet.

Also, they said in this article that even though Intel said they removed the AVX512 units -- it can still be seen in the die shots.

Also, Intel didn't stop development on Atom -- this chip has a brand new core and their public roadmaps have several more in the future.

reggjoo1 - Tuesday, July 7, 2020 - link

They’re gonna have to develop more for atom, and get into the right “governor “ for crossover operation, more than scheduler tweaks. They have a lot to learn, and it may come down to the quality over the I/O system for these to really succeed. As long as their "ego" doesn't get in their way, and they learn from the "smartphone arena, they might have something for X86.dotjaz - Friday, July 3, 2020 - link

Did we read the same article? AVX-512 was clearly not removed.dotjaz - Friday, July 3, 2020 - link

There, "Intel has stated on the record repeatedly that they removed it. The die shot of the compute silicon shows that not to be the case." If you can read.jeremyshaw - Friday, July 3, 2020 - link

That was a later edit. Originally Ian claimed it was removed.