The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTHybrid CPUs: Sunny Cove and Tremont

Now that we’ve gone over the concept of the heterogeneous core design, it’s time to dig into each of the cores separately and some of the tradeoffs that Intel has had to do in order to get this to work.

Big Sunny Cove

As mentioned previously, the big core in Lakefield is known as Sunny Cove, and stands as the same core we currently see in Intel’s Ice Lake mobile processors today. It is officially Intel’s second 10nm-class core (the first one being the DOA Cannon Lake / Palm Cove), but the first one in mass production.

We have covered the Sunny Cove core microarchitecture in great detail, and you can read about it here:

Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

The quick recap is as follows.

Very similar to a Skylake design, except that:

- Better prefetchers and branch predictors

- +50% L1 Data Cache

- +100% L1 Store Bandwidth

- +100% L2 Cache w/improved L2 TLB

- +50% Micro-op Cache

- +25% uops/cycle into reorder buffer

- +57% reorder buffer size

- +25% execution ports

- AVX-512 with VNNI

The side effect of increasing the L1 Data cache size was a decrease in latency, with the L1-D moving to a 5-cycle rather than a 4-cycle. Normally that would sound like a 25% automatic speed drop, however the increased L1 size, L1 bandwidth, and L2 cache all help for an overall improvement.

Intel claimed that Sunny Cove should perform ~18% better clock-for-clock compared to a Skylake core design. In our initial review of Ice Lake, we compared the i7-1065G7 processor (Ice Lake) to the Core i9-9900K processor (Coffee Lake, a Skylake derivative), and saw a 19% increase in performance per clock, essentially matching Intel’s advertised numbers.

(However it should be noted that overall we didn’t see that much of an improvement at the overall chip and product level, because the Ice Lake ran at a lower frequency, which removed any raw clock speed gain.)

Small Tremont Atom

Arguably the Tremont core is the more interesting of the two in the Lakefield design. Lakefield will be the first consumer product built with a Tremont core inside, and as a result we have not had a chance to test it yet. But we have gone over the microarchitecture extensively in a previous article.

Intel's new Atom Microarchitecture: The Tremont Core in Lakefield

The reason why Tremont is more exciting is because updates to Intel’s Atom line of processor cores happen at a much slower pace. Traditionally Atom has been a core that focuses on the low cost part of the market, so there isn’t that much of a need to make it right at the bleeding edge as it commands lower margins for the company. It still plays a vital role, but for context, here is what year we’ve seen new Atom designs come into the market:

- 2008: Bonnell

- 2011: Saltwell

- 2013: Silvermont

- 2015: Airmont

- 2016: Goldmont

- 2017: Goldmont Plus

- 2020: Tremont

Tremont is the first new Atom microarchitecture design for three years, and technically only the third Atom design to be an out-of-order design. However, Tremont is a big jump in a lot of under-the-hood changes compared to Goldmont Plus.

- Can be in a 1-core, 2-core, or 4-core cluster

- +33% L1-Data Cache over Goldmont+, no performance penalty

- Configurable L2 cache per cluster, from 1.5 MB to 4.5 MB

- +50% L2 TLB (1024-entry, up from 512)

- New 2x3-wide decoder, rather than single 3-wide decoder

- +119% re-order buffer (208, up from 92)

- 8 execution ports, 7 reservation stations

- 3 ALUs, 2 AGUs

- Dual 128-bit AES units

- New Instructions*

What made the most noise is the new dual 3-wide decoder. On Intel’s primary Core line, we haven’t seen much change in the decoder in recent generations – it still uses a 5-wide decoder, split between 1 complex decoder and 4 simple decoders, backed with a micro-op cache. Tremont’s new dual 3-wide decoder can manage dual data streams in order to keep the buffers further down the core fed. Intel stated that for the design targets of Tremont, this was more area and power efficient than a 6-wide decoder, or having a large micro-op cache in the processor design (Atom cores have not have micro-op caches to date). Intel states that the decoder design helps shape the back-end of the core and the balance of resources.

Also worthy of note in Tremont is the L1-Data cache. Intel moved up from a 24 KiB design to a 32 KiB design, an increase of 33%. This is mostly due to using the latest manufacturing node. However, an increase in cache size is typically accompanied with an increase in latency – as we saw on Sunny Cove, we moved from a 4-cycle to a 5-cycle. However in Tremont’s case, the L1-Data cache stays at 3-cycle for an 8-way 32 KiB design. Even Skylake’s L1-D cache, at an 8-way 32 KiB design, is a 4-cycle, which means that Tremont’s L1-D is tuned to surpass even Skylake here.

The final point, Tremont’s new instructions, requires a section all on its own, specifically because none of the new instructions are supported in Lakefield.

What’s Missing in Lakefield

One of the biggest issues with a heterogeneous processor design is software. Even if we go beyond the issues that come with scheduling a workload on such a device, the problem is that most programs are designed to work on whatever microarchitecture they were written for. Generic programs are meant to work everywhere, while big publishers will write custom code for specific optimizations, such as if AVX-512 is detected, it will write AVX-512.

The hair-pulling out moment occurs when a processor has two different types of CPU core involved, and there is the potential for each of them to support different instructions or commands. Typically the scheduler makes no guarantee that software will run on any given core, so for example if you had some code written for AVX-512, it would happily run on an AVX-512 enabled core, but cause a critical fault on a core that doesn’t have AVX-512. The core won’t even know it’s an AVX-512 instruction until it comes time to decode it, and just throw an error when that happens. Not only this, but the scheduler has the right to move a thread when it needs to – if it moves a thread in the middle of an instruction stream, that can cause errors too. The processor could also move a thread to prevent thermal hotspots occurring, which will then cause a fault.

There could be a situation where the programmer can flag that their code has specific instructions. In a program with unique instructions, there’s very often a check that tries to detect support, in order to say to itself something like ‘AVX512 will work here!’. However, all modern software assumes a homogeneous processor – that all cores will support all of the same instructions.

It becomes a very chicken and egg problem, to a certain degree.

The only way out of this is that both processors in a hybrid CPU have to support the same instructions completely. This means that we end up with the worst of both worlds – only instructions supported by both can be enabled. This is the lowest common denominator of the two, and means that in Lakefield we lose support for AVX-512 on Sunny Cove, but also things like GFNI, ENCLV, and CLDEMOTE in Tremont (Tremont is actually rather progressive in its instruction support).

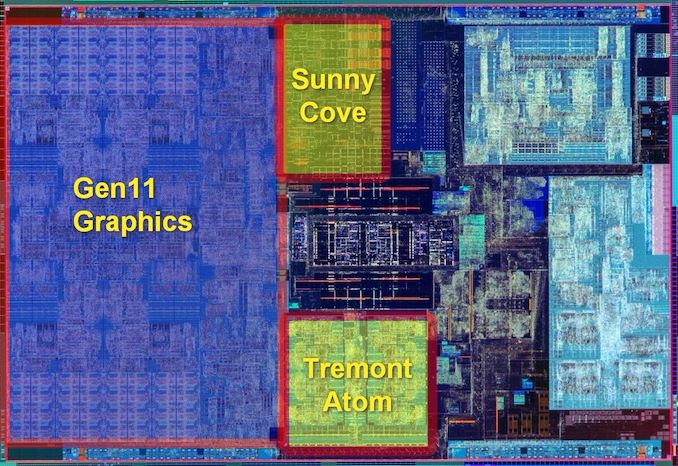

Knowing that Lakefield was going to have to take the lowest common denominator from the two core designs, Intel probably should physically removed the very bulky AVX-512 unit from the Sunny Cove core. Looking at the die shot, it's still there - there was some question going into the recent disclosures as to whether it would still be there, but Intel has stated on the record repeatedly that they removed it. The die shot of the compute silicon shows that not to be the case.

For x86 programmers doing instruction detection by code name or core family, this might have to change. In the smartphone world, where 4+4 processor designs are somewhat the norm, this lowest common denominator issue has essentially been universally adopted. There was some slight issue with a Samsung processor that had a non-unified cache setup, which ended up being rectified in firmware. But both sets of CPUs had to rely on lowest common denominator instructions.

221 Comments

View All Comments

Drkrieger01 - Friday, July 3, 2020 - link

I'm not one to criticize, but this comment section is a dumpster fire.First of all, this is a FIRST GENERATION PRODUCT that hasn't even/barely made it to market.

Secondly, no one has really gotten to do a deep dive on performance of said product.

Thirdly, this processor package can be used from low end laptops, to tablets, and possibly it other mobile devices.

Fourth - who the hell cares about AVX? Do you people realize just how little AVX-512 is actually used in day-to-day usage scenarios that this CPU would be designed for? (mobile)

How about we wait to see what this product actually does for the technology market before we write it off as 'Intel Trash'.

/drops mic

Wilco1 - Friday, July 3, 2020 - link

What hasn't helped is that both Lakefield and Tremont have been hyped up for some time, so expectations were high. Some sites even claim that Tremont is a Cortex-A77 class core purely based on it having 2x3 decoders... That is setting things up for disappointment and failure."Wait for the next generation, it'll be great" has been used on every Atom, but it never lived up to its promise.

Deicidium369 - Sunday, July 5, 2020 - link

"Wait for the next generation, it'll be great" has been used on every AMD product, but it never lived up to its promise."Wilco1 - Sunday, July 5, 2020 - link

Without a doubt AMD has a much better track record than Intel - where are the 10nm desktops and servers? And Lakefield getting 60% of performance of the 18 month old 8cx is embarassing...lmcd - Sunday, July 5, 2020 - link

Track record is more than the last calendar year in a single market segment. You're kidding yourself if the company that brought Bulldozer, Piledriver, Steamroller, and Excavator to market promising that this was the one that fixed the architecture suddenly gets a pass on everything.Korguz - Monday, July 6, 2020 - link

and yet, it seems intel gets a pass when they make mistakes, or screw up. go figure.Spunjji - Monday, July 6, 2020 - link

Do you want to produce a similar list for the Pentium 4, Itanium, and Atom product ranges, or would that require a little too much intellectual honesty?Both companies have extended periods of bad products. Only one of them had the excuse of mediocre revenues, and only one of them was punished for their repeated failures with a dramatic loss in market share. Tells you a lot, really.

Spunjji - Monday, July 6, 2020 - link

Weird - pretty sure Athlon 64 was a rout, the first Athlon X2 was a rout, and Ryzen 3000 was a rout... You post some of the most asinine crap in this comment section when you're bagging on AMD, which is a real shame, because the rest of the time you seem to make a fair bit of sense.abufrejoval - Friday, July 3, 2020 - link

The entire article is about explaining what can already be inferred from the information we have at hand.Chips are engineering and physics, very little magic and a great degree of predictability.

None of the elements here are first generation, only their combination is a bit new. Ice Lake can be measured, you can benchmark a single core at 5 Watts with ThrottleStop and pinning the benchmark to a single core in any IceLake system. Atoms are well known and we can be sure that when Intel claims 23% improvement at the same power, it won't be 230%.

You can predict it's going to be much more expensive to make than a normal Atom, and you can measure that a single Core CPU below 5 Watts doesn't have a lot of horse power, while multiple cores on this design leave no Wattage for the big one.

This chip will be very expensive to make, so it won't sell at Atom prices. All the engineering is about making small enough to compete with ARM designs, yet capable of competing at 5Watts.

Yes, Ian could still be wrong here and there, but there isn't a lot of room to err.

The rest of us agree, that this chip will fail to make Intel rich and customers happy.

If we should be all wrong, remind us and we'll show proper contrition and learn.

But we bet on what we extrapolate from what we can know and measure, that's our duty as engineers.

lmcd - Sunday, July 5, 2020 - link

Tremont is absolutely new and the thermal characteristics of the package and layout also determine a lot.