The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTThermal Management on Stacked Silicon

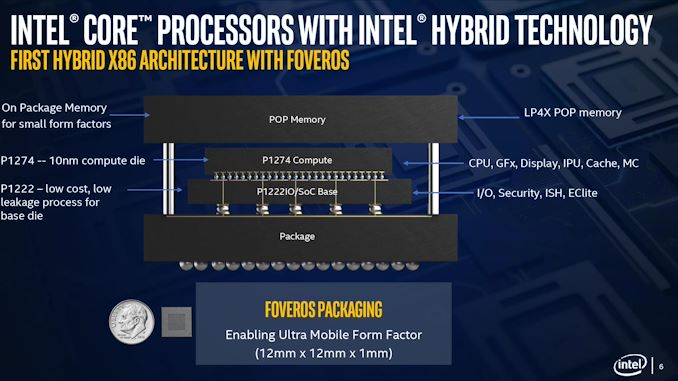

With a standard processor design, there is a single piece of silicon doing all the work and generating the heat – it’s bonded to the package (which doesn’t do any work) and then depending on the implementation, there’s some adhesive to either a cooler or a headspreader then a cooler. When moving to a stacked chiplet design, it gets a bit more complicated.

Having two bits of silicon that ‘do work’, even if one is the heavy compute die and the other is an active interposer taking care of USB and audio and things, does mean that there’s a thermal gradient between the silicon, and depending on the bonding, potential for thermal hotspots and build-up. Lakefield makes it even more complex, by having an additional DRAM package placed on top but not directly bonded.

We can take each of these issues independently. For the case of die-on-die interaction, there is a lot of research going into this area. Discussions and development about fluidic channels between two hot silicon dies have been going on for a decade or longer in academia, and Intel has mentioned it a number of times, especially when relating to a potential solution of its new die-to-die stacking technology.

They key here is hot dies, with thermal hotspots. As with a standard silicon design, ideally it is best to keep two high-powered areas separate, as it gives a number of benefits with power delivery, cooling, and signal integrity. With a stacked die, it is best to not have hotspots directly on top of each other, for similar reasons. Despite Intel using its leading edge 10+ process node for the compute die, the base die is using 22FFL, which is Intel’s low power implementation of its 14nm process. Not only that, but the base die is only dealing with IO, such as USB and PCIe 3.0, which is essentially fixed bandwidth and energy costs. What we have here is a high-powered die on top of a low powered die, and as such thermal issues between the two silicon die, especially in a low TDP device like Lakefield (7W TDP), are not an issue.

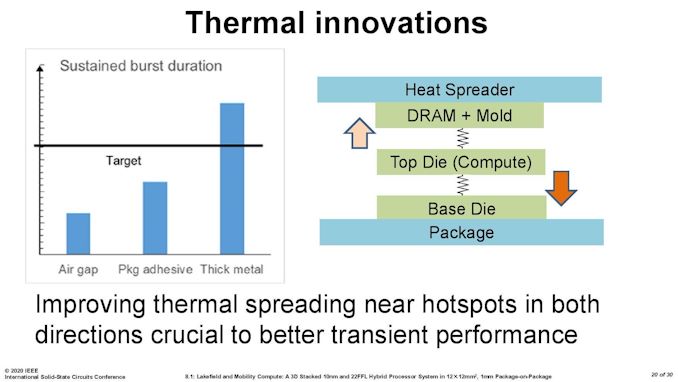

What is an issue is how the compute die gets rid of the heat. On the bottom it can do convection by being bonded to more silicon, but the top is ultimately blocked by that DRAM die. As you can see in the image above, there’s a big air gap between the two.

As part of the Lakefield design, Intel had to add in a number of design changes in order to make the thermals work. A lot of work can be done with the silicon design itself, such as matching up hotspots in the right area, using suitable thickness of metals in various layers, and rearranging the floorplan to reduce localized power density. Ultimately both increasing the thermal mass and the potential dissipation becomes high priorities.

Lakefield CPUs have a sustained power limit of 7 watts – this is defined in the specifications. Intel also has another limit, known as the turbo power limit. At Intel’s Architecture Day, the company stated that the turbo power limit was 27 watts, however in the recent product briefing, we were told is set at 9.5 W. Historically Intel will let its OEM partners (Samsung, Lenovo, Microsoft) choose its own values for these based on how well the design implements its cooling – passive vs active and heatsink mass and things like this. Intel also has another factor of turbo time, essentially a measure of how long the turbo power can be sustained for.

When we initially asked Intel for this value, they refused to tell us, stating that it is proprietary information. After I asked again after a group call on the product, I got the same answer, despite the fact that I informed the Lakefield team that Intel has historically given this information out. Later on, I found out through my European peers that in a separate briefing, they gave the value of 28 seconds, to which Intel emailed me this several hours afterwards. This value can also be set by OEMs.

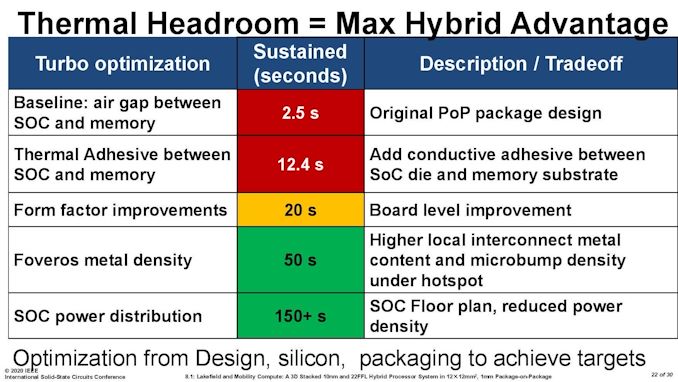

Then I subsequently found one of Intel’s ISSCC slides.

This slide shows that a basic implementation would only allow sustained power for 2.5 seconds. Adding in an adhesive between the top die and the DRAM moves up to 12.4 seconds, and then improving the system cooling goes up to 20 seconds. The rest of the improvements work below the compute die: a sizeable improvement comes from increasing the die-to-die metal density, and then an optimized power floor plan which in total gives sustained power support for 150+ seconds.

221 Comments

View All Comments

Drkrieger01 - Friday, July 3, 2020 - link

I'm not one to criticize, but this comment section is a dumpster fire.First of all, this is a FIRST GENERATION PRODUCT that hasn't even/barely made it to market.

Secondly, no one has really gotten to do a deep dive on performance of said product.

Thirdly, this processor package can be used from low end laptops, to tablets, and possibly it other mobile devices.

Fourth - who the hell cares about AVX? Do you people realize just how little AVX-512 is actually used in day-to-day usage scenarios that this CPU would be designed for? (mobile)

How about we wait to see what this product actually does for the technology market before we write it off as 'Intel Trash'.

/drops mic

Wilco1 - Friday, July 3, 2020 - link

What hasn't helped is that both Lakefield and Tremont have been hyped up for some time, so expectations were high. Some sites even claim that Tremont is a Cortex-A77 class core purely based on it having 2x3 decoders... That is setting things up for disappointment and failure."Wait for the next generation, it'll be great" has been used on every Atom, but it never lived up to its promise.

Deicidium369 - Sunday, July 5, 2020 - link

"Wait for the next generation, it'll be great" has been used on every AMD product, but it never lived up to its promise."Wilco1 - Sunday, July 5, 2020 - link

Without a doubt AMD has a much better track record than Intel - where are the 10nm desktops and servers? And Lakefield getting 60% of performance of the 18 month old 8cx is embarassing...lmcd - Sunday, July 5, 2020 - link

Track record is more than the last calendar year in a single market segment. You're kidding yourself if the company that brought Bulldozer, Piledriver, Steamroller, and Excavator to market promising that this was the one that fixed the architecture suddenly gets a pass on everything.Korguz - Monday, July 6, 2020 - link

and yet, it seems intel gets a pass when they make mistakes, or screw up. go figure.Spunjji - Monday, July 6, 2020 - link

Do you want to produce a similar list for the Pentium 4, Itanium, and Atom product ranges, or would that require a little too much intellectual honesty?Both companies have extended periods of bad products. Only one of them had the excuse of mediocre revenues, and only one of them was punished for their repeated failures with a dramatic loss in market share. Tells you a lot, really.

Spunjji - Monday, July 6, 2020 - link

Weird - pretty sure Athlon 64 was a rout, the first Athlon X2 was a rout, and Ryzen 3000 was a rout... You post some of the most asinine crap in this comment section when you're bagging on AMD, which is a real shame, because the rest of the time you seem to make a fair bit of sense.abufrejoval - Friday, July 3, 2020 - link

The entire article is about explaining what can already be inferred from the information we have at hand.Chips are engineering and physics, very little magic and a great degree of predictability.

None of the elements here are first generation, only their combination is a bit new. Ice Lake can be measured, you can benchmark a single core at 5 Watts with ThrottleStop and pinning the benchmark to a single core in any IceLake system. Atoms are well known and we can be sure that when Intel claims 23% improvement at the same power, it won't be 230%.

You can predict it's going to be much more expensive to make than a normal Atom, and you can measure that a single Core CPU below 5 Watts doesn't have a lot of horse power, while multiple cores on this design leave no Wattage for the big one.

This chip will be very expensive to make, so it won't sell at Atom prices. All the engineering is about making small enough to compete with ARM designs, yet capable of competing at 5Watts.

Yes, Ian could still be wrong here and there, but there isn't a lot of room to err.

The rest of us agree, that this chip will fail to make Intel rich and customers happy.

If we should be all wrong, remind us and we'll show proper contrition and learn.

But we bet on what we extrapolate from what we can know and measure, that's our duty as engineers.

lmcd - Sunday, July 5, 2020 - link

Tremont is absolutely new and the thermal characteristics of the package and layout also determine a lot.