The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTHybrid CPUs: Sunny Cove and Tremont

Now that we’ve gone over the concept of the heterogeneous core design, it’s time to dig into each of the cores separately and some of the tradeoffs that Intel has had to do in order to get this to work.

Big Sunny Cove

As mentioned previously, the big core in Lakefield is known as Sunny Cove, and stands as the same core we currently see in Intel’s Ice Lake mobile processors today. It is officially Intel’s second 10nm-class core (the first one being the DOA Cannon Lake / Palm Cove), but the first one in mass production.

We have covered the Sunny Cove core microarchitecture in great detail, and you can read about it here:

Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

The quick recap is as follows.

Very similar to a Skylake design, except that:

- Better prefetchers and branch predictors

- +50% L1 Data Cache

- +100% L1 Store Bandwidth

- +100% L2 Cache w/improved L2 TLB

- +50% Micro-op Cache

- +25% uops/cycle into reorder buffer

- +57% reorder buffer size

- +25% execution ports

- AVX-512 with VNNI

The side effect of increasing the L1 Data cache size was a decrease in latency, with the L1-D moving to a 5-cycle rather than a 4-cycle. Normally that would sound like a 25% automatic speed drop, however the increased L1 size, L1 bandwidth, and L2 cache all help for an overall improvement.

Intel claimed that Sunny Cove should perform ~18% better clock-for-clock compared to a Skylake core design. In our initial review of Ice Lake, we compared the i7-1065G7 processor (Ice Lake) to the Core i9-9900K processor (Coffee Lake, a Skylake derivative), and saw a 19% increase in performance per clock, essentially matching Intel’s advertised numbers.

(However it should be noted that overall we didn’t see that much of an improvement at the overall chip and product level, because the Ice Lake ran at a lower frequency, which removed any raw clock speed gain.)

Small Tremont Atom

Arguably the Tremont core is the more interesting of the two in the Lakefield design. Lakefield will be the first consumer product built with a Tremont core inside, and as a result we have not had a chance to test it yet. But we have gone over the microarchitecture extensively in a previous article.

Intel's new Atom Microarchitecture: The Tremont Core in Lakefield

The reason why Tremont is more exciting is because updates to Intel’s Atom line of processor cores happen at a much slower pace. Traditionally Atom has been a core that focuses on the low cost part of the market, so there isn’t that much of a need to make it right at the bleeding edge as it commands lower margins for the company. It still plays a vital role, but for context, here is what year we’ve seen new Atom designs come into the market:

- 2008: Bonnell

- 2011: Saltwell

- 2013: Silvermont

- 2015: Airmont

- 2016: Goldmont

- 2017: Goldmont Plus

- 2020: Tremont

Tremont is the first new Atom microarchitecture design for three years, and technically only the third Atom design to be an out-of-order design. However, Tremont is a big jump in a lot of under-the-hood changes compared to Goldmont Plus.

- Can be in a 1-core, 2-core, or 4-core cluster

- +33% L1-Data Cache over Goldmont+, no performance penalty

- Configurable L2 cache per cluster, from 1.5 MB to 4.5 MB

- +50% L2 TLB (1024-entry, up from 512)

- New 2x3-wide decoder, rather than single 3-wide decoder

- +119% re-order buffer (208, up from 92)

- 8 execution ports, 7 reservation stations

- 3 ALUs, 2 AGUs

- Dual 128-bit AES units

- New Instructions*

What made the most noise is the new dual 3-wide decoder. On Intel’s primary Core line, we haven’t seen much change in the decoder in recent generations – it still uses a 5-wide decoder, split between 1 complex decoder and 4 simple decoders, backed with a micro-op cache. Tremont’s new dual 3-wide decoder can manage dual data streams in order to keep the buffers further down the core fed. Intel stated that for the design targets of Tremont, this was more area and power efficient than a 6-wide decoder, or having a large micro-op cache in the processor design (Atom cores have not have micro-op caches to date). Intel states that the decoder design helps shape the back-end of the core and the balance of resources.

Also worthy of note in Tremont is the L1-Data cache. Intel moved up from a 24 KiB design to a 32 KiB design, an increase of 33%. This is mostly due to using the latest manufacturing node. However, an increase in cache size is typically accompanied with an increase in latency – as we saw on Sunny Cove, we moved from a 4-cycle to a 5-cycle. However in Tremont’s case, the L1-Data cache stays at 3-cycle for an 8-way 32 KiB design. Even Skylake’s L1-D cache, at an 8-way 32 KiB design, is a 4-cycle, which means that Tremont’s L1-D is tuned to surpass even Skylake here.

The final point, Tremont’s new instructions, requires a section all on its own, specifically because none of the new instructions are supported in Lakefield.

What’s Missing in Lakefield

One of the biggest issues with a heterogeneous processor design is software. Even if we go beyond the issues that come with scheduling a workload on such a device, the problem is that most programs are designed to work on whatever microarchitecture they were written for. Generic programs are meant to work everywhere, while big publishers will write custom code for specific optimizations, such as if AVX-512 is detected, it will write AVX-512.

The hair-pulling out moment occurs when a processor has two different types of CPU core involved, and there is the potential for each of them to support different instructions or commands. Typically the scheduler makes no guarantee that software will run on any given core, so for example if you had some code written for AVX-512, it would happily run on an AVX-512 enabled core, but cause a critical fault on a core that doesn’t have AVX-512. The core won’t even know it’s an AVX-512 instruction until it comes time to decode it, and just throw an error when that happens. Not only this, but the scheduler has the right to move a thread when it needs to – if it moves a thread in the middle of an instruction stream, that can cause errors too. The processor could also move a thread to prevent thermal hotspots occurring, which will then cause a fault.

There could be a situation where the programmer can flag that their code has specific instructions. In a program with unique instructions, there’s very often a check that tries to detect support, in order to say to itself something like ‘AVX512 will work here!’. However, all modern software assumes a homogeneous processor – that all cores will support all of the same instructions.

It becomes a very chicken and egg problem, to a certain degree.

The only way out of this is that both processors in a hybrid CPU have to support the same instructions completely. This means that we end up with the worst of both worlds – only instructions supported by both can be enabled. This is the lowest common denominator of the two, and means that in Lakefield we lose support for AVX-512 on Sunny Cove, but also things like GFNI, ENCLV, and CLDEMOTE in Tremont (Tremont is actually rather progressive in its instruction support).

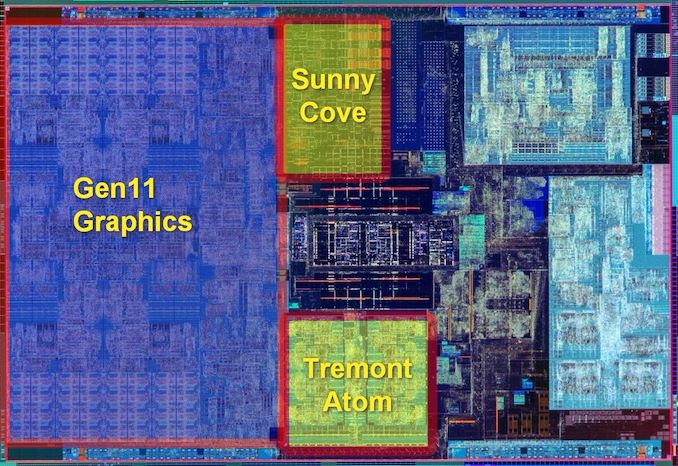

Knowing that Lakefield was going to have to take the lowest common denominator from the two core designs, Intel probably should physically removed the very bulky AVX-512 unit from the Sunny Cove core. Looking at the die shot, it's still there - there was some question going into the recent disclosures as to whether it would still be there, but Intel has stated on the record repeatedly that they removed it. The die shot of the compute silicon shows that not to be the case.

For x86 programmers doing instruction detection by code name or core family, this might have to change. In the smartphone world, where 4+4 processor designs are somewhat the norm, this lowest common denominator issue has essentially been universally adopted. There was some slight issue with a Samsung processor that had a non-unified cache setup, which ended up being rectified in firmware. But both sets of CPUs had to rely on lowest common denominator instructions.

221 Comments

View All Comments

Alistair - Thursday, July 2, 2020 - link

The only point of this is if it is dirt cheap. You don't pay a premium for 1 core and 4 atom cores. DOA. I'll take a 7nm 4 core Zen 2 laptop instead thanks.Make this a $50 CPU? Then I'm interested.

lmcd - Thursday, July 2, 2020 - link

I don't think it'll be $50 but if it is, I hope to see it on single-board computers. That'd be slick.serendip - Thursday, July 2, 2020 - link

It's meant for $1000 computers, not cheap sub-$500 devices. I wouldn't pay that much money for 4 Atom cores and a big core that sits around like an unwanted appendage.lmcd - Friday, July 3, 2020 - link

It's meant for $1000 tablets and ultralights, not traditional computer form factors.Glad you won't buy any smartphone then!

yeeeeman - Friday, July 3, 2020 - link

Qualcomm is fighting in the same space with 8cx for the same huge prices and that one doesn't even run x64 apps. This market wants very light laptops with very good battery life and LKF does just that, wherever you like it or not.Spunjji - Monday, July 6, 2020 - link

We'll see what the market actually wants when this launches. I have a strong suspicion that the market doesn't want the absolutely miserable performance/$ on offer here, even for the quoted battery life benefits, but I've been wrong before.justing6 - Thursday, July 2, 2020 - link

Amazing article! I learned so much about Lakefield and 3D stacking in general. The technology and engineering is really incredible, but as a consumer product it looks extremely lacking.I'm a proud owner and heavy user of a Surface Pro X, and the 8cx/SQ1 is generally "good enough" when running ARM workloads. Going to a 15W Intel chip that can turbo to 25-40W feels noticeably snappier, but when considering the SQ1 is 7W-15W it's really impressive. The 4+4 also allows for very good multitasking performance, it takes 10GB+ of heavy web browser tabs running on an external 3440x1440p display before it really feels like it starts to slow down.

However, that's when I live inside Chromium Edge running native ARM64 code. Performance is still laughable compared to Apple Silicon, especially for translated x86 code. On Geekbench the A12z on the dev kits running translated x86 code is just as fast as the 8cx running native ARM code, while the 8cx's performance really suffers when it has to run anything more complicated than a text editor or video player written in x86. I expect Apple's successor to the A12z to mop the floor with this whole market at the same price points, even for x86 code. On top of this, Apple has unparalleled leverage over developers by controlling its entire hardware stack. I wouldn't be surprised if in 2 years, all major MacOS applications will be compiled for native ARM64 code. On the other hand, Windows on ARM64 is almost 2 years old now and has very few natively compiled apps.

I really prefer Windows, but it's going to be a hard choice for me and a lot of consumers if a Lakefield/8cx ultraportable running Windows costs the same as an Apple ultraportable on Silicon that has somewhere around double the performance for the same price, while still keeping a thin and light design with great battery life. Intel and Qualcomm will be fighting for a distant second place.

jeremyshaw - Thursday, July 2, 2020 - link

So you're saying a desktop with desktop TDP outperforms a fanless tablet with tablet TDP?I do agree Apple has a stronger push (and will have to, since they are moving their entire ecosystem over, and anyone that isn't fully onboard will simply be left behind).

Qualcomm got too greedy, Nvidia doesn't want to fight in that market anymore (remember the original Surface tablets with Nvidia Tegra chips?), and nobody else is really eyeing the laptop/consumer segment outside of Apple.

Oh, well. Some people are propping up the PINE64 as if it's worth anything.

lmcd - Thursday, July 2, 2020 - link

No one's come up with an exciting killer app beyond video decoding for smartphones or tablets so might as well "prop up" the PINE64 :)Hopefully Broadcom will get interested in SoCs again with the work they're doing with the RPi foundation. ARM is going toward powerful CPU cores anyway so it shouldn't take an Apple-sized company to come up with competitive ARM designs.

justing6 - Thursday, July 2, 2020 - link

Considering an iPad Pro (a fanless tablet) running an A12z puts up Geekbench 5 scores 30% to 60% higher that the SQ1/8cx single/multi core respectively when running native ARM code, it's safe to say its a generation or two ahead of anything Qualcomm has. I also doubt they changed much with the TDP of the chip in the Arm transition Dev kit, if anything they made it less powerful by disabling the 4 small cores and leaving it only with the 4 large cores to give them more time to work out the big.LITTLE scheduling in MacOS. A 30% hit to performance when running x86 code sounds about right, its just that the chip has so much more raw power than the 8cx that it will be able to give users a much better experience.I'm not an Apple fan by any means, but I am a fan of innovation. Apple has been pretty stagnant on that front the past decade, but with the move to ARM they have a chance to really get ahead of the market like the Apple of the 2000s.