AMD Rome Second Generation EPYC Review: 2x 64-core Benchmarked

by Johan De Gelas on August 7, 2019 7:00 PM ESTJava Performance

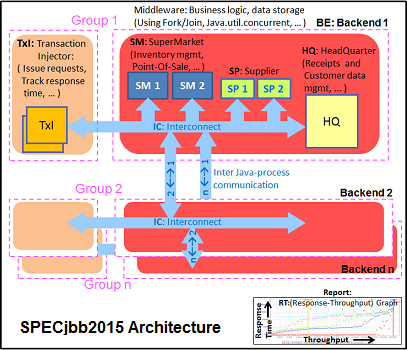

The SPECjbb 2015 benchmark has 'a usage model based on a world-wide supermarket company with an IT infrastructure that handles a mix of point-of-sale requests, online purchases, and data-mining operations'. It uses the latest Java 7 features and makes use of XML, compressed communication, and messaging with security.

We test SPECjbb with four groups of transaction injectors and backends. The reason why we use the "Multi JVM" test is that it is more realistic: multiple VMs on a server is a very common practice.

The Java version was OpenJDK 1.8.0_222. We used the older JDK 8 as the most recent JDK 11 has removed some deprecated JAVA EE modules that SPECJBB 1.01 needs. We applied relatively basic tuning to mimic real-world use, while aiming to fit everything inside a server with 128 GB of RAM:

We tested with huge pages on and off.

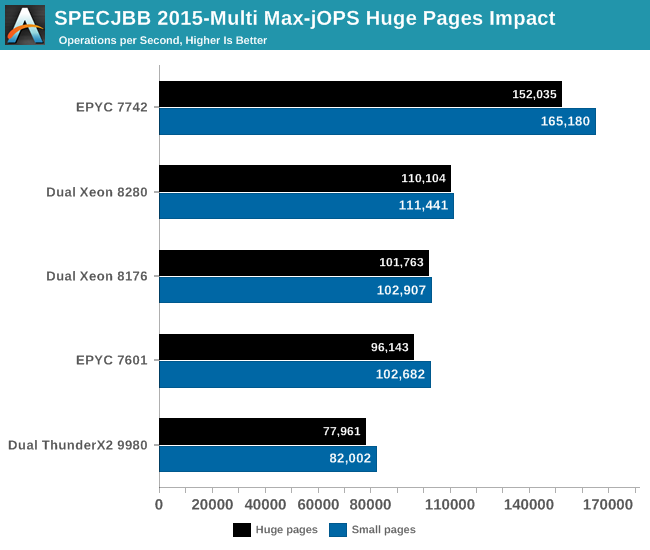

The graph below shows the maximum throughput numbers for our MultiJVM SPECJbb test. Since the test is almost identical to the one that we have used in our ThunderX2 review (JDK8 1.8.0_166), we also include Cavium's server CPU.

Ultimately we publish these numbers with a caveat: you should not compare this with the official published SPECJBB2015 numbers, because we run our test slightly differently to the official run specifications. We believe our numbers make as much sense (and maybe more) as most professionals users will not go for the last drop of performance. Using these ultra optimized settings can result in unrepeateable and hard to debug inconsistent errors - at best they will result in subpar performance as they are so very specific to SPECJBB. It is simply not worth it, a professional will stick with basic and reliable optimization in the real non-HPC world. In the HPC world, you simply rerun your job in case of an error. But in the rest of the enterprise world you just made a lot users very unhappy and created a lot of work for (hopefully) well paid employees.

The EPYC 7742 performance is excellent, outperforming the best available Intel Xeon by 48%.

Notice that the EPYC CPU performs better with small pages (4 KB) than with large ones (2 MB). AMD's small pages TLB are massive and as result page table walks (PTW) are seldom with large pages. If the number of PTW is already very low, you can not get much benefit from increasing the page size.

What about Cavium? Well, the 32-core ThunderX2 was baked with a 16 nm process technology. So do not discount them - Cavium has a unique opportunity as they move the the ThunderX3 to 7 nm FFN TSMC too.

To be fair to AMD, we can improve performance even higher by using numactl and binding the JVM to certain CPUs. However, you rarely want to that, and happily trade that extra performance for the flexibility of being able to start new JVMs when you need them and let the server deal with it. That is why you buy those servers with massive core counts. We are in the world of micro services, docker containers, not in the early years of 21st century.

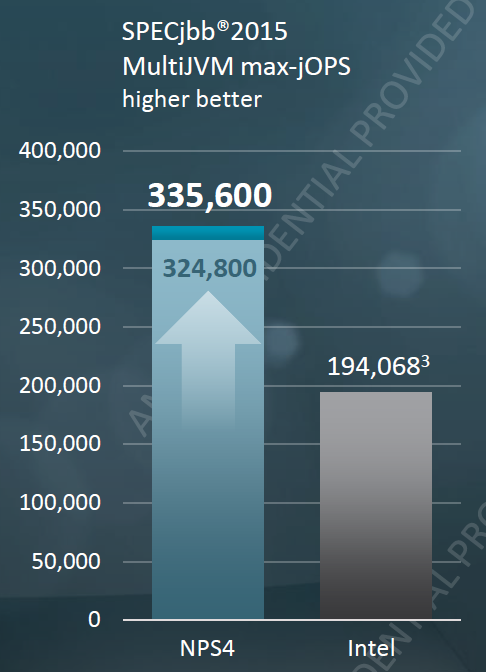

Ok, what if you do that anyway? AMD offered some numbers, while comparing them to the officialy published SPEJBB numbers of Lenovo ThinkSystem SR650 (Dual Intel 8280).

AMD achieves 335600 by using 4 JVM per node, binding them to "virtual NUMA nodes".

Just like Intel, AMD uses the Oracle JDK, but there is more to these record breaking numbers. A few tricks that only benchmarking people can use to boost SPECJBB:

- Disabling p-states and setting the OS to maximum performance (instead of balanced)

- Disabling memory protection (patrol scrub)

- Using older garbage collector because they happen to better at Specjbb

- Non-default kernel settings

- Aggressive java optimizations

- Disabling JVM statistics and monitoring

- ...

In summary, we don't think that it is wise to mimic these settings, but let us say that AMD's new EPYC 7742 is anywhere between 48 and 72% faster. And in both cases, that is significant!

180 Comments

View All Comments

AnonCPU - Friday, August 9, 2019 - link

The gain in hmmer on EPYC with GCC8 is not due to TAGE predictor.Hmmer gains a lot on EPYC only because of GCC8.

GCC8 vectorizer has been improved in GCC8 and hmmer gets vectorized heavily while it was not the case for GCC7. The same run on an Intel machine would have shown the same kind of improvement.

JohanAnandtech - Sunday, August 11, 2019 - link

Thanks, do you have a source for that? Interested in learning more!AnonCPU - Monday, August 12, 2019 - link

That should be due to the improvements on loop distribution:https://gcc.gnu.org/gcc-8/changes.html

"The classic loop nest optimization pass -ftree-loop-distribution has been improved and enabled by default at -O3 and above. It supports loop nest distribution in some restricted scenarios;"

There are also some references here in what was missing for hmmer vectorization in GCC some years ago:

https://gcc.gnu.org/ml/gcc/2017-03/msg00012.html

And a page where you can see that LLVM was missing (at least in 2015) a good loop distribution algo useful for hmmer:

https://www.phoronix.com/scan.php?page=news_item&a...

AnonCPU - Monday, August 12, 2019 - link

And more:https://community.arm.com/developer/tools-software...

just4U - Friday, August 9, 2019 - link

I guess the question to ask now is can they churn these puppies out like no tomorrow? Is the demand there? What about other Hardware? Motherboards and the like..Do they have 100 000 of these ready to go? The window of opportunity for AMD is always fleeting.. and if their going to capitalize on this they need to be able to put the product out there.

name99 - Friday, August 9, 2019 - link

No obvious reason why not. The chiplets are not large and TSMC ships 200 million Apple chips a year on essentially the same process. So yields should be there.Manufacturing the chiplet assembly also doesn't look any different from the Naples assembly (details differ, yes, but no new envelopes being pushed: no much higher frequency signals or denser traces -- the flip side to that is that there's scope there for some optimization come Milan...)

So it seems like there is nothing to obviously hold them back...

fallaha56 - Saturday, August 10, 2019 - link

Perhaps Hypertheading should be off on the Intel systems to better reflect eg Google’s reality / proper security standards now we know Intel isn’t secure?Targon - Monday, August 12, 2019 - link

That is why Google is going to be buying many Epyc based servers going forward. Mitigations do not mean a problem has been fixed.imaskar - Wednesday, August 14, 2019 - link

Why do you think AWS, GCP, Azure, etc. mitigated the vulnerabilities? They only patched Meltdown at most. All other things are too costly and hard to execute. They just don't care so much for your data. Too loose 2x cloud capacity for that? No way. And for security conscious serious customers they offer private clusters, so your workloads run on separate servers.ballsystemlord - Saturday, August 10, 2019 - link

Spelling and grammar errors:"This happened in almost every OS, and in some cases we saw reports that system administrators and others had to do quite a bit optimization work to get the best performance out of the EPYC 7001 series."

Missing "of":

"This happened in almost every OS, and in some cases we saw reports that system administrators and others had to do quite a bit of optimization work to get the best performance out of the EPYC 7001 series."

"...to us it is simply is ridiculous that Intel expect enterprise users to cough up another few thousand dollars per CPU for a model that supports 2 TB,..."

Excess "is" and missing "s":

"...to us it is simply ridiculous that Intel expects enterprise users to cough up another few thousand dollars per CPU for a model that supports 2 TB,..."

"Although the 225W TDP CPUs needs extra heatspipes and heatsinks, there are still running on air cooling..."

Excess "s" and incorrect "there",

"Although the 225W TDP CPUs need extra heatspipes and heatsinks, they're still running on air cooling..."

"The Intel L3-cache keeps latency consistingy low as long as you stay within the L3-cache."

"consistently" not "consistingy":

"The Intel L3-cache keeps latency consistently low as long as you stay within the L3-cache."

"For example keeping a large part of the index in the cache improve performance..."

Missing comma and missing "s" (you might also consider making cache plural, but you seem to be talking strictly about the L3):

"For example, keeping a large part of the index in the cache improves performance..."

"That is a real thing is shown by the fact that Intel states that the OLTP hammerDB runs 60% faster on a 28-core Intel Xeon 8280 than on EPYC 7601."

Missing "it":

"That it is a real thing is shown by the fact that Intel states that the OLTP hammerDB runs 60% faster on a 28-core Intel Xeon 8280 than on EPYC 7601."

In general, the beginning of the sentance appears quite poorly worded, how about:

"That L3 cache latency is a matter for concern is shown by the fact that Intel states that the OLTP hammerDB runs 60% faster on a 28-core Intel Xeon 8280 than on EPYC 7601."

"In NPS4, the NUMA domains are reported to software in such a way as it chiplets always access the near (2 channels) DRAM."

Missing "s":

"In NPS4, the NUMA domains are reported to software in such a way as its chiplets always access the near (2 channels) DRAM."

"The fact that the EPYC 7002 has higher DRAM bandwidth is clearly visible."

Wrong numbers (maybet you ment, series?):

"The fact that the EPYC 7742 has higher DRAM bandwidth is clearly visible."

"...but show very significant improvements on EPYC 7002."

Wrong numbers (maybet you ment, series?):

"...but show very significant improvements on EPYC 7742."

"Using older garbage collector because they happen to better at Specjbb"

Badly worded.

"Using an older garbage collector because it happens to be better at Specjbb"

"For those with little time: at the high end with socketed x86 CPUs, AMD offers you up to 50 to 100% higher performance while offering a 40% lower price."

"Up to" requires 1 metric, not 2. Try:

"For those with little time: at the high end with socketed x86 CPUs, AMD offers you from 50 up to 100% higher performance while offering a 40% lower price."