AMD Rome Second Generation EPYC Review: 2x 64-core Benchmarked

by Johan De Gelas on August 7, 2019 7:00 PM ESTJava Performance

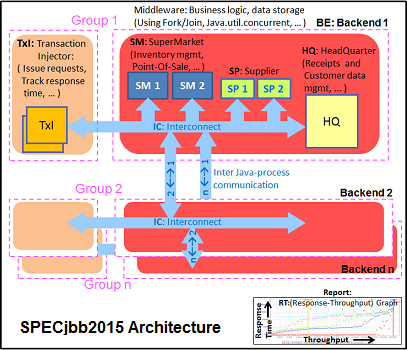

The SPECjbb 2015 benchmark has 'a usage model based on a world-wide supermarket company with an IT infrastructure that handles a mix of point-of-sale requests, online purchases, and data-mining operations'. It uses the latest Java 7 features and makes use of XML, compressed communication, and messaging with security.

We test SPECjbb with four groups of transaction injectors and backends. The reason why we use the "Multi JVM" test is that it is more realistic: multiple VMs on a server is a very common practice.

The Java version was OpenJDK 1.8.0_222. We used the older JDK 8 as the most recent JDK 11 has removed some deprecated JAVA EE modules that SPECJBB 1.01 needs. We applied relatively basic tuning to mimic real-world use, while aiming to fit everything inside a server with 128 GB of RAM:

We tested with huge pages on and off.

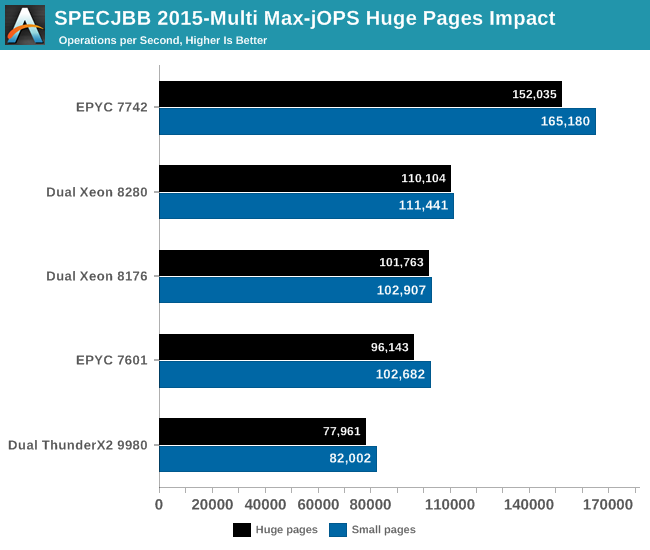

The graph below shows the maximum throughput numbers for our MultiJVM SPECJbb test. Since the test is almost identical to the one that we have used in our ThunderX2 review (JDK8 1.8.0_166), we also include Cavium's server CPU.

Ultimately we publish these numbers with a caveat: you should not compare this with the official published SPECJBB2015 numbers, because we run our test slightly differently to the official run specifications. We believe our numbers make as much sense (and maybe more) as most professionals users will not go for the last drop of performance. Using these ultra optimized settings can result in unrepeateable and hard to debug inconsistent errors - at best they will result in subpar performance as they are so very specific to SPECJBB. It is simply not worth it, a professional will stick with basic and reliable optimization in the real non-HPC world. In the HPC world, you simply rerun your job in case of an error. But in the rest of the enterprise world you just made a lot users very unhappy and created a lot of work for (hopefully) well paid employees.

The EPYC 7742 performance is excellent, outperforming the best available Intel Xeon by 48%.

Notice that the EPYC CPU performs better with small pages (4 KB) than with large ones (2 MB). AMD's small pages TLB are massive and as result page table walks (PTW) are seldom with large pages. If the number of PTW is already very low, you can not get much benefit from increasing the page size.

What about Cavium? Well, the 32-core ThunderX2 was baked with a 16 nm process technology. So do not discount them - Cavium has a unique opportunity as they move the the ThunderX3 to 7 nm FFN TSMC too.

To be fair to AMD, we can improve performance even higher by using numactl and binding the JVM to certain CPUs. However, you rarely want to that, and happily trade that extra performance for the flexibility of being able to start new JVMs when you need them and let the server deal with it. That is why you buy those servers with massive core counts. We are in the world of micro services, docker containers, not in the early years of 21st century.

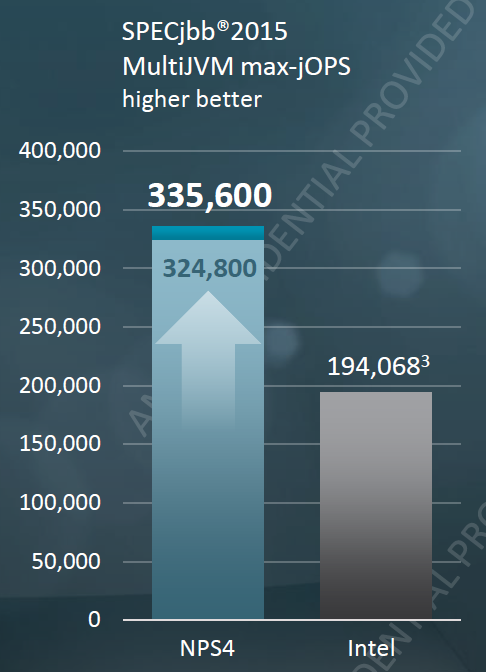

Ok, what if you do that anyway? AMD offered some numbers, while comparing them to the officialy published SPEJBB numbers of Lenovo ThinkSystem SR650 (Dual Intel 8280).

AMD achieves 335600 by using 4 JVM per node, binding them to "virtual NUMA nodes".

Just like Intel, AMD uses the Oracle JDK, but there is more to these record breaking numbers. A few tricks that only benchmarking people can use to boost SPECJBB:

- Disabling p-states and setting the OS to maximum performance (instead of balanced)

- Disabling memory protection (patrol scrub)

- Using older garbage collector because they happen to better at Specjbb

- Non-default kernel settings

- Aggressive java optimizations

- Disabling JVM statistics and monitoring

- ...

In summary, we don't think that it is wise to mimic these settings, but let us say that AMD's new EPYC 7742 is anywhere between 48 and 72% faster. And in both cases, that is significant!

180 Comments

View All Comments

ET - Thursday, August 8, 2019 - link

I found the EPYC 7262 the most interesting SKU. By L3 cache size, that would be 4 chiplets, each offering only 2 cores. From the specs it looks like AMD has no shortage of 4 core chiplets, but I didn't expect 2 core chiplets.Rudde - Friday, August 9, 2019 - link

L3 cache is shared inside a CCX (4 cores), which suggests that every CCX has only one core available, but 16MB of L3 cache. I.e. every core has private L3 cache.colonelclaw - Thursday, August 8, 2019 - link

But can it serve Crysis Battle Royale?shing3232 - Thursday, August 8, 2019 - link

I am pretty sure it can lolBigMamaInHouse - Thursday, August 8, 2019 - link

@ Johan De Gelas will u test @240W TDP config?JohanAnandtech - Thursday, August 8, 2019 - link

Elaborate your interest in that, as it is only tad higher than the official 225W TDP?BigMamaInHouse - Thursday, August 8, 2019 - link

AMD is offering 225W/240W TDP option in bios to it's customers and lets them to decide if to go with better cooling and use 240W or stay at 225W, even though it looks small increase- in reality it should offer almost 10% more power headroom to the CPU chiplets -if you consider that the 225W is including ~55W for I/O die, so extra 15W for the chiplets alone should offer nice bump in clocks.Gondalf - Thursday, August 8, 2019 - link

Strange.....the article forgot Cooper Lake, out in Q4 this year and at major customers (for revenue) from at least two quarters. Same applies to Ice Lake SP that is in evaluation to OEMs right now.From the article looks like Intel is sleeping, but it is not at all. Ummm maybe Intel is snobbing some guys here not giving samples to test?? or informations to share??

Bet Intel have to argue about the test suite or about compiler settings.........

JohanAnandtech - Thursday, August 8, 2019 - link

Because Cooper Lake is still "warmed up Skylake" (unless I missed something). AFAIK it is Cascade Lake with 8 mem channels - so the 56-core socketed will probably be still in the 350-400W TDP range. So the SPEC benchmarks will look better, but getting that kind of server running inside your datacenter does not look very attractive: complex and thus expensive boards, high cooling and power distribution required. Looks like a chip that wins back benchmarks, but is too much hassle to roll out in high quantities.Null666666 - Friday, August 9, 2019 - link

Wondering when 4-8 socket ice lake is due.