The Ice Lake Benchmark Preview: Inside Intel's 10nm

by Dr. Ian Cutress on August 1, 2019 9:00 AM EST- Posted in

- CPUs

- Intel

- GPUs

- 10nm

- Core

- Ice Lake

- Cannon Lake

- Sunny Cove

- 10th Gen Core

Conclusions

First of all, I must say that Intel offering us to test a reference system in advance of a launch is a very good thing indeed. It is not something that Intel has done often in the past – in fact the last time I remember it happening was with Broadwell, when Intel sampled us one of their mobile CRB (consumer reference board) systems for the 45W chip. Before that, Intel had a small attempt allowing the press to benchmark Conroe in 2006 with canned pre-provided benchmarks, which did not go down to well. So moving into this pre-testing regime gets some immediate kudos to those who approved the testing.

Intel’s Broadwell / Crystalwell Mobile CRB

Given that the Ice Lake platform is more geared up towards ultra-premium designs, the software development system we ended up testing was certainly a reasonable expectation and direction that these parts would go in. Of course, we only had the best part of nine hours to test, and giving us the option to test both 15W and 25W modes meant we had to pick and choose what tests we thought were relevant. My most prominent feedback to Intel would be to give us two days to test next time, as it allows us to sit on our data after day one and decide what to do next. It was clear that some of the press in attendance only needed a day (or half a day), but for what we do at AT, then two days would be better.

As for Ice Lake itself, our results lean towards Ice Lake outperforming Whiskey Lake, if only by a small margin.

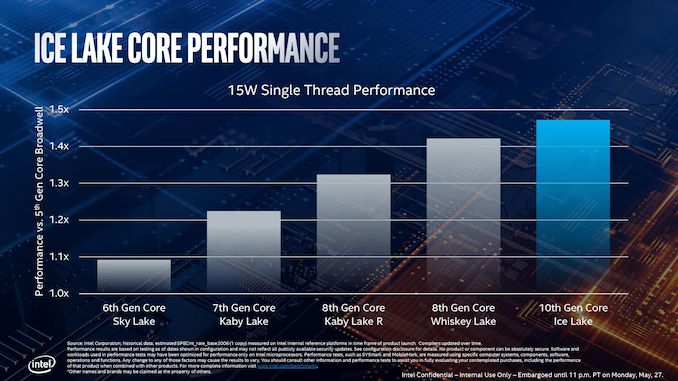

To preface this, I want to recall a graph that Intel showed off at Computex:

This graph shows the single thread performance of Skylake and beyond, compared to 5th Gen Broadwell hardware. Right at the very end, we see Whiskey Lake performing +42% above Broadwell, and Ice Lake performing +47% above Broadwell. A quick calculation of 1.47/1.42 means that even Intel is only predicting an absolute gain of ~3.5% for Ice Lake over current generation systems.

The reason why the difference is so small is because of IPC and frequency. Intel is touting a median IPC advantage on the new Sunny Cove cores of +18% against Skylake. That isn’t something we were able to test in the short time we had with the system, but +18% should provide a healthy bump – we actually see a number of key microarchitectural improvements bubble up through in our SPEC testing.

But at the same time, the frequency has decreased – our Whiskey Lake Huawei Matebook system was +500 MHz on the base frequency (+38%), and +700 MHz on the turbo frequency (+18%). If it were not for the vast increase in memory speed, moving from LPDDR3-2133 to LPDDR4X-3733, one might have predicted that the Core i7-1065G7 Ice Lake processor and the Core i7-8565U Whisky Lake processor would have performed equally.

The question here then becomes whether you prefer IPC or frequency. For instruction limited tasks, that answer should be IPC. For critical path limited tasks, you nominally require frequency. All this gets muddled a bit with the increased memory frequency, but with higher IPC at lower frequency, you should arguably be more power efficient as well, leading to longer battery life. At iso-performance between Ice and Whiskey, considering no other factors like price, I would choose Ice.

Intel has made a number of improvements to a chunk of the instruction set that should work well for users, however the new bigger cache design has added a bit of latency there, which ends up being a bit of give and take with cache hits and misses.

Of course, the one area where Ice Lake excels in is graphics. Moving from 24 EUs to 64 EUs, plus an increase in memory bandwidth to >50 GB/s, makes for some easy reading. It gets even better in 25W mode, for games that are CPU limited, but still don’t expect to be tackling AAA games at high resolutions. Despite Ice Lake being focused on the ultra-premium >1080p resolution market, you will still be gaming at 720p or 1080p at best here.

The other alternative is to attach a Thunderbolt 3 external graphics card. If there’s one really good add-in to Ice Lake, aside from the graphics uplift, it’s the inclusion of up to four TB3 ports as part of the CPU silicon. If and when the TB3 controllers get a lot cheaper on the device side, this should really help accelerate a high-performance standard here.

We should also talk about AVX-512 – Intel is in a position right now where including it in the chip uses a good amount of die area, and the software ecosystem hasn’t yet adopted it. By advertising speed-ups like DLBoost, the company is hoping to entice developers to work with AVX-512 in mind, and improve a number of machine learning applications for consumer processors. The other side there is what sort of consumer applications need machine learning that isn’t already done in the cloud. It’s a bit of a catch-22, but in our own testing, the AVX-512 does provide a significant speed-up. However, given Intel’s recent mantra of testing for user experience, it will be interesting to see how hammering the AVX-512 unit meshes with that mantra.

The scope of when these Ice Lake processors are coming to market, and how much, is still a question mark. Intel states that we’ll see Ice Lake in the market for the holiday season (i.e. Christmas), however we have a number of trade shows around the corner, such as IFA in September, where me might start seeing some companies start to show off their designs. We also know that Intel plans to release Comet Lake mobile processors sometime this year, on the old 14nm process and old Skylake-based microarchitecture, but at higher frequencies, so it will be interesting to see how they compete.

Final Thoughts

I’m glad to have tested Ice Lake. It’s a shame that we only had a day to test, because I could have spent a week testing that system. Increasing IPC is the best problem to solve, even if it gives similar performance due to a lower frequency, but hopefully the knock on effect here will be better battery life for users at the same performance. Once we get some systems in to test that battery life, and Project Athena’s requirement of 16+ hours comes to the front, I think we’ll see the best examples of Ice Lake shine through.

261 Comments

View All Comments

tamalero - Monday, August 5, 2019 - link

the 3d mark VRS test graph is very confusing.MASSAMKULABOX - Tuesday, August 6, 2019 - link

These chips are priced quite high esp the i3's the Dualcore is outrageous (20$ discount for half the cores and threads?).They will only sell in limited qtys at such high prices . Bring on the 14nm equiv at sane prices.what discrete gfx does the IGPU equate to? gt1030 vs 2200g vs 3400ge??

Zhentar - Tuesday, August 6, 2019 - link

The bit per cycle throughput of REP STOS is really only half of the picture - the startup latency matters a lot too! On my Skylake, I've measured a minimum latency of 29 cycles* (any REP STOS from 1 byte to 128 bytes takes 29 cycle, then it starts going up from there). Some compilers make heavy use of it even for small stores/copies (VC6, first and foremost, but also the .NET JIT for stack zeroing), so it can be pretty important to performance in some scenarios.*I am no Agner Fog... nor anywhere close to him, this measurement should be taken with a grain of salt ;-)

ballsystemlord - Wednesday, August 7, 2019 - link

@Ian

Sunny Cove SIMD chart and others have many asterisks, why?

"POPCNT Microcode 50% faster than SW (under L1-D size)"

What does this mean? The CPU uses microcode and HW, not SW, AFAIK, much less use it to implement the POPCNT instruction.

ballsystemlord - Thursday, August 8, 2019 - link

Spelling and grammar errors:Insert: I've been commenting corrections for at least 1 year now, if you guys want me to change the format, or have any request regarding phrasing, etc., just ask. Thanks for your work!

"L3 latencies look similar, however we'll dwell into that just in a bit."

I think you ment delve:

"L3 latencies look similar, however we'll delve into that just in a bit."

"IPC increases against the mobile Skylake are 33 and 38% in the integer and fp suites, though we also have to keep in d mind these figures go beyond just the Sunny Cove architecture and also include improvements through the new LPDDR4X memory controllers."

Missing percent sign and stray "d".

"IPC increases against the mobile Skylake are 33% and 38% in the integer and fp suites, though we also have to keep in mind these figures go beyond just the Sunny Cove architecture and also include improvements through the new LPDDR4X memory controllers."

"...which did not go down to well."

You mean "too" not "to":

"...which did not go down too well."

"...we actually see a number of key microarchitectural improvements bubble up through in our SPEC testing."

Excess "in":

"...we actually see a number of key microarchitectural improvements bubble up through our SPEC testing."

alysdexia - Thursday, November 28, 2019 - link

I think you mean Baalsystemlord or Bàqhàlsýstemlord.Grammar is a barbarism of ghrammatics, another word for composition or handwriting, font, format, spacing, the looks, whereas you meant diction/lecsis or register, vocabulary, declension, placement, spelling, the meaning.

you guys -> ye

nils_ - Monday, August 19, 2019 - link

I noticed on Intel Ark that Ice Lake CPUs do not have TSX instructions enabled / available. THis is interesting, since I believe TSX has also been used for some of the spectre attacks.ikjadoon - Thursday, September 12, 2019 - link

On 'Gaming Results (15W and 25W)', the graph is colored incorrectly. "On" and "Off" have the same color...and the legend colors are somehow not related to the graphic?