AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome

by Dr. Ian Cutress on June 10, 2019 7:22 PM EST- Posted in

- CPUs

- AMD

- Ryzen

- EPYC

- Infinity Fabric

- PCIe 4.0

- Zen 2

- Rome

- Ryzen 3000

- Ryzen 3rd Gen

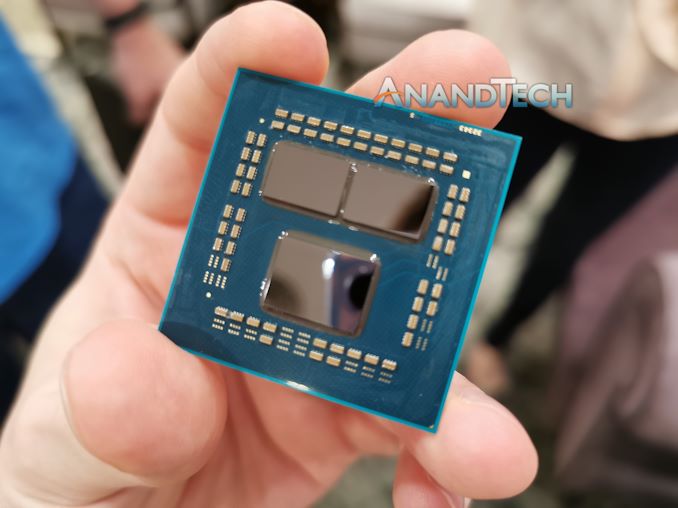

Building a core like Zen 2 requires more than just building a core. The interplay between the core, the SoC design, and then the platform requires different internal teams to come together to create a level of synergy that working separately lacks. What AMD has done with the chiplet design and Zen 2 shows great promise, not only in taking advantage of smaller process nodes, but also driving one path on the future of compute.

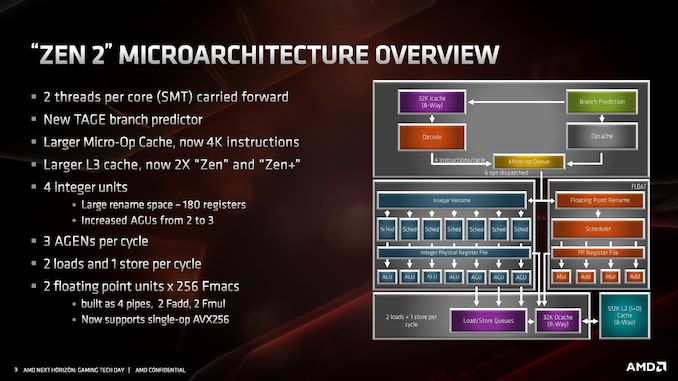

When going down a process node, the main advantages are lower power. That can be taken in a few ways: lower power for operation at the same performance, or more power budget to do more. We see this with core designs over time: as more power budget is opened or different units within the core get more efficient, that extra power is used to drive cores wider, hopefully increasing raw instruction rate. It’s not an easy equation to solve, as there are many trade-offs: one such example in the Zen 2 core is the relationship between the reduced L1 I-cache that has allowed AMD to double the micro-op cache, which overall AMD expects to help with performance and power. Going into the minutae of what might be possible, at least at a high level, is like playing with Lego for these engineers.

All that being said, Zen 2 looks a lot like Zen. It is part of the same family, which means it looks very similar. What AMD has done with the platform, enabling PCIe 4.0, and putting the design in place to rid the server processors of the NUMA-like environment is going to help AMD in the long run. The outlook is good for AMD here, depending on how high it can drive the frequency of the server parts, but Zen 2 plus Rome is going to remove a good number of questions that customers on the fence had about Zen.

Overall AMD has quoted a +15% core performance improvement with Zen 2 over Zen+. With the core changes, at a high level, that certainly looks feasible. Users focused on performance will love the new 16-core Ryzen 9 3950X, while the processor seems nice an efficient at 105W, so it will be interesting so see what happens at lower power. We're also anticipating a very strong Rome launch here over the next few months, especially with features like double FP performance and QoS, and the raw multithreading performance of 64 cores is going to be an interesting disruptor to the market, especially if priced effectively. We’ll be getting the hardware on hand here soon to present our findings when the processors are launched on July 7th.

216 Comments

View All Comments

scineram - Wednesday, June 12, 2019 - link

No.Xyler94 - Thursday, June 13, 2019 - link

YesXyler94 - Thursday, June 13, 2019 - link

If he meant 2700x, of course. Darn misreading :Pnevcairiel - Monday, June 10, 2019 - link

A quick note. AVX2 is actually primarily Integer. AVX1 (or just AVX) is 256-bit floating point. The article often refers to "full AVX2 support", which isn't necessarily wrong, but Zen2 also adds full AVX support equally.NikosD - Saturday, June 15, 2019 - link

AVX256 is both integer and floating point because it includes AVX2 FMA which doubles floating point capability compared to AVX1NikosD - Saturday, June 15, 2019 - link

AVX256 was a typo, I meant AVX2 obviously.eastcoast_pete - Monday, June 10, 2019 - link

Thanks Ian? Two questions: what is the official memory bandwidth for the consumer chips? (Sounds like they remain dual channel) and: Any words on relative performance of AMD's AVX 2 implementation vs. Intel's AVX 512 with software that can use either?emn13 - Tuesday, June 11, 2019 - link

AVX-512 is a really misleading name; the interesting... bits... aren't the 512-bit width, but the dramatically increased flexibility. All kinds of operations are now maskable and better reshufflable, and where specific sub-segements of the vector were used, they're now sometimes usable at 1bit granularity (whereas previously that was greater).Assuming x86 sticks around for high-perf computing long enough for compilers to be able to automatically leverage it and then for most software to use it, AVX-512 is likely to be quite the game changer - but given intel's super-slow rollout so far, and AFAIK no AMD support... that's going to take a while.

Which is all a long-winded way to say that you might well expect AMDs AVX2 implementation to be not all that much slower than intel's 512 when executing code that's essentially AVX2-esque (because intel drops the frequency, so won't get the full factor 2 speedup), but AVX-512 has the potential to be *much* faster than that, because the win isn't actually in vector-width.

GreenReaper - Tuesday, June 11, 2019 - link

Intel's own product segmentation has caused it to lose its first-mover advantage here. System software aside, there's little point in most developers seeking to use instructions that most of their users will not have (and which they themselves may not have). By the time software does support it, AMD is likely to have it. And of course an increasing number of developers will be pouncing on Zen 2 thanks to fast, cheap cores that they can use to compile on...HStewart - Tuesday, June 11, 2019 - link

Intel only had AVX 512 versions in Xeon and Xeon derive chips, but the with Ice Lake ( don't really count Canon Lake test run ) AVX 512 will hit main stream starting with in a month and 2020 should be fully roll out.As for AMD AVX 2 is true 256 bit, the last I heard is that it actually like dual 128 bit unless they change it in Zen 2. I serious doubt AMD AVX 2 implement is going to any much different that Intel AVX 2 and AVX 512 is a total different beast.

It funny years ago we heard the same thing about 64 bit in x86 instructions, and now we here in 512 bit AVX.

As for as AMD support for AVX 512, that does not matter much since Intel is coming out with AVX 512 in full line over next year or so.

But keep in mind unlike normal x86 instruction, AVX is kind of specialize with vectorize processing, I know with Video processing like Power Director this was a deciding factor earlier for it.,