AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome

by Dr. Ian Cutress on June 10, 2019 7:22 PM EST- Posted in

- CPUs

- AMD

- Ryzen

- EPYC

- Infinity Fabric

- PCIe 4.0

- Zen 2

- Rome

- Ryzen 3000

- Ryzen 3rd Gen

Cache and Infinity Fabric

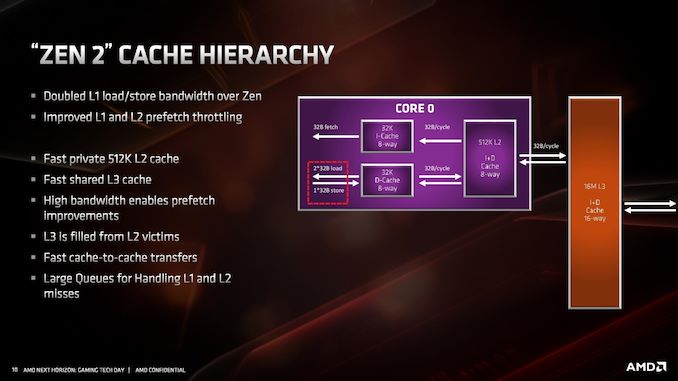

If it hasn’t been hammered in already, the big change in the cache is the L1 instruction cache which has been reduced from 64 KB to 32 KB, but the associativity has increased from 4-way to 8-way. This change enabled AMD to increase the size of the micro-op cache from 2K entry to 4K entry, and AMD felt that this gave a better performance balance with how modern workloads are evolving.

The L1-D cache is still 32KB 8-way, while the L2 cache is still 512KB 8-way. The L3 cache, which is a non-inclusive cache (compared to the L2 inclusive cache), has now doubled in size to 16 MB per core complex, up from 8 MB. AMD manages its L3 by sharing a 16MB block per CCX, rather than enabling access to any L3 from any core.

Because of the increase in size of the L3, latency has increased slightly. L1 is still 4-cycle, L2 is still 12-cycle, but L3 has increased from ~35 cycle to ~40 cycle (this is a characteristic of larger caches, they end up being slightly slower latency; it’s an interesting trade off to measure). AMD has stated that it has increased the size of the queues handling L1 and L2 misses, although hasn’t elaborated as to how big they now are.

Infinity Fabric

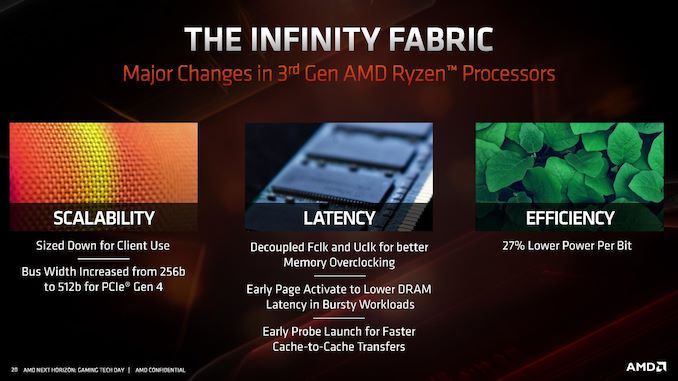

With the move to Zen 2, we also move to the second generation of Infinity Fabric. One of the major updates with IF2 is the support of PCIe 4.0, and thus the increase of the bus width from 256-bit to 512-bit.

Overall efficiency of IF2 has improved 27% according to AMD, leading to a lower power per bit. As we move to more IF links in EPYC, this will become very important as data is transferred from chiplet to IO die.

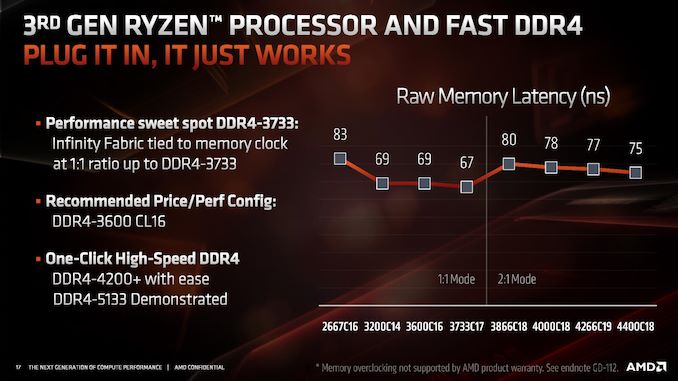

One of the features of IF2 is that the clock has been decoupled from the main DRAM clock. In Zen and Zen+, the IF frequency was coupled to the DRAM frequency, which led to some interesting scenarios where the memory could go a lot faster but the limitations in the IF meant that they were both limited by the lock-step nature of the clock. For Zen 2, AMD has introduced ratios to the IF2, enabling a 1:1 normal ratio or a 2:1 ratio that reduces the IF2 clock in half.

This ratio should automatically come into play around DDR4-3600 or DDR4-3800, but it does mean that IF2 clock does reduce in half, which has a knock on effect with respect to bandwidth. It should be noted that even if the DRAM frequency is high, having a slower IF frequency will likely limit the raw performance gain from that faster memory. AMD recommends keeping the ratio at a 1:1 around DDR4-3600, and instead optimizing sub-timings at that speed.

216 Comments

View All Comments

fmcjw - Tuesday, June 11, 2019 - link

All good and fine, but I want Zen 2 and 7nm on my laptop. If they aren't announcing it today, products aren't gonna ship by holiday 2019, and most consumers will end up buying 10nm Intel devices. Missed chance.mode_13h - Tuesday, June 11, 2019 - link

Eh, they have perfectly good 12 nm laptop SoCs. 7 nm would've been nice, but it's hard to do everything at once.levizx - Tuesday, June 11, 2019 - link

Nope, those 12nm APUs have worse battery life (than current 8th Gen) and no TB3/USB4 support. I can't think of a reason where I would choose Ryzen 3xxxU over Ice Lakemode_13h - Tuesday, June 11, 2019 - link

Do price & availability count?Xyler94 - Tuesday, June 11, 2019 - link

Misleading remarks. Huawei was able to make a Ryzen APU have better battery life than an 8th gen processor. TB3 and USB4 aren't readily used mainstream yet. Heck USB-C hasn't even caught on yet.Currently laptop makers aren't optimizing AMD's CPU, that's just the fact.

Cooe - Wednesday, June 12, 2019 - link

This is mostly nonsense. Performance AND battery life for Ryzen Mobile 2nd Gen is extremely close to Intel's current 8th & 9th gen 4-core parts. And until Ice Lake is a real thing that you can actually buy, Ryzen still has a major value advantage + far better iGPU performance. Ice Lake also isn't really any faster CPU wise than Whiskey Lake, because despite increasing IPC by +18%, clock-speeds were dropped from 4.8 to 4.1GHz, or about -16%, erasing nearly all those gains.fmcjw - Tuesday, June 11, 2019 - link

Yeah, I get that they still need time to get the GPU down to 7nm, so they pushed it back to focus on the CPU for desktop (where performance per watt matters much less than server or mobile). But the silence is not reassuring, and mobile-wise, Zen is still inferior to Intel, maybe not performance-wise as Huawei demonstrates with its Matebook, but definitely battery-wise because of the more powerful GPU.scineram - Tuesday, June 11, 2019 - link

Nobody is going to buy Shintel vaporware. Or only very few.The_Assimilator - Tuesday, June 11, 2019 - link

Please edit the table on page 1 to combine the rows with identical values into a single row (e.g. the RAM speed). Also edit the 3950X price to have a ? after it as it's not yet confirmed.jfmonty2 - Tuesday, June 11, 2019 - link

The 3950X price is most definitely confirmed; Lisa Su said it loud and clear (and showed it on the slide) in AMD's E3 presentation yesterday: https://www.youtube.com/watch?v=yxPBXNuX6Xs&t=...