Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86

by Dr. Ian Cutress on December 12, 2018 9:00 AM EST- Posted in

- CPUs

- Memory

- Intel

- GPUs

- DRAM

- Architecture

- Microarchitecture

- Xe

The Next Generation Gen11 Graphics: Playable Games and Adaptive Sync!

Some of the first words out of the mouth of Raja Koduri about graphics is that Intel has a duty to its one billion customers with integrated graphics to give them something that is useful, and that it is time for Intel to provide graphics which people can actually play games on. Given his expertise on the matter, it shouldn’t sound too far-fetched: more people play games than ever before, and these users want to play no matter what their hardware. To that end, Raja stated that Gen11 graphics is the first step in a new graphics policy to provide the performance and features to let gamers play the most popular games, no matter what implementation.

Gen11: Intel’s first GT2 TFLOPS Graphics

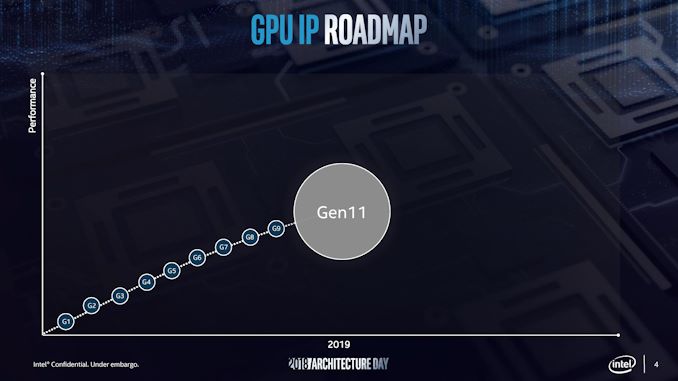

In 2015, Intel launched the Skylake processor with Gen9 integrated graphics. Rather than moving straight to Gen10 the next time around, we were given Gen 9.5 in both Kaby Lake and Coffee Lake, which supposedly draw features from what would have been Gen 10. Actually, the graphics for Intel’s failed 10nm Cannon Lake chip were meant to be called Gen10, however Intel never released a Cannon Lake processor with working integrated graphics, and because Gen11 goes above and beyond what Gen10 would have been, we’ve gone straight to Gen11. Make sense? Well Intel didn’t even bother to acknowledge Gen10 in its history graph:

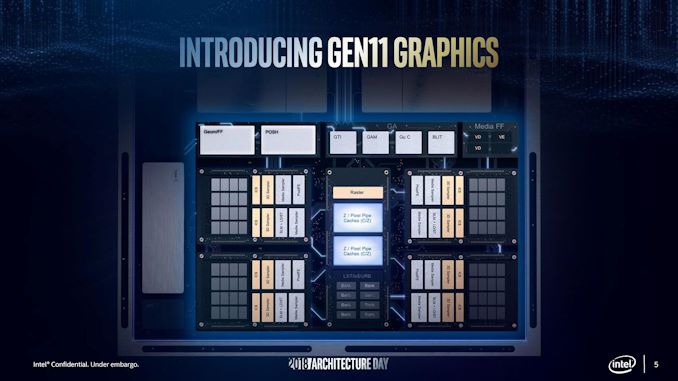

We will see Gen11 graphics being paired with Sunny Cove cores on 10nm sometime in 2019 according to the roadmaps. However rather than give a detailed architecture layout for the new product, we instead were given a rather high level diagram.

From here we can deduce a few things. We were told that this configuration is the GT2 config, which will have 64 execution units, up from 24 in Gen9.5. These 64 EUs are split into four slices, with each slice being made of two sub-slices of 8 EUs a piece. Each sub-slice will have an instruction cache and a 3D sampler, while the bigger slice gets two media samplers, a PixelFE, and additional load/store hardware. Intel lists Gen11 targeting efficiency, performance, advanced 3D and media capabilities, and a better gaming experience.

Intel didn’t go into too much detail regarding how the EUs are at higher performance, however the company did say that the FPU interfaces inside the EU are redesigned and it still has support for fast (2x) FP16 performance as seen in Gen9.5. Each EU will support seven threads as before, which means that the entire GT2 design will essentially have 512 concurrent pipelines. In order to help feed these pipes, Intel states that it has redesigned the memory interface, as well as increasing the L3 cache of the GPU to 3 MB, a 4x increase over Gen9.5, and it is now a separate block in the unslice section of the GPU.

Other features include tile-based rendering, which Intel stated the graphics hardware will be able to enable/disable on a render pass basis. This will make Intel the final member of the PC GPU vendor community to implement this, following NVIDIA in 2014 and AMD in 2017. While not a panacea to all performance woes, a good tile rendering setup plays well to the bandwidth limitations of an integrated GPU. Meanwhile Intel's lossless memory compression has also improved, with Intel listing a best case performance boost of 10% or a geometric mean boost of 4%. The GTI interface now supports 64 bytes per clock read and write to increase throughput, which works with the better memory interface.

Coarse Pixel Shading, Intel's implementation of multi-rate shading and similar in scope to NVIDIA’s own Variable Pixel Shading, is also supported. This allows the GPU to reduce the amount of total shading work required by shading some pixels on a less than 1:1 basis. Intel showed two demos for CPS, where pixel shading was reduced either as a function of object distance from camera (so you do less work when things are further away), or reduced as a function of how close the object is to the center of the screen, designed to help features like foveated rendering for VR. With a 2x2 pixel stencil applied – meaning only one pixel shading operation was done per block of 4 pixels – Intel stated a ~30% increase in frame rates in supported games. Unfortunately this needs to be applied on a game-by-game basis in order to prevent significant image quality losses, so the performance gains won't be immediate or universal.

For the media block, Intel says that the Gen11 design includes a ground up HEVC encoder design, with high quality encode and decode support. Intel cited the fact that its media fixed function units are already used in the datacenter for video processing, and home users can take advantage of the same hardware. Intel also stated that by using parallel decoders it can either support concurrent video streams or they can be combined to support a single large stream, and this scalable design will allow future hardware to push the peak resolutions up to 8K and beyond.

The highlight of the display engine is support for Adaptive Sync technologies. We were told that it was announced back at the launch of Skylake, but now it is finally ready to go into Intel’s integrated graphics. This goes in hand with HDR support due to its high-precision data path.

One thing in this presentation that Intel didn’t mention directly is that Gen11 graphics would appear to have Type-C video output support, potentially indicating that Intel has integrated the necessary mux into the chipset itself, removing another IC from the motherboard design.

148 Comments

View All Comments

jjj - Wednesday, December 12, 2018 - link

And you acted like someone clueless that has put all his savings in Intel's stock based on brad, "Large revenue stream" LOL, you don't know anything about the product, the target market, about the packaging solution but you get all wet.Anyway, took a look at the slides and they do actually provide some relevant details that yuo seem to not notice. They say face-face, bump pitch at 36um and bump density at 828.mm2.

Spunjji - Thursday, December 13, 2018 - link

Your comments are unnecessarily aggressive, dripping with unwarranted confidence and really unpleasant to read. Please spend more time offline.jjj - Wednesday, December 12, 2018 - link

For the hell of it, I'll add this IMEC slide (different versions out there but this one was the first i could find)http://www.techdesignforums.com/practice/files/201...

iwod - Thursday, December 13, 2018 - link

ignore the trolls.Raqia - Wednesday, December 12, 2018 - link

That's a nice fan on their fanless SoC design. It seems like Intel is really playing catch up with their ultra mobile designs (with a power envelope that's likely still above phones) fabbed on a late 10nm design and only now doing things like heterogeneous cores and PoP memory that the AX and Snapdragons have been doing for a few years now.I wonder what portion of that block diagram's compute reside on the P1222 (which looks bigger die space wise on their diagram than the P1274 but may pack fewer transistors.) They mentioned IO but it wouldn't make too much performance sense for caches and coherency to segregate the Big/Little cores onto separate dies, so it likely contains the ISPs and memory controllers. Where the GPU is located is another interesting question and no LTE modem can be seen on the block diagram. This is also likely to have higher packaging cost and worse integration than the AX, Kirins, PXX's or Snapdragons.

A5 - Wednesday, December 12, 2018 - link

Dev boards have fans because they don't have a chassis to sink heat into. If it's like every other dev board I've used, it is probably a 8k RPM screamer, too.The_Assimilator - Wednesday, December 12, 2018 - link

Seems like you failed to read page 4: "These were development systems with these funky looking heatsinks and loud fans to ensure there was no thermal throttling."Raqia - Wednesday, December 12, 2018 - link

My comment was in reference to their new Atom lineup which are supposed to be fanless, not Sunny Cove which operates in a much higher power envelope. Surely they could use a larger passive cooling unit to demonstrate what's supposed to be a key feature of that product; my other point is that Intel's aiming for something later next year that seems much less advanced than what Apple, Huawei, Mediatek, and Qualcomm already have in production today.The_Assimilator - Thursday, December 13, 2018 - link

And, again, the Fovoros setup was a demo board in the open air, not a production chip inside a device designed around dissipating the heat it outputs.Spunjji - Thursday, December 13, 2018 - link

If that's what you took from that part of the presentation then I feel you missed the point. What Intel are doing in terms of chip layout is something none of the companies you mentioned are able to do yet, which is the fundamental point here - whether it results in a useful product is another matter entirely, but it's still fascinating and not same-same.To back up the other people who responded to you, again, the fan is irrelevant. It's a dev board.