Intel Architecture Day 2021: Alder Lake, Golden Cove, and Gracemont Detailed

by Dr. Ian Cutress & Andrei Frumusanu on August 19, 2021 9:00 AM ESTConclusions

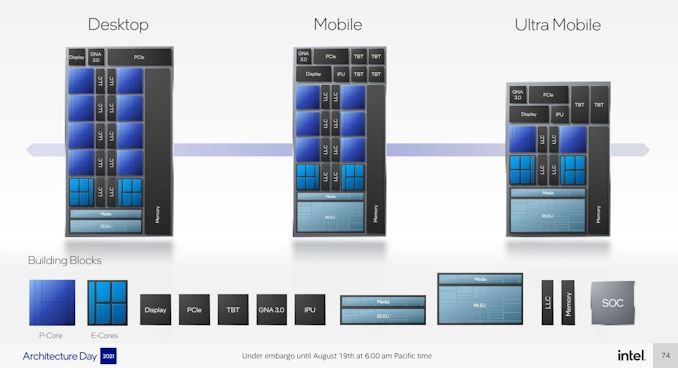

Alder Lake is set to come to market for both desktop and mobile, and we’re expecting the desktop hardware to start to appear by the end of the year – perhaps a little later for the rest of the family, but all-in-all we expect Intel is experiencing some serious squeaky bum time regarding how all the pieces will fit in place at that launch. The two main critical factors are operating systems and memory.

Because Alder Lake is Intel’s first full-stack attempt to commercialize a hybrid design, it has had to work closely with Microsoft to enable all the features it needs to make managing a hybrid core design properly beneficial to users. Intel’s new Thread Director Technology couples an integrated microcontroller per P-core and a new API for Windows 11 such that the scheduler in the operating system can take hints about the workflow on the core at a super fine granularity – every 30 microseconds or so. With information about what each thread is doing (from heavy AVX2 down to spin lock idling), the OS can react when a new thread needs performance, and choose which threads need to be relegated down to the E-core or as a hyperthread (which is classified as slower than an E-core).

When I first learned Alder Lake was going to be a hybrid design, I was perhaps one of the most skeptical users about how it was going to work, especially with some of the limits of Windows 10. At this point today however, with the explanations I have from Intel, I’m more confident than not that they’ve done it right. Some side off-the-record conversations I have had have only bolstered the idea that Microsoft has done everything Intel has asked, and users will need Windows 11 to get that benefit. Windows 10 still has some Hardware Guided Scheduling, but it’s akin to only knowing half the story. The only question is whether Windows 11 will be fully ready by the time Alder Lake comes to market.

For memory, as a core design, Alder Lake will have support for DDR4 and DDR5, however only one can be used at any given time. Systems will have to be designed for one or the other – Intel will state that by offering both, OEMs will have the opportunity to use the right memory at the right time for the right cost, however the push to full DDR5 would simplify the platform a lot more. We’re starting to see DDR5 come to the consumer market, but not in any volume that makes any consumer sense – market research firms expect the market to be 10% DDR5 by the end of 2022, which means that consumers might have to be stay with DDR4 for a while, and vendors will have to choose whether to bundle DDR5 with their systems. Either way, there’s no easy answer to the question ‘what memory should I use with Alder Lake’.

Through The Cores and The Atoms

From a design perspective, both the P-core and E-core are showcasing substantial improvements to their designs compared to previous generations.

The new Golden Cove core has upgraded the front-end decoder, which has been a sticking point for analysis of previous Cove and Lake cores. The exact details of how they operate are still being kept under wraps, but having a 6-wide variable length decoder is going to be an interesting talking point against 8-wide fixed-length decoders in the market and which one is better. The Golden Cove core also has very solid IPC figure gains, Intel saying 19%, although the fact there are some regressions is interesting. Intel did compare Golden Cove to Cypress Cove, the backported desktop core, rather than Willow Cove, the Tiger Lake core, which would have been a more apt comparison given that our testing shows Willow Cove slightly ahead. But still, around 19% is a good figure. Andrei highlights in his analysis that the move from a 10-wide to a 12-wide disaggregated execution back-end should be a good part of that performance, and that most core designs that go down this route end up being good.

However, for Gracemont, Intel has taken that concept to the extreme. Having 17 execution ports allows Intel to clock-gate each port when not in use, and even when you couple that with a smaller 5-wide allocation dispatch and 8-wide retire, it means that without specific code to keep all 17 ports fed, a good number are likely to be disabled, saving power. The performance numbers Intel provided were somewhat insane for Gracemont, suggesting +8% performance over Skylake at peak power, or a variety of 40% ST perf/power or 80% MT perf/power against Skylake. If Gracemont is truly a Skylake-beating architecture, then where have you been! I’m advocating for a 64-core HEDT chip tomorrow.

One harsh criticism Intel is going to get back is dropping AVX-512 for this generation. For the talk we had about ‘no transistor left behind’, Alder Lake dropped it hard. That’s nothing to say if the functionality will come back later, but if rumors are believed and Zen 4 has some AVX-512 support, we might be in a situation where the only latest consumer hardware on the market supporting AVX-512 is from AMD. That would be a turn-up. But AMD’s support is just a rumor, and really if Intel wants to push AVX-512 again, it will have a Sisyphean task to convince everyone it’s what the industry needs.

Where We Go From Here

There are still some unanswered questions as to the Alder Lake design, and stuff that we will test when we get the hardware in hand. Intel has an event planned for the end of October called the Intel InnovatiON event (part of the ON series), which would be the right time to introduce Alder Lake as a product to the world. Exactly when it comes to retail will be a different question, but as long as Intel executes this year on the technology, it should make for an interesting competition with the rest of the market.

223 Comments

View All Comments

Unashamed_unoriginal_username_x86 - Thursday, August 19, 2021 - link

When you say "similar in magnitude to what skylake did" on the Golden Cove page, are you sure you don't mean something like Sandy Bridge? I vaguely remember Skylake being a pretty nominal improvement on the order of 10-15%mode_13h - Thursday, August 19, 2021 - link

> I vaguely remember Skylake being a pretty nominal improvement on the order of 10-15%That would NOT be a nominal improvement! Fortunately, the real number isn't hard to find:

https://www.anandtech.com/show/9483/intel-skylake-...

"In our IPC testing, ... we saw a 5.7% increase in performance over Haswell. That value masks the fact that between Haswell and Skylake, we have Broadwell, marking a 5.7% increase for a two generation gap."

"In our discrete gaming benchmarks, at 3GHz Skylake actually performs worse than Haswell at an equivalent clockspeed, giving up an average of 1.3% performance."

Wereweeb - Thursday, August 19, 2021 - link

Funny how Ryzen made people used to thinking in terms of generational improvements as "10-15%" again. Thankfully, EUV and GAAFETs will make sure the next few generations keep advancing at that pace.mode_13h - Thursday, August 19, 2021 - link

> are you sure you don't mean something like Sandy Bridge?Exactly. The timeframe of "a decade" and the magnitude of the changes they're describing lines up with Sandybridge.

Spunjji - Monday, August 23, 2021 - link

Definitely referring to Sandy Bridge, as that was a 2011 architecture.zzzxtreme - Thursday, August 19, 2021 - link

been waiting 10 years for this, assuming this is a breakthrough x86 cpucheshirster - Thursday, August 19, 2021 - link

Not this time.shabby - Thursday, August 19, 2021 - link

Finally we'll see how good intels 10nm is...AdrianBc - Thursday, August 19, 2021 - link

"E-core will be at ‘Haswell-level’ AVX2 support" seems to be contradicted by the slides from the Intel presentation, which imply that Gracemont does not have FMA, but only separate FADD and FMUL.If the Intel slides are correct Gracemont cannot support the complete Haswell instruction set.

Maybe Gracemont supports only the 256-bit integer instructions added by Haswell over Sandy Bridge and it might also not support the BMI Haswell instructions.

Also weird is that the original Intel presentation does not contain the terms AVX or AVX2, but only some vague "support for Advanced Vector Instructions".

So, unless Intel has purposedly confused the presentations for now, it looks like the Gracemont and Golden Cove do not have compatible instructions sets, even with AVX-512 disabled.

If that is true, then disabling AVX-512 must have only one reason, decreasing the manufacturing cost for Alder Lake, by using all the defect chips and reserving the good ones for Sapphire Rapids.

AdrianBc - Thursday, August 19, 2021 - link

After writing the comment above, I have looked again at the Gracemont presentation and only now I have noticed that in the same slide that does not show any FMA unit it is written that it indeed supports the FMA instructions.I do not know why 2 FADD + 2 FMUL are shown instead of 2 FMA, like in the slide for Golden Cove.

Because each FADD is on the same port with an FMUL, this means that Gracemont cannot function like AMD Zen, which can do an extra separate FADD besides an FMUL, when the full FMA is not needed. If the FMA and the FMUL cannot be executed simultaneously, then they should have drawn it as just an FMA unit, like in the Golden Cove slide.

In any case even if Gracemont would be compatible with Haswell + the SHA extension, that still cannot make it instruction compatible with Golden Cove, because there are important additional instructions introduced in Broadwell, Ice Lake and Tiger Lake.