Intel Launches Coffee Lake Xeon E (Entry): The Next-Gen E3-1200

by Ian Cutress on July 12, 2018 12:00 PM EST- Posted in

- CPUs

- Intel

- Xeon

- E3-1200

- Coffee Lake

- Xeon E

- Xeon-E

- E3-1200 v7

Today Intel is announcing the Xeon E family of processors. The Xeon E-2100 stack of CPUs will replace the previous generation E3 v6 processors, following Intel's renaming of their whole Xeon stack, and in line with the workstation-focused Xeon W-2100 family, and the Xeon D-2100 family. The new processors mirror the current Coffee Lake Core processors on the market and will support up to 64GB of ECC memory, but require motherboards with a specalized workstation C246 chipset. The E in this case stands for 'Entry', and these processors aim to be the cornerstone of Intel's portfolio of entry-level workstation parts.

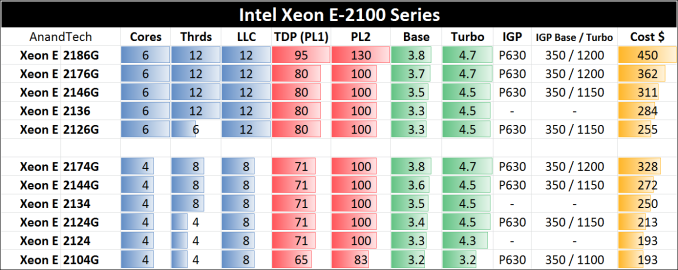

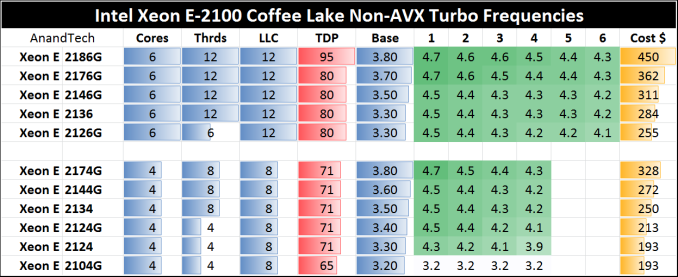

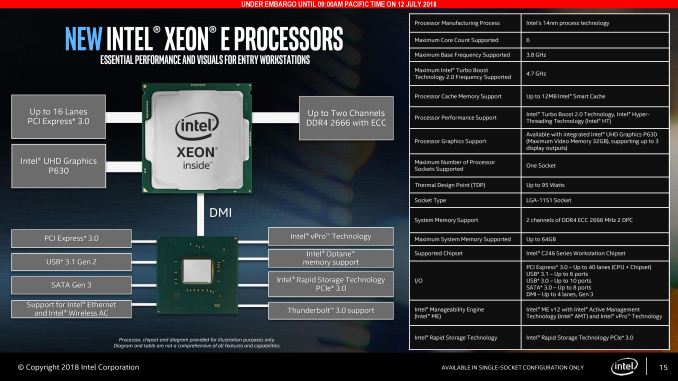

The new family of processors will have four core and six core parts, mostly with hyperthreading, and mostly with integrated graphics, much like the Coffee Lake Core 8000-series CPUs. In order to differentiate the models with integrated graphics, these parts will have a 'G' after the name. All the processors are built on Intel's 14++ process technology, offering base clocks up to 3.8 GHz and single core turbo up to 4.7 GHz. At this time Intel is not disclosing all-core turbo frequencies or AVX2 frequencies. TDP will mostly be 71-80W, except for the high-end six-core processor which will be at 95W. All processors will support up to dual channel DDR4-2666 Non-ECC and ECC UDIMM modules. Intel also confirmed that the interface between the CPU and heatspreader is a polymer-based thermal interface material (TIM), not soldered.

Despite the same pin configuration as the consumer parts (LGA1151), they will require Xeon E-enabled motherboards with the C246 chipset, and will not work in 300-series motherboards. They will also not work in C236-based motherboards, even though they have the same socket, due to Intel's product segmentation policies. Intel confirmed that the new C246 chipset will have an integrated wireless controller inside, and will require a CRF module on board in order to enable it (much like the second generation of 300-series chipsets). The C246 motherboards are set to support Xeon E, Pentium, Celeron, and Core i3 processors only, and not Core i5/i7. At the present time, Intel did not comment on any future parts that may or may not have 8 cores.

Out of the processors that are in the stack, three are without hyperthreading and three are without integrated graphics. Intel did disclose the per-core turbos for each processor after the launch, showing that most of the processors will be 4.1-4.3 GHz at all core turbo, meaning that the load power values will be pushing well into their PL2 numbers. Intel stated that for all the parts with integrated graphics, the base frequencies were 350 MHz, however the turbo peak frequencies were 1200 MHz for the 218x and 217x models, 1150 MHz for the 212x to 216x models, and 1100 MHz for the E-2104G. The E-2104G is what is known as an off-roadmap model, built only for specific customers, and in our briefing Intel iterated its desire to only speak about the ten 'on-roadmap' models as part of this release. However other companies have noted that this part exists.

All the processors have 16 PCIe lanes from the CPU, and 24 lanes from the chipset (which has an upstream limit of four lanes), and much to our chagrin and to obfuscate the issue, Intel will advertise these processors as having '40' PCIe lanes. We do not see the reason why Intel needs to obfuscate this, as they have never needed to in previous generations, and it makes zero sense unless all the PCIe lanes were equal. We have beat on this door several times previously with Intel, but we never seem to discuss it with (or influence) the person who actually makes that decision.

The top end part, the Xeon E-2186G, will peak at a 3.8 GHz base frequency, and have a single core turbo of 4.7 GHz. Comparing to the consumer line, this is +100 MHz on the base frequency over the Core i7-8700K, although the Xeon has ECC, is not overclockable, and will have a tray price of $450. It is worth noting that in previous generations Intel's top end Xeon E3-1200 chip was often around $650, and more than $200+ the second best processor, and that isn't happening here. This seemed very 'un-Intel' when we saw it for the first time. Intel's official response was that they offer 'price points that will be compelling to OEMs and we expect more opportunities from a solutions perspective''. This response doesn't really address the issue of why there isn't a top $600+ SKU anymore, leaving a card on the table which states that we should probably expect higher-end models to come out at a later date. Roadmaps have already leaked that Intel is preparing an 8-core consumer product later this year, so I can imagine that an equivalent Xeon E processor will also be made available.

| Intel Xeon Naming Strategy | ||||||||

| SNB | IVB | HSW | BDW | SKL-SP | Future | |||

| Servers | E7-8000 | 'v1' | v2 | v3 | v4 | Xeon SP Platinum Xeon SP Gold Xeon SP Silver Xeon SP Bronze |

||

| E7-4000 | 'v1' | v2 | v3 | v4 | ||||

| E7-2800 | 'v1' | v2 | - | - | ||||

| E5-4600 | 'v1' | v2 | v3 | v4 | ||||

| E5-2600 | 'v1' | v2 | v3 | v4 | ||||

| E5-2400 | 'v1' | v2 | v3 | - | ||||

| Workstations | E5-1600 | 'v1' | v2 | v3 | v4 | Xeon W | ||

| E5-1400 | 'v1' | v2 | v3 | - | - | - | - | |

| SNB | IVB | HSW | BDW | SKL | KBL | CFL | ||

| Mobile | E3-1500M | - | - | - | - | v5 | v6 | Xeon E |

| Consumer | E3-1200 | 'v1' | v2 | v3 | v4 | v5 | v6 | Xeon E |

| Comms | E3-1100 | 'v1' | v2 | - | - | - | - | - |

| Network | Xeon-D | - | - | - | D-1500 | D-2100 | ||

As we've mentioned before, Intel's new naming scheme for the Xeon platforms has been a relatively haphazard transition, with the description of the direct translation of how parts compare to the previous generation being minimal at best. Xeon E is arguably the easiest transition to make: what used to be the E3-1275 v6 in the stack is now the Xeon E-2176G, with the 6 representing the number of cores. Intel now also has three '2100' lines of processors: Xeon D-2100, Xeon W-2100, and Xeon E-2100. They're all aimed at different markets, and the numbering of each model has no correlation to the same number in a different segment. So your guess as to why this matters is as good as ours.

One interesting thing came to the forefront of our pre-briefing however. In our slide deck, when discussing which 14nm process was being used, both 14++ and 14+++ were mentioned. If you like more 14-plus variants, Intel does too. I'm sure that this was an error on the part of the speaker, as we know that Coffee Lake is 14++.

We've been discussing on and off with Intel about sampling the Xeon E-series processors for review for over six months, when the first leaks started to come out. We were told yesterday, finally, that the business unit is not planning to seed the press review units. A similar situation happened with the E3-1200 v6 processors. So immediate press reviews will not be forthcoming.

Finally, systems with Xeon E will be being announced from today from the major OEMs.

40 Comments

View All Comments

Reflex - Friday, July 13, 2018 - link

This here is a point I've tried to make. Hardware fixes for Meltdown and Spectre, by design, will reduce performance. It's unlikely to be significantly different than the current methods of avoiding the problems. There is no reason to wait for hardware that has a fix, it may perform better but it'll be almost entirely due to it simply being a new generation of chips, not due to the fixes being in hardware.GreenReaper - Friday, July 13, 2018 - link

Meltdown requires a security check during L1 address translation, while the branch misprediction form of Spectre can be addressed by storing more information about the caller it's for (potentially multiplying cache entries):https://news.ycombinator.com/item?id=16593061

Both of these will require extra transistors, and maybe extra time, but it seems unlikely to be as much time as the software workarounds.

Indeed, it's another form of specialized hardware for particular tasks; like AES-NI, which can easily be ten times faster than doing the same thing in software.

Reflex - Friday, July 13, 2018 - link

I can't agree with that assessment, you are comparing adding more conditions to an operation (which reduces performance) with adding a specialized component that does just one thing well. Branch prediction is used virtually all the time, it does not get 'faster' by adding more requirements, in fact it gets slower. Additional transisters dedicated to the task will not be used only in specific scenarios, because again branch prediction is used virtually all the time. Instead they will add more heat, more latency and more power consumption.I don't see doing it 'in hardware' as a way to gain performance out of this.

GreenReaper - Saturday, July 14, 2018 - link

That doesn't make sense. We have to effectively add those conditions (or elide the benefits of the cache) now *anyway* to ensure security - which imposes a performance penalty. That's the deficit we're trying to avoid. I wouldn't be surprised if such checks could be done in parallel to the hardware access, so it returns an error in the same time that it would have returned a value.Reflex - Saturday, July 14, 2018 - link

No, the current approach was to disable the functionality, which certainly does cost performance. To do it securely will be more latent than the previous implementation, so while you will get some perf back due to the feature being usable again, it won't be like before. It's not going to be some huge gain.And no, you can't do it in parallel or you open yourself up to another side channel attack. Parallel operations like this are a big part of the problem in the first place.

iwod - Thursday, July 12, 2018 - link

The DMI limits are getting silly. 4x PCI-E bandwidth for everything from Thunderbolt 3.0, possibly 10G Ethernet, USB 3.1 Gen 2,shabby - Thursday, July 12, 2018 - link

Ya i'm surprised the infographic didn't mention UP TO 16 PCIE LANES FOR ESSENTIAL PERFORMANCE AND VISUALS!!!edzieba - Friday, July 13, 2018 - link

Whether DMI is a limit depends on how much of the data shunted around the PCIe buses actually needs to hop over it to go via the CPU & main memory. With DMI you can go from storage to/from network (or storage to GPU, etc) just via the PCH without bottlenecking.TrevorH - Thursday, July 12, 2018 - link

> Intel's new naming scheme for the Xeon platforms has been a relatively haphazard transitionIs that a polite way of saying "makes no sense at all"?

bolkhov - Thursday, July 12, 2018 - link

Previous E3/E5/E7 naming was familiar, but current scheme is more meaningful.At least Xeon E: it encodes generation (2nd digit - now "1") and number of cores (last digit).

3rd digit isn't obvious: it encodes the "level"/"coolness" somehow.

BTW, Xeon-SP naming is also more meaningful than E5/E7 SKU numbering.