Sizing Up Servers: Intel's Skylake-SP Xeon versus AMD's EPYC 7000 - The Server CPU Battle of the Decade?

by Johan De Gelas & Ian Cutress on July 11, 2017 12:15 PM EST- Posted in

- CPUs

- AMD

- Intel

- Xeon

- Enterprise

- Skylake

- Zen

- Naples

- Skylake-SP

- EPYC

Memory Subsystem: Bandwidth

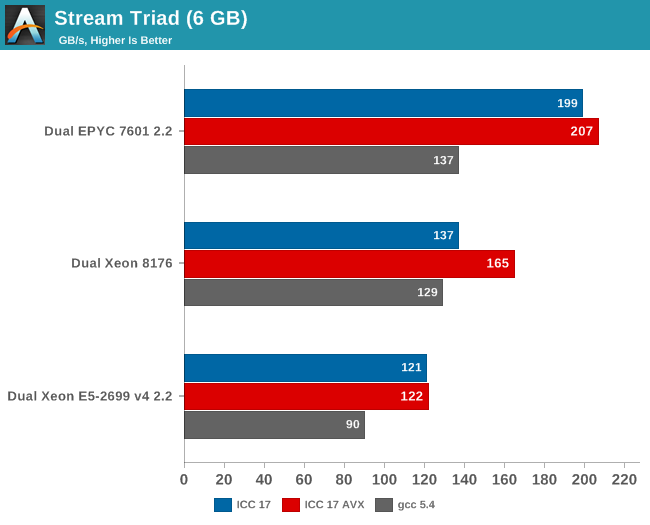

Measuring the full bandwidth potential with John McCalpin's Stream bandwidth benchmark is getting increasingly difficult on the latest CPUs, as core and memory channel counts have continued to grow. We compiled the stream 5.10 source code with the Intel compiler (icc) for linux version 17, or GCC 5.4, both 64-bit. The following compiler switches were used on icc:

icc -fast -qopenmp -parallel (-AVX) -DSTREAM_ARRAY_SIZE=800000000

Notice that we had to increase the array significantly, to a data size of around 6 GB. We compiled one version with AVX and one without.

The results are expressed in gigabytes per second.

Meanwhile the following compiler switches were used on gcc:

-Ofast -fopenmp -static -DSTREAM_ARRAY_SIZE=800000000

Notice that the DDR4 DRAM in the EPYC system ran at 2400 GT/s (8 channels), while the Intel system ran its DRAM at 2666 GT/s (6 channels). So the dual socket AMD system should theoretically get 307 GB per second (2.4 GT/s* 8 bytes per channel x 8 channels x 2 sockets). The Intel system has access to 256 GB per second (2.66 GT/s* 8 bytes per channel x 6 channels x 2 sockets).

AMD told me they do not fully trust the results from the binaries compiled with ICC (and who can blame them?). Their own fully customized stream binary achieved 250 GB/s. Intel claims 199 GB/s for an AVX-512 optimized binary (Xeon E5-2699 v4: 128 GB/s with DDR-2400). Those kind of bandwidth numbers are only available to specially tuned AVX HPC binaries.

Our numbers are much more realistic, and show that given enough threads, the 8 channels of DDR4 give the AMD EPYC server a 25% to 45% bandwidth advantage. This is less relevant in most server applications, but a nice bonus in many sparse matrix HPC applications.

Maximum bandwidth is one thing, but that bandwidth must be available as soon as possible. To better understand the memory subsystem, we pinned the stream threads to different cores with numactl.

| Pinned Memory Bandwidth (in MB/sec) | |||

| Mem Hierarchy |

AMD "Naples" EPYC 7601 DDR4-2400 |

Intel "Skylake-SP" Xeon 8176 DDR4-2666 |

Intel "Broadwell-EP" Xeon E5-2699v4 DDR4-2400 |

| 1 Thread | 27490 | 12224 | 18555 |

| 2 Threads, same core same socket |

27663 | 14313 | 19043 |

| 2 Threads, different cores same socket |

29836 | 24462 | 37279 |

| 2 Threads, different socket | 54997 | 24387 | 37333 |

| 4 threads on the first 4 cores same socket |

29201 | 47986 | 53983 |

| 8 threads on the first 8 cores same socket |

32703 | 77884 | 61450 |

| 8 threads on different dies (core 0,4,8,12...) same socket |

98747 | 77880 | 61504 |

The new Skylake-SP offers mediocre bandwidth to a single thread: only 12 GB/s is available despite the use of fast DDR-4 2666. The Broadwell-EP delivers 50% more bandwidth with slower DDR4-2400. It is clear that Skylake-SP needs more threads to get the most of its available memory bandwidth.

Meanwhile a single thread on a Naples core can get 27,5 GB/s if necessary. This is very promissing, as this means that a single-threaded phase in an HPC application will get abundant bandwidth and run as fast as possible. But the total bandwidth that one whole quad core CCX can command is only 30 GB/s.

Overall, memory bandwidth on Intel's Skylake-SP Xeon behaves more linearly than on AMD's EPYC. All off the Xeon's cores have access to all the memory channels, so bandwidth more directly increases with the number of threads.

219 Comments

View All Comments

StargateSg7 - Sunday, August 6, 2017 - link

Maybe I'm spoiled, but to me a BIG database is something I usually deal with on a daily basissuch as 500,000 large and small video files ranging from two megabytes to over a PETABYTE

(1000 Terabytes) per file running on a Windows and Linux network.

What sort of read and write speeds do we get between disk, main memory and CPU

and when doing special FX LIVE on such files which can be 960 x 540 pixel youtube-style

videos up to full blown 120 fps 8192 x 4320 pixel RAW 64 bits per pixel colour RGBA files

used for editing and video post-production.

AND I need for the smaller files, total I/O-transaction rates at around

OVER 500,000 STREAMS of 1-to-1000 64 kilobyte unique packets

read and written PER SECOND. Basically 500,000 different users

simultaneously need up to one thousand 64 kilobyte packets per

second EACH sent to and read from their devices.

Obviously Disk speed and network comm speed is an issue here, but on

a low-level hardware basis, how much can these new Intel and AMD chips

handle INTERNALLY on such massive data requirements?

I need EXABYTE-level storage management on a chip! Can EITHER

Xeon or EPyC do this well? Which One is the winner? ... Based upon

this report it seems multiple 4-way EPyC processors on waterblocked

blades could be racked on a 100 gigabit (or faster) fibre backbone

to do 500,000 simultaneous users at a level MUCH CHEAPER than

me having to goto IBM or HP for a 30+ million dollar HPC solution!

PixyMisa - Tuesday, July 11, 2017 - link

It seems like a well-balanced article to me. Sure the DB performance issue is a corner case, but from a technical point of view its worth knowing.I'd love to see a test on a larger database (tens of GB) though.

philehidiot - Wednesday, July 12, 2017 - link

It seems to me that some people should set up their own server review websites in order that they might find the unbiased balance that they so crave. They might also find a time dilation device that will allow them to perform the multitude of different workload tests they so desire. I believe this article stated quite clearly the time constraints and the limitations imposed by such constraints. This means that the benchmarks were scheduled down to the minute to get as many in as possible and therefore performing different tests based on the results of the previous benchmarks would have put the entire review dataset in jeopardy.It might be nice to consider just how much data has been acquired here, how it might have been done and the degree of interpretation. It might also be worth considering, if you can do a better job, setting up shop on your own and competing as obviously the standard would be so much higher.

Sigh.

JohanAnandtech - Thursday, July 13, 2017 - link

Thank you for being reasonable. :-) Many of the benchmarks (Tinymembench, Stream, SPEC) etc. can be repeated, so people can actually check that we are unbiased.Shankar1962 - Monday, July 17, 2017 - link

Don't go by the labs idiotUnderstand what real world workloads are.....understand what owning an entire rack means ......you started foul language so you deserve the same respect from me......

roybotnik - Wednesday, July 12, 2017 - link

EPYC looks extremely good here aside from the database benchmark, which isn't a useful benchmark anyways. Need to see the DB performance with 100GB+ of memory in use.CarlosYus - Friday, July 14, 2017 - link

A detailed and unbiased article. I'm awaiting for more tests as testing time passes.3.2 Ghz is a moderate Turbo for AMD EPYC, I think AMD could push it further with a higher thermal envelope i/o 14 nm process improvement in the coming months.

mdw9604 - Tuesday, July 11, 2017 - link

Nice, comprehensive article. Glad to see AMD is competitive once again in the server CPU space.nathanddrews - Tuesday, July 11, 2017 - link

"Competitive" seems like an understatement, but yes, AMD is certainly bringing it!ddriver - Tuesday, July 11, 2017 - link

Yeah, offering pretty much double the value is so barely competitive LOL.