Sizing Up Servers: Intel's Skylake-SP Xeon versus AMD's EPYC 7000 - The Server CPU Battle of the Decade?

by Johan De Gelas & Ian Cutress on July 11, 2017 12:15 PM EST- Posted in

- CPUs

- AMD

- Intel

- Xeon

- Enterprise

- Skylake

- Zen

- Naples

- Skylake-SP

- EPYC

Multi-core SPEC CPU2006

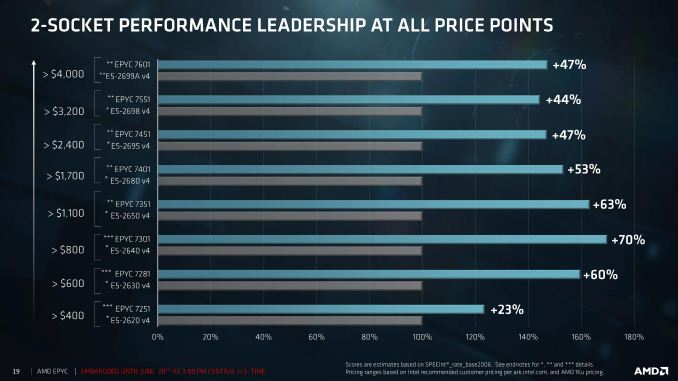

For the record, we do not believe that the SPEC CPU "Rate" metric has much value for estimating server CPU performance. Most applications do not run lots of completely separate processes in parallel; there is at least some interaction between the threads. But since the benchmark below caused so much discussion, we wanted to satisfy the curiosity of our readers.

Does the EPYC7601 really have 47% more raw integer power? Let us find out. Though please note that you are looking at officially invalid base SPEC rate runs, as we still have to figure out how to tell the SPEC software that our "invalid" flag "-Ofast" is not invalid at all. We did the required 3 iterations though.

| Subtest | Application type | Xeon E5-2699 v4 @ 2.8 |

Xeon 8176 @ 2.8 |

EPYC 7601 @2.7 |

EPYC Vs Broadwell EP |

EPYC vs Skylake SP |

| 400.perlbench | Spam filter | 1470 | 1980 | 2020 | +37% | +2% |

| 401.bzip2 | Compression | 860 | 1120 | 1280 | +49% | +14% |

| 403.gcc | Compiling | 960 | 1300 | 1400 | +46% | +8% |

| 429.mcf | Vehicle scheduling | 752 | 927 | 837 | +11% | -10% |

| 445.gobmk | Game AI | 1220 | 1500 | 1780 | +46% | +19% |

| 456.hmmer | Protein seq. analyses | 1220 | 1580 | 1700 | +39% | +8% |

| 458.sjeng | Chess | 1290 | 1570 | 1820 | +41% | +16% |

| 462.libquantum | Quantum sim | 545 | 870 | 1060 | +94% | +22% |

| 464.h264ref | Video encoding | 1790 | 2670 | 2680 | +50% | -0% |

| 471.omnetpp | Network sim | 625 | 756 | 705 (*) | +13% | -7% |

| 473.astar | Pathfinding | 749 | 976 | 1080 | +44% | +11% |

| 483.xalancbmk | XML processing | 1120 | 1310 | 1240 | +11% | -5% |

(*) We had to run 471.omnetpp with 64 threads on EPYC: when running at 128 threads, it gave errors. Once solved, we expect performance to be 10-20% higher.

Ok, first a disclaimer. The SPECint rate test is likely unrealistic. If you start up 88 to 128 instances, you create a massive bandwidth bottleneck and a consistent CPU load of 100%, neither of which are very realistic in most integer applications. You have no synchronization going on, so this is really the ideal case for a processor such as the AMD EPYC 7601. The rate test estimates more or less the peak integer crunching power available, ignoring many subtle scaling problems that most integer applications have.

Nevertheless, AMD's claim was not farfetched. On average, and using a "neutral" compiler with reasonable compiler settings, the AMD 7601 has about 40% (42% if you take into account that our Omnetpp score will be higher once we fixed the 128 instances issue) more "raw" integer processing power than the Xeon E5-2699 v4, and is even about 6% faster than the Xeon 8176. Don't expect those numbers to be reached in most real integer applications though. But it shows how much progress AMD has made nevertheless...

219 Comments

View All Comments

PixyMisa - Tuesday, July 11, 2017 - link

No, the pricing is correct. The 1P CPUs really are half the price of a single 2P CPU.msroadkill612 - Wednesday, July 12, 2017 - link

Seems to me, the simplest explanation of something complex, is to list what it will not do, which they will not do :(.Can i run a 1p Epyc in a 2p mobo e.g., please?

PixyMisa - Thursday, July 13, 2017 - link

Short answer is no. It might boot, but only half the slots, memory, SATA and so on will be available. Two 1P CPUs won't talk to each other.A 2P Epyc will work in a 1P board though.

cekim - Tuesday, July 11, 2017 - link

One glaring bug/feature of AMD's segmentation relative to Intel's is the utter and obvious crippling of clock speeds for all but the absolute top SKUs. Fewer cores should be able to make use of higher clocks within the same TDP envelope. As a result Intel is objectively offering more and better fits up and down the sweep of cores vs clocks vs price spectrum.So, the bottom line is AMD is saying that you will have to buy the top-end, 4S SKU to get the top GHz for those applications in your mix that won't benefit from 16,18,32,128 cores.

I say all of this as someone who desperately wants EPYC to shake things up and force Intel to remove the sand-bags. I know I'm in a small, but non-zero market of users who can make use of dozens of cores, but still need 8 or fewer cores to perform on par with desktop parts for that purpose.

KAlmquist - Wednesday, July 12, 2017 - link

One possibility is that they have only a small percentage of the chips currently being produced bin well enough to be used in the highest clocking SKU's, so they are saving those chips for the most expensive offerings. Admittedly, that depends on what they are seeing coming off the production line. If they have a fair number of chips where with two very good cores, and two not so good, then it would make sense to offer a high clocking 16 core EPYC using chips with two cores disabled. But if clock speed on most chips is limited due to minor registration errors (which would affect the entire chip), then a chip with only two really good cores would require two localized defects in two separate cores, in addition to very good registration to get the two good cores. The combination might be too rare to justify a separate SKU.I would expect Global Foundries to continue to tweak its process to get better yields. In that case, more processors would end up in the highest bin, and AMD might decide to launch a higher clock speed 16 and 8 core EPYC processors, mostly using chips which bin well enough that they could have been used for the 32 core EPYC 7601.

alpha754293 - Tuesday, July 11, 2017 - link

Why does the Intel Xeon 6142 cost LESS than the 6142M? (e.g. per the table above, 6142 is shown with a price of $5946 while the 6142M costs $2949)ca197 - Tuesday, July 11, 2017 - link

I assume that is the wrong way round on the list. I have seen it reported the other way round on other sites.Ian Cutress - Tuesday, July 11, 2017 - link

You're correct. I've updated the piece, was a misread error from Intel's tables.coder543 - Tuesday, July 11, 2017 - link

On page 6, it says that Epyc only has 64 PCIe lanes (available), but that's not correct. There are 128 PCIe lanes per chip. In a 1P configuration, that's 128 PCIe lanes available. On a 2P configuration, 64 PCIe lanes from each chip are used to connect to the other chip, leaving 64 + 64 = 128 PCIe lanes still available.This is a significant advantage.

Ian Cutress - Tuesday, July 11, 2017 - link

You misread that table. It's quoting per-CPU when in a 2P configuration.