Sizing Up Servers: Intel's Skylake-SP Xeon versus AMD's EPYC 7000 - The Server CPU Battle of the Decade?

by Johan De Gelas & Ian Cutress on July 11, 2017 12:15 PM EST- Posted in

- CPUs

- AMD

- Intel

- Xeon

- Enterprise

- Skylake

- Zen

- Naples

- Skylake-SP

- EPYC

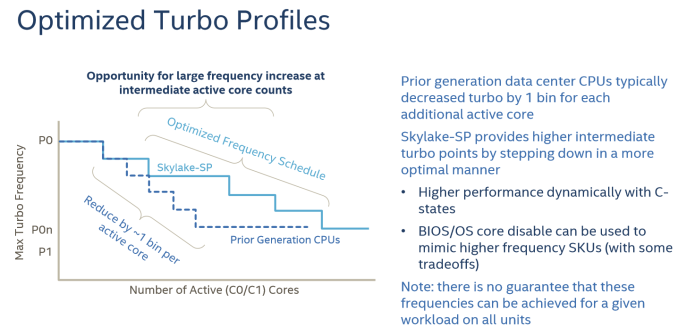

Intel's Optimized Turbo Profiles

Also new to Skylake-SP, Intel has also further enhanced turbo boosting.

There are also some security and virtualization enhancements (MBE, PPK, MPX) , but these are beyond the scope this article as we don't test them.

Summing It All Up: How Skylake-SP and Zen Compare

The table below shows you the differences in a nutshell.

| AMD EPYC 7000 |

Intel Skylake-SP | Intel Broadwell-EP |

|

| Package & Dies | Four dies in one MCM | Monolithic | Monolithic |

| Die size | 4x 195 mm² | 677 mm² | 456 mm² |

| On-Chip Topology | Infinity Fabric (1-Hop Max) |

Mesh | Dual Ring |

| Socket configuration | 1-2S | 1-8S ("Platinum") | 1-2S |

| Interconnect (Max.) Bandwidth (*)(Max.) |

4x16 (64) PCIe lanes 4x 37.9 GB/s |

3x UPI 20 lanes 3x 41.6 GB/s |

2x QPI 20 lanes 2x 38.4 GB/s |

| TDP | 120-180W | 70-205W | 55-145W |

| 8-32 | 4-28 | 4-22 | |

| LLC (max.) | 64MB (8x8 MB) | 38.5 MB | 55 MB |

| Max. Memory | 2 TB | 1.5 TB | 1.5 TB |

| Memory subsystem Fastest sup. DRAM |

8 channels DDR4-2666 |

6 channels DDR4-2666 |

4 channels DDR4-2400 |

| PCIe Per CPU in a 2P |

64 PCIe (available) | 48 PCIe 3.0 | 40 PCIe 3.0 |

(*) total bandwidth (bidirectional)

At a high level, I would argue that Intel has the most advanced multi-core topology, as they're capable of integrating up to 28 cores in a mesh. The mesh topology will allow Intel to add more cores in future generations while scaling consistently in most applications. The last level cache has a decent latency and can accommodate applications with a massive memory footprint. The latency difference between accessing a local L3-cache chunk and one further away is negligible on average, allowing the L3-cache to be a central storage for fast data synchronization between the L2-caches. However, the highest performing Xeons are huge, and thus expensive to manufacture.

AMD's MCM approach is much cheaper to manufacture. Peak memory bandwidth and capacity is quite a bit higher with 4 dies and 2 memory channels per die. However, there is no central last level cache that can perform low latency data coordination between the L2-caches of the different cores (except inside one CCX). The eight 8 MB L3-caches acts like - relatively low latency - spill over caches for the 32 L2-caches on one chip.

219 Comments

View All Comments

extide - Tuesday, July 11, 2017 - link

PCPer made this same mistake -- Nehalem/Westmere used a crossbar memory bus -- not a ringbus. Only Nehalem/Westmere EX used the ringbus (the 6500/7500 series) The i7 and Xeon 5500 and 5600 series used the crossbar.extide - Tuesday, July 11, 2017 - link

Sandy Bridge brought the ringbus down to Xeon EP and client chips.Yorgos - Tuesday, July 11, 2017 - link

"With the complexity of both server hardware and especially server software, that is very little time. There is still a lot to test and tune, but the general picture is clear."No wonder why we see ubuntu and ancient versions of gcc and the rest of the s/w stack.

Imagine if you tried to use debian or rhel, it would take you decades to get the review.

eligrey - Tuesday, July 11, 2017 - link

Why did you omit the Turbo frequencies for the Xeon Gold 6146 and 6144?Intel ARK says that the 6146's turbo frequency is 4.2GHz and the 6144's is 4.5GHz.

eligrey - Tuesday, July 11, 2017 - link

Oops, I mean 4.2GHz for both.boozed - Tuesday, July 11, 2017 - link

Need more Skylake-SP SKUsrHardware - Tuesday, July 11, 2017 - link

For the purley system, It's listed that you used Chipset Intel Wellsburg B0This information cannot be correct. Lewisburg Chipset is the name of the purley chipset. Also, B0 stepping lewisburg also wouldn't boot with the stepping of CPU you have.

rHardware - Tuesday, July 11, 2017 - link

That 0200011 microcode is also very old.Rickyxds - Tuesday, July 11, 2017 - link

I'am a brazilian processors enthusiast and I'am very critic about intel and AMD processors, between 2012 and Q1 2017 AMD just doesn't existed, who bought AMD on that years, bougth just for love AMD and just it, doesn't for the price, doesn't for the high core count, doesn't for AMD is red, AMD was the worst performance processors. The A9 Apple dual core performance is better than FX 8150.But now I am very surprise with the aggressive AMD prices. No one here Imagined get the Ryzen 7 performance for less than $500. And I don't know if this scenario brings profit to AMD, but for the image against the intel it's wonderful.

On the next years we will see.

krumme - Tuesday, July 11, 2017 - link

Thank you for quality stuff article especially given the short time. So thank you for booting up Johan !Interesting and surpricing results.