PCIe 5.0

SK hynix early in Friday announced that the company has finished the development of it's PCB01 PCIe Gen5 SSD, the company's forthcoming high-end SSD for OEMs. Based on the company's new Alistar platform, the PCB01 is designed to deliver chart-topping performance for client machines. And, as a sign of the times, SK hynix is positioning the PCB01 for AI PCs, looking to synergize with the overall industry interest in anything and everything AI. The bare, OEM-focused drives have previously been shown off by SK hynix, and make no attempt to hide what's under the hood. The PCB01 relies on SK hynix's Alistar controller, which features a PCIe Gen5 x4 host interface on the front end and eight NAND channels on the back end, placing it...

AMD Unveils Ryzen 9000 CPUs For Desktop, Zen 5 Takes Center Stage at Computex 2024

During AMD's Computex 2024 kick-off keynote, AMD's CEO, Dr. Lisa Su, officially unveiled and announced the company's next generation of Ryzen processors. Today marks the first unveiling of AMD's...

62 by Gavin Bonshor on 6/2/2024PCI-SIG Completes CopprLink Cabling Standard: PCIe 5.0 & 6.0 Get Wired

The PCI-SIG sends word over this morning that the special interest group has completed their development efforts on the group’s new PCI-Express cabling standard, CopprLink. Designed to go hand-in-hand...

8 by Ryan Smith on 5/1/2024SK hynix Platinum P51 Gen5 SSD with 238L NAND Spotted at GTC

SK hynix is set to unveil their first Gen5 consumer NVMe SSD lineup shortly, based on the products at display in their GTC 2024 booth. The Platinum P51 M.2...

8 by Ganesh T S on 3/19/2024Sabrent's Rocket 5 SSD Rockets to 14,169 MB/s, Available Soon

Sabrent on Friday announced the latest addition to its Rocket family of high-performance SSDs, the Rocket 5. Rated for sequential read speeds of over 14,000 MB/s and up to...

8 by Anton Shilov on 1/8/2024HP Z6 G5 A Workstation Review: 96-Core AMD Ryzen Threadripper Pro 7995WX Impresses

With AMD's recent launch of their Zen 4 architecture-based Threadripper 7000 series CPUs, the company and its OEM partners have unleashed a new wave of high-end PCs and workstations...

23 by Gavin Bonshor on 12/13/2023Silicon Motion Readies PCIe Gen5 SSD Platform with 3.5W Power Consumption [UPDATED]

UPDATE 8/24: As it turns out, the 3.5W figure referes to power consumption of the controller alone, not the whole SSD. The story has been updated accordingly. We also...

19 by Anton Shilov on 8/9/2023Seagate Announces FireCuda 540 PCIe Gen5 SSD

Flash-based computer storage has been improving in speed and capacity at breakneck pace over the last decade. M.2 NVMe SSDs have almost completely replaced SATA drives for primary storage...

3 by Ganesh T S on 6/27/2023Corsair Introduces MP700 PCIe 5.0 SSDs: 1 TB Starting At $169.99

After a few teasers and months of waiting, Corsair has finally launched the MP700, the company's first PCIe 5.0 SSD. The MP700 aims to win enthusiasts over with its...

18 by Zhiye Liu on 5/4/2023Crucial Preps T700 PCIe 5.0 SSD With Write Speeds Up To 12.4 GB/s

Crucial has started to tease the T700, the company's first mainstream PCIe 5.0 SSD. Not to be confused with the Terminator T-700, the T700's product page has already gone...

28 by Zhiye Liu on 3/23/2023First PCIe Gen5 SSDs Finally Hit Shelves - But The Best Is Yet To Come

This week, consumer-grade PCIe 5.0 M.2 drives have finally hit the U.S. market, well over a year since the first client PC platforms supporting PCIe Gen5 became available. The...

29 by Anton Shilov on 3/3/2023Intel Launches Xeon W-3400 and W-2400 Processors For Workstations: Up to 56 Cores and 112 PCIe 5.0 Lanes

For all of the singular focus that Intel has placed on its consumer Core desktop CPU parts in the last few years, you could be forgiven for thinking that...

62 by Gavin Bonshor on 2/15/2023The MSI MEG Ai1300P PCIE5 1300W PSU Review: The ATX 3.0 Era Has Begun

Just under a year since the specification was first announced, the ATX 3.0 era for power supplies is now underway. The updated version of the Intel-maintained specification introduced several...

67 by E. Fylladitakis on 12/8/2022NZXT Unveils N7 Z790 Motherboard for Intel 13th Gen Core Series

With a lot of news and info dropping on Intel's latest Z790 chipset using the LGA1700 socket, NZXT has pulled the trigger and announced its N7 Z790 motherboard. Available...

17 by Gavin Bonshor on 9/27/2022MSI Unveils X670 Pricing Ahead of AMD Ryzen 7000 Launch, Starting at $290

Ahead of the launch of AMD's latest Ryzen 7000 processors, which will hit retail shelves on September 27th, MSI unveiled pricing on four of its X670/X670E motherboards. Given the...

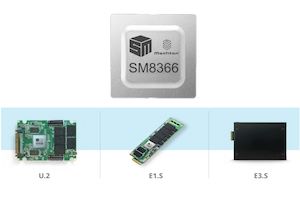

29 by Gavin Bonshor on 9/8/2022Silicon Motion Announces SM8366 PCIe 5.0 x4 NVMe Controller and MonTitan SSD Solutions Platform for Enterprise Storage

In the lead up to the Flash Memory Summit next week, many vendors have started announcing their new products. Today, Silicon Motion is unveiling their first enterprise-focused PCIe 5.0...

3 by Ganesh T S on 7/28/2022The ASUS ROG Maximus Z690 Hero Motherboard Review: A Solid Option For Alder Lake

Over the last six months since Intel launched its 12th Gen Core series of processors, we've looked at several Alder Lake desktop CPUs and seen how competitive they are...

40 by Gavin Bonshor on 6/15/2022AMD Ryzen 7000 Announced: 16 Cores of Zen 4, Plus PCIe 5 and DDR5 for Socket AM5, Coming This Fall

During the AMD Keynote at Computex 2022, its CEO, Dr. Lisa Su officially unveiled their next generation of Ryzen processors and the successor to the highly successful Ryzen 5000...

333 by Gavin Bonshor on 5/23/2022Samsung Announces First PCIe 5.0 Enterprise SSD: PM1743, Coming In 2022

Even though CES 2022 is technically still a couple of weeks away, CES-related announcements are already starting to roll in. Among these are Samsung, who is announcing their first...

12 by Ryan Smith on 12/23/2021The Intel Z690 Motherboard Overview (DDR4): Over 30+ New Models

To support the launch of Intel's latest 12th generation 'Alder Lake' processors, Intel has also pulled the trigger on its latest Z690 motherboard chipset. Using a new LGA1700 socket...

42 by Gavin Bonshor on 11/24/2021

_carousel.jpg)