DDR5

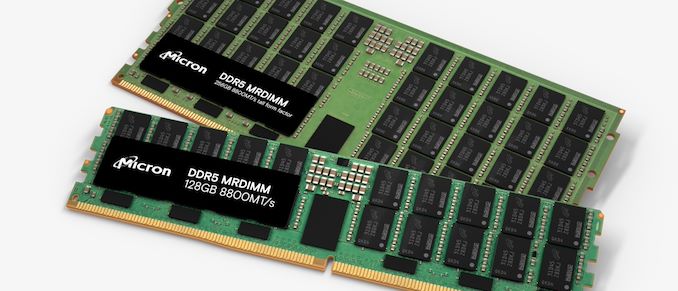

Following a relative lull in the desktop memory industry in the previous decade, the past few years have seen a flurry of new memory standards and form factors enter development. Joining the traditional DIMM/SO-DIMM form factors, we've seen the introduction of space-efficient DDR5 CAMM2s, their LPDDR5-based counterpart the LPCAMM2, and the high-clockspeed optimized CUDIMM. But JEDEC, the industry organization behind these efforts, is not done there. In a press release sent out at the start of the week, the group announced that it is working on standards for DDR5 Multiplexed Rank DIMMs (MRDIMM) for servers, as well as an updated LPCAMM standard to go with next-generation LPDDR6 memory. Just last week Micron introduced the industry's first DDR5 MRDIMMs, which are timed to launch alongside Intel's...

CUDIMM Standard Set to Make Desktop Memory a Bit Smarter and a Lot More Robust

While the new CAMM and LPCAMM memory modules for laptops have garnered a great deal of attention in recent months, it's not just the mobile side of the PC...

26 by Ryan Smith & Anton Shilov on 6/21/2024G.Skill Demonstrates DDR5-10600 Memory Modules On Ryzen 8500G System

Ultra-high performance memory modules are a staple of of Computex, and it looks like this year G.Skill is showing off the highest performance dual-channel memory module kit to date...

7 by Anton Shilov on 6/5/2024JEDEC Extends DDR5 Memory Specification to 8800 MT/s, Adds Anti-Rowhammer Features

When JEDEC released its DDR5 specification (JESD79) back in 2020, the standard setting organization defined precise specs for modules with speed bins of up to 6400 MT/s, while leaving...

14 by Anton Shilov on 4/22/2024Asus Adds Support for 64GB Memory Modules to Intel 600/700 Motherboards

Asus on Thursday said it has released new versions of UEFI BIOS for DDR5-supporting Intel 600/700-series motherboards that enable support for 64 GB DIMMs. As a result, Asus's latest...

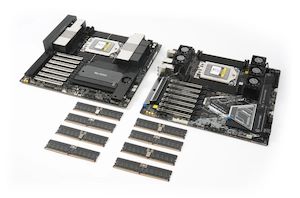

4 by Anton Shilov on 3/14/2024V-Color Has New RDIMM Octo-Kits For Threadripper 7000 CPUs: 768 GB Kits Starting at $4,840

V-Color has launched several EXPO-certified DDR5 RDIMM memory kits for AMD's Ryzen Threadripper 7000 Pro and non-Pro platforms. The new RDIMM memory kits, which only come in an eight-DIMM...

2 by Zhiye Liu on 3/7/2024Rambus Preps Updated RCD for Server-Grade DDR5-7200 Modules

Rambus has introduced its fourth-generation registering clock driver (RCD) chip for server-grade DDR5 memory modules. The updated RCD chip brings support for higher clockspeeds on DDR5 RDIMMs, allowing for...

7 by Anton Shilov on 1/3/2024G.Skill and V-Color Unveil Factory Overclocked ECC RDIMMs for Ryzen Threadripper 7000 [UPDATED]

UPDATE 11/24: Demu, our reader with sharp eyes, notified us that Gigabyte had published a list of overclockable RDIMMs with ECC and AMD EXPO profiles supported by its TRX50...

7 by Anton Shilov on 11/23/2023Micron Introduces 128 GB DDR5-8000 RDIMMs with Monolithic 32 Gb Die

The path to high-capacity RDIMMs for servers has primarily been through 3D stacking (3DS) of DRAM dies using Through-Silicon Vias (TSVs). However, this has presented significant challenges in packaging...

15 by Ganesh T S on 11/9/2023Micron Samples 128 GB Modules Based on 32 Gb DDR5 ICs

Micron is sampling 128 GB DDR5 memory modules, the company said at its earnings call this week. The modules are based on the company's latest single die, non-stacked 32...

9 by Anton Shilov on 9/28/2023Corsair's Dominator Titanium Memory Now Available, Unveils Plans for Beyond 8000 MT/s

Corsair has started sales of its Dominator Titanium memory modules that were formally introduced this May. The new modules bring together luxurious look, customizable design, and extreme data transfer...

1 by Anton Shilov on 9/26/2023Samsung Unveils Industry's First 32Gbit DDR5 Memory Die: 1TB Modules Incoming

Samsung early on Friday revealed the world's first 32 Gb DDR5 DRAM die. The new memory die is made on the company's 12 nm-class DRAM fabrication process and not...

6 by Anton Shilov on 9/1/2023Micron's CZ120 CXL Memory Expansion Modules Unveiled: 128GB and 256GB

This week, Micron announced the sample availability of its first CXL 2.0 memory expansion modules for servers that promise easy and cheap DRAM subsystem expansions. Modern server platforms from...

7 by Anton Shilov on 8/9/2023TeamGroup Unveils JEDEC-Spec DDR5-6400 Memory Kits: Faster 1.1V DDR5 On The Way For Future CPUs

While DDR5 memory has been out and in use for a couple of years now, so far we haven't seen the memory reach its full potential – at least...

5 by Anton Shilov on 7/31/2023Micron Publishes Updated DRAM Roadmap: 32 Gb DDR5 DRAMs, GDDR7, HBMNext

In addition to unveiling its first HBM3 memory products yesterday, Micron also published a fresh DRAM roadmap for its AI customers for the coming years. Being one of the...

4 by Anton Shilov on 7/27/2023G.Skill's 24GB DDR5-6000 Modules with AMD EXPO Profiles Released

G.Skill has quietly started selling its 24 GB DDR5 memory modules with AMD EXPO profiles for single-click overclocking. G.Skill's Trident Z5 Neo RGB modules are among the first EXPO-profiled...

4 by Anton Shilov on 6/28/2023TeamGroup Announces T-Force Xtreem ARGB DDR5 Memory: Up to DDR5-8266

At Computex 2023, TeamGroup unveiled two additions to its extensive family of memory products. Available with ARGB heatsinks or subtle black non-RGB heatsinks, the TeamGroup T-Force Xtreem DDR5 memory...

5 by Gavin Bonshor on 6/2/2023Next-Generation CAMM, MR-DIMM Memory Modules Show Up at Computex

Dynamic random access memory is an indispensable part of all computers, and requirements for DRAM — such as performance, power, density, and physical implementation — tend to change now...

4 by Anton Shilov on 6/2/2023Corsair Unveils Dominator Titanium DDR5 Kits: Reaching For DDR5-8000

Corsair has introduced its new Dominator Titanium series of DDR5 memory modules that will combine performance, capacity, and style. The new lineup of memory modules and kits will offer...

5 by Anton Shilov on 5/30/2023Micron Expects Impact as China Bans Its Products from 'Critical' Industries

In the latest move in the tit-for-tat technology trade war between the United States and China, on Sunday the Cyberspace Administration of China announced that it was effectively banning...

12 by Anton Shilov on 5/23/2023