Cortex-M7 Launches: Embedded, IoT and Wearables

by Stephen Barrett on September 23, 2014 7:01 PM ESTHybrid Systems

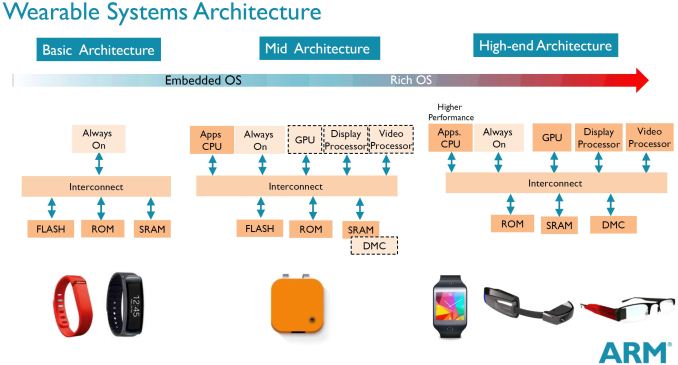

While the Cortex-M series aims to be the MCU for many application markets including IoT and wearables, ARM does not expect M series processors to always be used alone and expects many devices to combine A series application processors with the M seires. When I mentioned the word coprocessor referring to the M series, Nandan quickly pointed out that in this market, the A series might actually be considered the coprocessor. Considering the MCU is the always on device and the A series CPU wakes only sparingly, I can see his point of view. The following diagram from ARM lays out this perspective well.

MediaTek used a much simpler table to describe the sub markets of IoT and wearables that, as I noted at the time, insinuated there was no overlap between MCUs and APs. I tend to agree more with Intel’s Edison platform and ARM’s slide here that there are large market segments that will indeed be combining these differentiated processors.

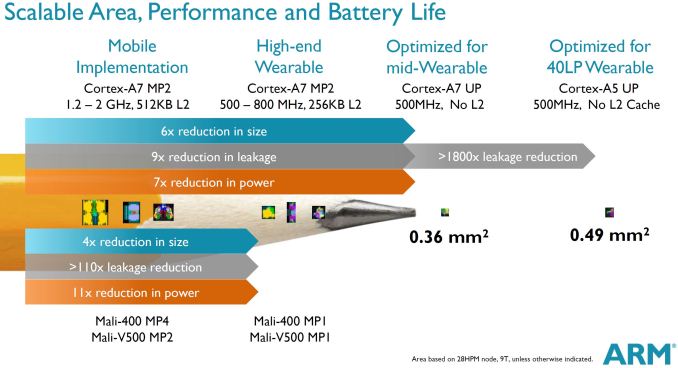

When designing hybrid systems like this for IoT and wearables, it is very important to synthesize the AP with power optimization goals. The process of synthesizing HDL to an ASIC is essentially an optimization problem, much like all engineering. Targeting one aspect of performance, such as power consumption, means you’re willing to sacrifice something else. The prevailing trend so far has been to reuse smartphone processors in wearables. Companies practicing this approach are not optimizing their wearables' power use but are instead optimizing time to market and internal expenses.

To emphasize what this means, when the Cortex A15 launched ARM stated it was optimized for 1.2 GHz operation. When the first smartphone featuring an A15 hit the market it actually ran at much higher voltages to achieve higher frequencies and thus relatively high power consumption. Reusing this chip inside an IoT or wearable device is not only choosing a performance focused CPU instead of a power optimized one like the A7, but it has also been synthesized to further push the CPU away from power efficiency. This is why many wearables today featuring rich operating systems have struggled with battery life. Apple has traditionally been conservative with smart phone SoC power consumption and it will be interesting to see how their new wearable is designed.

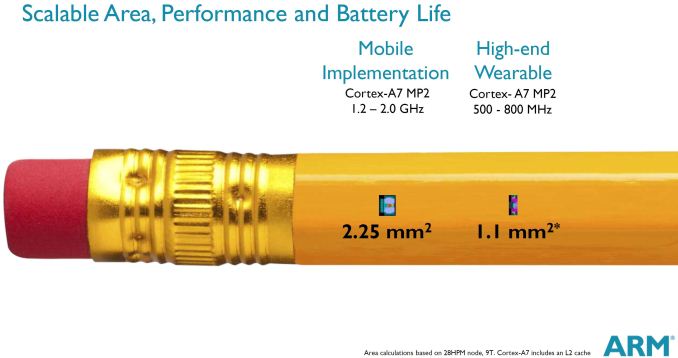

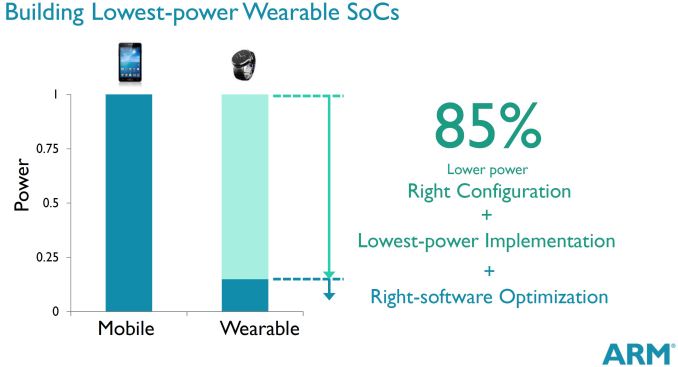

For wearable devices, ARM recommends reducing A series frequency and area by over half, which has a direct effect on power consumption. ARM states that wise choices of CPU cores and caches, synthesis goals, and software optimizations to offload certain tasks to an MCU, can reduce power consumption by as much as 85%. This will be something we will keep an eye on when we review future wearables.

43 Comments

View All Comments

Wilco1 - Thursday, September 25, 2014 - link

It does 2 16-bit MACs per cycle and the graph shows 2x32 interfaces to DTCM, so that should mean it can sustain 2 MACs plus 64-bit load/store per cycle.fteoath64 - Saturday, September 27, 2014 - link

Even on a mid-wearable config, a 500Mhz Soc seems really overkill considering the original iPhone had a 400Mhz Soc and could do all the phone functions except taking speech (this could be done using a small custom DSP on the Soc). For a wearable, it cannot be expected to play video but maybe capture 3 minute video segments at a time. It seems the industry is pushing hardware as an overkill rate just to spur up a new segment of the market. This has led to compromises in battery life due to too much transistor counts and too high frequency chips being used. There was a day when a Pentium 266Mhz was a fast computer. Just our perception of numbers makes us think, it is slow as molluscs today. It ain't that slow. Running Linux, it does nicely.jinish - Tuesday, November 17, 2015 - link

Hi!The post is more than a year old now.. Were you guys able to fetch the area of cortex M7, till date?