Samsung SSD 850 Pro (128GB, 256GB & 1TB) Review: Enter the 3D Era

by Kristian Vättö on July 1, 2014 10:00 AM EST3D NAND: How It Works

To understand how 3D NAND helps to keep Moore's Law in action, we first need to go in-depth with the structure. Before we begin, there are a couple of disclaimers I want to get out. First of all, every manufacturer has a different 3D NAND structure, so to avoid information overflow and confusion, I will only talk about Samsung's structure for now. When other manufacturers are ready with their 3D NAND products, I will provide a similar analysis of their structure. Secondly, there is not much detailed information about Samsung's 3D NAND, or V-NAND as they call it, so I am mostly basing my analysis on The Memory Guy's blog post (also known as Jim Handy, a respected semiconductor analyst).

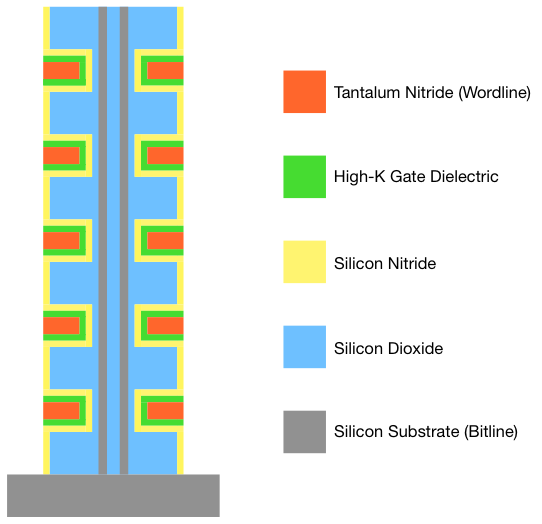

What you are seeing above is a 5-layer 3D NAND string based on Samsung's TCAT (Terabit Cell Array Transistor) structure. It consists of a total of ten cells and similar to 2D NAND each cell is capable of holding one, two or three bits of data depending on whether the NAND is SLC, MLC or TLC. Samsung's current (i.e. second) generation V-NAND has 32 layers, meaning that it is simply a taller tower but to keep the graph easily readable I decreased the number of layers to five.

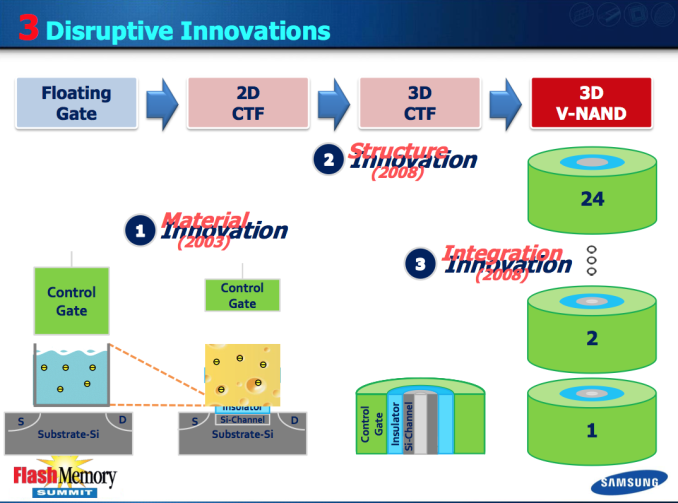

There is one fundamental difference between Samsung's V-NAND. With 2D NAND, the charge was stored in a conductive floating gate but as you can see in the graph above, there is not one in Samsung's V-NAND. Instead Samsung uses a design called Charge Trap Flash (CTF), which means that the charge is stored in an insulator, which is silicon nitride in this case.

Some of you might remember this rather hilarious slide we used in our V-NAND announcement article and I now have an explanation as to why Samsung used cheese in in (yes, it indeed is cheese). A traditional floating gate works pretty much like a bucket of water. As long as there is not a hole in the bucket, the water stays there without an issue. However, if you get even a tiny hole in the bucket, all the water will sooner than later escape through that hole. It is the same with a floating gate because if there is a hole in the insulating material around it (Inter Poly Dielectric and tunnel oxide), all the electrons in the floating gate will escape through that as the floating gate is conductive and the electrons can move freely. As I mentioned on the previous page, this is exactly what happens when NAND is cycled and wears out because the stress caused by the programming operation causes the insulators to lose their insulating characteristics.

With Charge Trap Flash that does not happen because the electrons reside in an insulator. Samsung compared the bucket of water idea to cheese, meaning that if there is a hole the cheese will not just pour out from it like water would.

As a result, Charge Trap Flash increases endurance as it is not as vulnerable to wear out. I am also told that CTF does not require as high programming voltages as floating gates do (up to 20V), which reduces the stess on the insulators. I wonder if this is simply because the insulators do not have to be that thick anymore (a miminum of 7nm for tunnel oxide and 12nm for ONO) because the charge trap is not as dependent on the surrounding insulators as floating gate is. The reason why such a high voltage is needed for 2D NAND programming is the thickness of the tunnel oxide because otherwise the electrons cannot tunnel through (remember, the electrons are shot through an insulator). On the other hand, the tunnel oxide cannot be made any thinner than 7nm or otherwise data retention takes a massive hit (NAND is really an engineers dream, isn't it? Touch one thing and you break another).

Another interesting tidbit regarding Samsung’s V-NAND is the usage of a high-K dielectrics. IMFT did a similar switch when they moved to 20nm node but all the other manufacturers, as far as I know, have stayed with an inter poly dielectric (IPD) design. I went into detail about high-K dielectrics in our Crucial MX100 review but I will provide a quick summary here. Basically, a high-K dielectric is a material with a high dielectric constant, which is quite surprisingly known as K. The benefit of a high-K dielectric over a normal dielectric (like oxide-nitride-oxide i.e. ONO in NAND) is that it provides a higher capacitance between the word and bitlines. Similar to 2D NAND, the capacitance between the control gate and the floating gate, or charge trap in the case of V-NAND, is still the key factor for operation. The usage of high-K dielectrics gives Samsung a bit more headroom in terms of vertical scaling as layers can be stacked closer to each other and it also improves endurance as high-K dielectrics have less leakage compared to normal dielectrics.

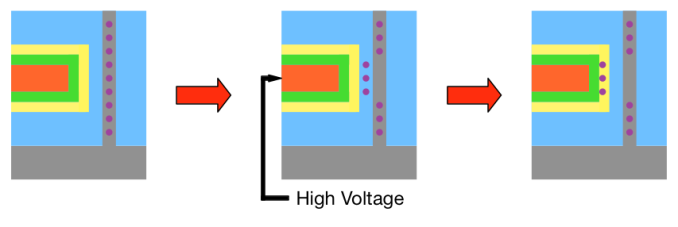

Otherwise the basics of V-NAND are very similar to 2D NAND. To program a cell, the bitline is grounded (i.e. held at 0V) while a high voltage is placed on the wordline. That makes the electrons that are floating in the bitline to tunnel through the silicon dioxide to the charge trap a.k.a. silicon nitride.

I made a very simple graph of V-NAND programming, which should help you to understand the process. The elements are the same as in the tower graph with the difference that it is just one layer and I cut the tower in half to fit it on the page. The purple balls are electrons.

Reading from V-NAND works exactly the same as with 2D NAND. The wordline of the cell-to-be-read is held at 0V while different voltages are applied on the bitline. Once the correct voltage is found, the cell will conduct and the sense amp will read the data depending on what the voltage was (the voltage determines the voltage state, i.e. what the value is).

160 Comments

View All Comments

Pastuch - Wednesday, July 2, 2014 - link

When will we see Vnand in smart phones? This 16gb Nexus 5 is brutal! Always out of space.ajlueke - Wednesday, July 2, 2014 - link

Page 1, "Scaling below 20nm was seemed", I believe you intended "Scaling below 20nm was seen".Automaticman - Wednesday, July 2, 2014 - link

Can current EVO 840 users upgrade to Magician 4.4 and get the benefits of RAPID 2.0 (assuming they have >16GB DRAM)?bsd228 - Wednesday, July 2, 2014 - link

just as RAPID support was extended to the 840 PRO, I would expect this to support the 840 pro/evo soon, if not right off the bat.Automaticman - Sunday, July 6, 2014 - link

Well, I was certainly able to upgrade to Magician 4.4, and it did take a couple reboots while it was re-activating RAPID. I am going to guess and say yes it seems to be the new version of RAPID, but I don't see anywhere that it actually says RAPID 2.0 or any indication of how much memory it has available.sirvival - Wednesday, July 2, 2014 - link

Ah ok.When I select the 470 in Bench there is no slumber so I got confused.

Since power cosumption is a big thing in Mobile could you do the following:

Bench the impact on the Battery of a Laptop due to a fast drive.

E.g. drive A is fast but has the downside that it draws more under load as drive B which is slower. But since its done faster it returns to idle faster.

I mean impact on real world scenarios.

Or how much power was used for bench x etc. and have a average per hour or something like that.

sirvival - Wednesday, July 2, 2014 - link

damn this was to be a reply tohttp://www.anandtech.com/comments/8216/samsung-ssd...

sorry

Nickat - Thursday, July 3, 2014 - link

Thank you so much. You explained everything so well.Stokkolm - Thursday, July 3, 2014 - link

Newegg still has them for preorder at the more expensive price, hopefully they drop those before the release date.skarthikeyan - Monday, July 7, 2014 - link

Hi, How come random read is 106.8MB/sec and random write is 292.4MB/sec for the SSD 850 Pro 256 GB? Aren't writes supposed to be slower than reads?