Samsung SSD 850 Pro (128GB, 256GB & 1TB) Review: Enter the 3D Era

by Kristian Vättö on July 1, 2014 10:00 AM EST3D NAND: Hitting The Reset Button on Scaling

Now that we understand how 3D NAND works, it is time to see what it is all about. As we now know, the problem with 2D NAND is the shrinking cell size and the proximity of the cells, which results in degraded reliability and endurance. Basically, 3D NAND must solve these two issues but it must also remain scalable to be economical. So how does it do that? This is where the third dimension comes into play.

The cost of a semiconductor is proportional to the die size. If you shrink the die, you effectively get more dies from a single wafer, resulting in a lower cost per die. Alternatively you can add more functionality (i.e. transistors) to each die. In the case of NAND, that means you can build a higher capacity die while keeping the die size the same, which gives more gigabits per wafer and thus reducing cost. If you cannot shrink the die, then you have just hit a dead-end because the cost will not scale. That is what has happened with 2D NAND because the shrinks on X and Y axes have run out of gas.

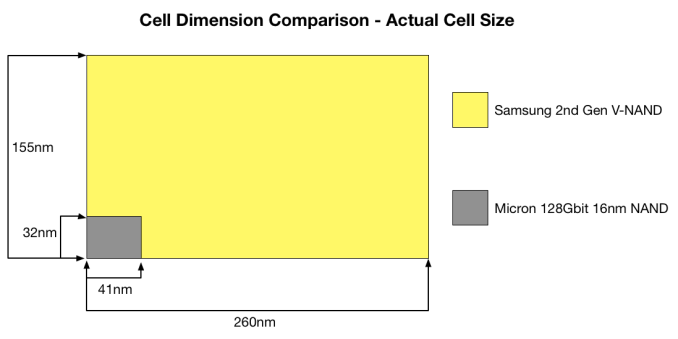

What 3D NAND does is add a Z-axis to the game. Because it stacks cells vertically, it is no longer as dependent on the X and Y axes since the die size can be reduced by adding more layers. As a result, Samsung's V-NAND takes a more relaxed position on the X and Y axes by going back to a 40nm process node, which increases the cell size and leaves more room between individual cells, eliminating the major issues 2D NAND has. The high amount of layers compensates for the much larger process node, resulting in a die that is the same size and capacity as the state of the art 2D NAND dies but without the caveats.

The above graph gives some guidance as to how big each cell in V-NAND really is. On the next page, I will go through the method of how cell size is really calculated and how V-NAND compares with Micron’s 16nm NAND but the above gives a good picture of the benefit that 3D NAND has. Obviously, when each cell is larger and the distance between individual cells is higher, there are more electrons to play with (i.e. more room for voltage state changes) and the cell to cell interference decreases substantially. Those two are the main reasons why V-NAND is capable of achieving up to ten times the endurance of 2D NAND.

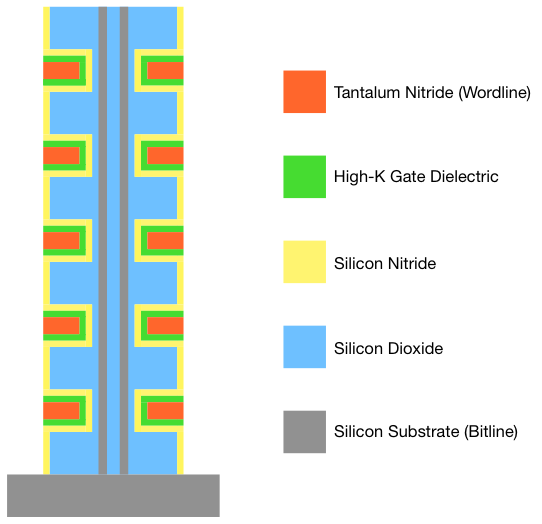

Moreover, scaling in vertical dimension does not have the same limitations as scaling in the X and Y axes do. Because the cost of a semiconductor is still mostly determined by the die area and not by the height, there is no need to cram cells very close to each other. As a result, there is very little interference between the cells even in the vertical direction. Also, the usage of high-K dielectrics means that the control gate does not have to wrap around the charge trap. The result is that there is a hefty barrier of silicon dioxide (which is an insulator) between each cell, which is far more insulating than the rather thin ONO layer in 2D NAND. Unfortunately, I do not know what is the exact distance between each cell in the vertical dimension but I think it is safe to assume that it is noticeably more than the ~20nm in 2D NAND since there is no need for aggressive vertical scaling.

As for how far Samsung believes their V-NAND can scale, their roadmap shows a 1Tbit die planned for 2017. That is very aggressive because it essentially implies that the die capacity will double every year (256Gbit next year, 512Gbit in 2016 and finally 1Tbit in 2017). The most interesting part is that Samsung is confident that they can do this simply by increasing the layer count, meaning that the process node will stay at 40nm.

160 Comments

View All Comments

Homeles - Monday, June 30, 2014 - link

Man, the 850 Pro is killer. Samsung really knocked it out of the park. Those prices are just completely out of touch, though.Awful - Monday, June 30, 2014 - link

Yeah the prices are high for now. Game changing stuff though; and prices can only come down. PCIe V-NAND? Yes please!Hung_Low - Tuesday, July 1, 2014 - link

Even better, Intel style NVMe controller + this v-nand!! orgasmicavyshue - Tuesday, July 1, 2014 - link

yeah, i've been holding off on upgrading from my existing 128 boot drive + mechanical setup to a full 1TB drive. I think I'll keep holding out until PCIe is better supported/better priced.Angrychair - Tuesday, July 1, 2014 - link

The prices are in line for class leading performance and reliability.The reliability is the critical part, these are drives that are unlikely to wear out in any system almost no matter how heavily taxed.

Ken_g6 - Tuesday, July 1, 2014 - link

I see these are MLC drives. Hopefully, Samsung will come out with consumer-level 3D TLC drives that have relatively good reliability, and a price at or below Crucial's drives.frenchy_2001 - Tuesday, July 1, 2014 - link

Reliability is a side effect of retreating to 40nm pitch technology.Even if they decided to do TLC with the same cells, they would probably end up being more reliable than 2D nand MLC.

joelypolly - Thursday, July 3, 2014 - link

They already have drives in testing that has written over 8 petabytes so I think the reliability is theremkozakewich - Saturday, July 5, 2014 - link

On that note, I'm wondering how 4-bit MLC would perform compared to 2D NAND.RaistlinZ - Monday, June 30, 2014 - link

Fantastic drives! That consistency is really remarkable. I don't know if most will pay the price premium for these over the EVO however. The average user probably wouldn't notice a difference in general day to day use.