The Haswell Ultrabook Review: Core i7-4500U Tested

by Anand Lal Shimpi on June 9, 2013 9:00 AM ESTHaswell ULT: Platform Power Improvements

Over the past several years, Intel’s maniacal focus on reducing CPU power almost entirely ignored the rest of the platform. Even its own chipsets were often on high power process nodes (remember the first Atom’s 2.5W TDP, but with a 6W chipset TDP). This all changes with Haswell, at least with the ULT/ULX flavors.

I already went through the chipset/PCH changes. The move to 32nm and bringing the PCH on-package will help with power tremendously. But with Haswell, Intel looked beyond its own silicon to other controllers on the motherboard for opportunistic power savings.

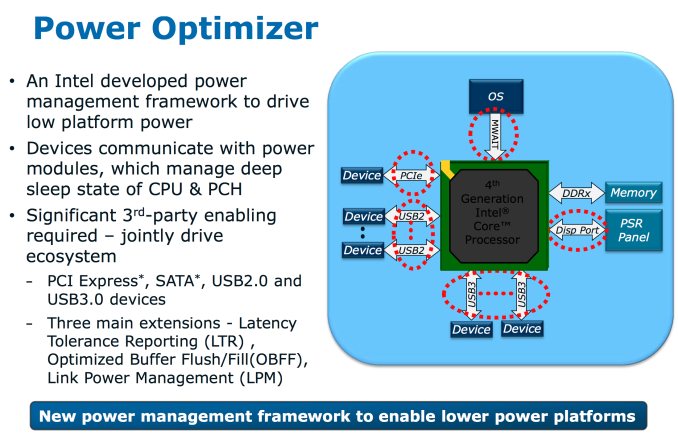

With Haswell, Intel deploys its new platform power management framework called Power Optimizer. Its goal? To deliver S3 (suspend to RAM) style power savings, at S0 (active) style latency.

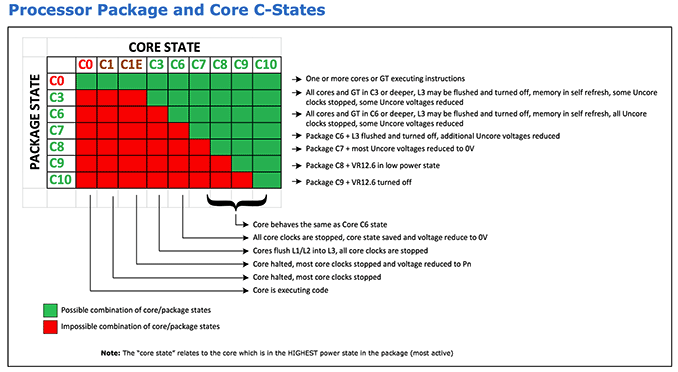

On the CPU, Intel had to dramatically increase its ability to turn blocks on/off, as well as quickly enter/exit its own low power states. Haswell’s FIVR (Fully Integrated Voltage Regular) helps tremendously in this regard as it can quickly switch between voltage states (Intel claims 5x - 10x faster than off-package VR). Haswell as a result can more aggressively choose to go down to lower power states because it can come out of them very quickly. Haswell ULT/ULX support lower core and package C-states. The entire SoC can now be power gated in C10, where the rail that feeds FIVR can be shut off.

For the rest of the platform though, Intel did what the PC industry is best known for: designing a spec and asking others to implement it.

PCIe, SATA, USB 3, DisplayPort are all touched by Power Optimizer. Devices on these busses can report latency tolerance to the PCH (how long can I sleep without breaking everything), and based on that information the PCH can determine how frequently everything has to wake up to avoid impacting user experience.

Haswell will take all of the latency tolerance information into account and coordinate system wide sleep/wake based on the least common denominator. The idea is that during idle periods, there’s no reason that most of the platform components can’t be driven down to their lowest power states as if your notebook lid was shut; especially as long as they can quickly wake up when needed. Intel calls this platform level active idle state S0ix, and it’s only supported on Haswell ULT/ULX. In the past Intel had referred to multiple S0ix states, but it looks like Intel is trying to move away from that nomenclature. Effectively now there’s just S0 and S0ix in terms of active power states.

Obviously all it takes is a single 3rd party component to ruin everything, so Intel has worked with device and microcontroller manufacturers to help improve their power profiles as well. Intel’s Power Optimizer architecture is very robust. Intel plans on working with platform vendors regularly to improve power. There are no more easy power gains; going forward, reducing power is going to require a much more collaborative effort from all the power consumers on the platform.

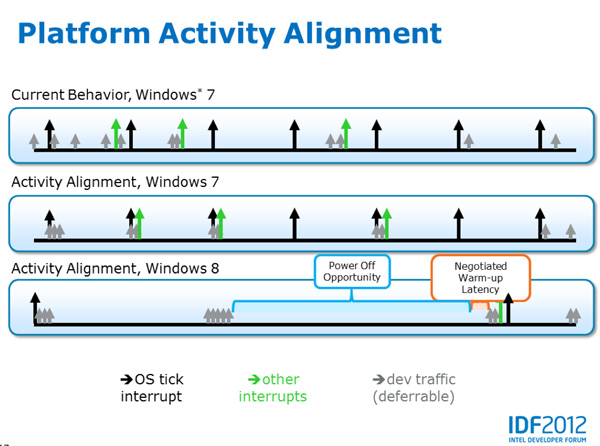

Windows 8 also plays a significant role in all of this as the OS supports coalescing of tasks in software to ensure that it isn’t working against Intel’s Power Optimizer in hardware.

If the CPU/SoC and much of the motherboard can aggressively drive down to S3-like idle power, the display becomes an even bigger burden than it has in the past. To allow the entire platform to go to sleep while the display is still active, Intel recommends Panel Self Refresh (PSR) to be implemented in Haswell Ultrabooks. The idea behind PSR is to put DRAM on the panel itself to store the frame buffer. In the event of a static display (e.g. staring at a Word document, looking at your desktop), the GPU frame buffer is copied to the panel’s DRAM, and the GPU itself is shut off instead of having to drive meaningless content updates to the display 60 times per second. With PSR, the SoC can go into its deepest sleep state (C10).

No Connected Standby for Now

Although you should be able to realize some of the benefits from S0ix with the first Haswell Ultrabooks, Connected Standby (periodic content refresh while in a sleep state) requires OS support. For Haswell Ultrabooks, that means waiting for Windows 8.1.

Even on the S0ix side, it’s not clear to me whether all of the devices in the system capable of going into D3 (their lowest power state) while active will actually do so until Windows 8.1. I get the distinct impression that Haswell Ultrabooks will see a tangible increase in battery life with Windows 8.1.

87 Comments

View All Comments

warezme - Monday, June 10, 2013 - link

"the processor graphics story by finally delivering discrete GPU class gaming performance". I hate this summation being thrown around, as I'm sure it will get re quoted somewhere as gospel. It is definitely NOT discrete GPU class gaming performance in any shape or form. There should be a limit to what is considered discrete GPU performance, like maybe 30-60FPS at, at least 1600x900 resolution and game settings across the board for all games set to Medium. That is not crazy or unreasonable for a true discrete GPU you would actually go out and buy. It shouldn't be unreasonable than to expect that in a built in GPU that is sold as "discrete GPU" quality.gnx - Monday, June 10, 2013 - link

Kudos! You have to love AnandTech for providing such detailed analysis, so soon after Haswell was made public!But it does seem that Haswell for Ultrabooks isn't so revolutionary as Intel seemed to imply. Not that we have much of a choice, since ARM isn't an option, and AMD doesn't provide much of an alternative, but I was personally hoping for more from Haswell.

Maybe it's change the equation for Windows Tablets? look forward to more from AnandTech!

Kiijibari - Monday, June 10, 2013 - link

Can you please add Wh numbers in the Battery Life Test graph (http://images.anandtech.com/graphs/graph7047/55504... or normalize them at least like in the previous tables? Seems to me that you compare 2 different batteries there. Haswell is great sure, but not THAT great ;-)Yes it is explained in the text below, but a picture not matching the numbers in the text is useless and misleading. A picture should be worth more than 1000 words and not demand reading 1000 words of explanation ;-)

broccauley - Tuesday, June 11, 2013 - link

Does anyone know what the status of "activity alignment" for power optimisation is on the Linux kernel and how it compares with Windows 8? I assume such techniques were added when the changes from the Android branch were merged?Henry 3 Dogg - Tuesday, June 11, 2013 - link

"And today, we had to track down a pre-production Haswell Ultrabook in Taiwan to even be able to bring you this review of Haswell ULT."And today, a day later, you can pick up a production Haswell ULT based MacBook Air in your local Apple store.

lhurt - Tuesday, June 11, 2013 - link

So are Platform Activity Manager (Windows) and Timer Coalescing (OSx) two different OS implementations of the same idea, to take advantage of Intel's Power Optimizer and are Haswell cpus required to get the benefit?fteoath64 - Saturday, June 15, 2013 - link

"Any hopes for pairing a meaningfully high performance discrete GPU with Haswell ULT are dead."This is Intel's method of CLOSING other discrete GPU solution on their cpus towards the future. This is a predatory move and premeditated !. Just stop buying their chips as this is forcing users into a proprietary path using their inferior gpu technology. It is a selfish and disgusting move. Now ARM is going to cream them on the desktop side as well soon and server side in time.