AMD Radeon HD 7970 Review: 28nm And Graphics Core Next, Together As One

by Ryan Smith on December 22, 2011 12:00 AM EST- Posted in

- GPUs

- AMD

- Radeon

- ATI

- Radeon HD 7000

PCI Express 3.0: More Bandwidth For Compute

It may seem like it’s still fairly new, but PCI Express 2 is actually a relatively old addition to motherboards and video cards. AMD first added support for it with the Radeon HD 3870 back in 2008 so it’s been nearly 4 years since video cards made the jump. At the same time PCI Express 3.0 has been in the works for some time now and although it hasn’t been 4 years it feels like it has been much longer. PCIe 3.0 motherboards only finally became available last month with the launch of the Sandy Bridge-E platform and now the first PCIe 3.0 video cards are becoming available with Tahiti.

But at first glance it may not seem like PCIe 3.0 is all that important. Additional PCIe bandwidth has proven to be generally unnecessary when it comes to gaming, as single-GPU cards typically only benefit by a couple percent (if at all) when moving from PCIe 2.1 x8 to x16. There will of course come a time where games need more PCIe bandwidth, but right now PCIe 2.1 x16 (8GB/sec) handles the task with room to spare.

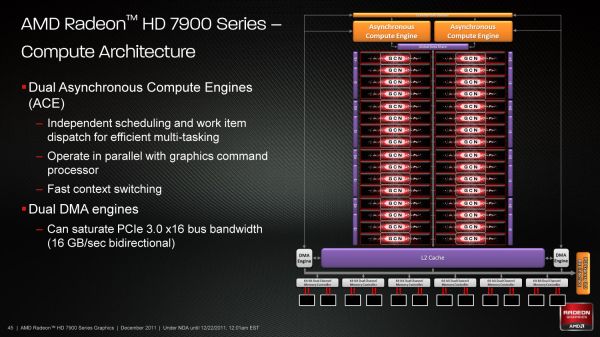

So why is PCIe 3.0 important then? It’s not the games, it’s the computing. GPUs have a great deal of internal memory bandwidth (264GB/sec; more with cache) but shuffling data between the GPU and the CPU is a high latency, heavily bottlenecked process that tops out at 8GB/sec under PCIe 2.1. And since GPUs are still specialized devices that excel at parallel code execution, a lot of workloads exist that will need to constantly move data between the GPU and the CPU to maximize parallel and serial code execution. As it stands today GPUs are really only best suited for workloads that involve sending work to the GPU and keeping it there; heterogeneous computing is a luxury there isn’t bandwidth for.

The long term solution of course is to bring the CPU and the GPU together, which is what Fusion does. CPU/GPU bandwidth just in Llano is over 20GB/sec, and latency is greatly reduced due to the CPU and GPU being on the same die. But this doesn’t preclude the fact that AMD also wants to bring some of these same benefits to discrete GPUs, which is where PCI e 3.0 comes in.

With PCIe 3.0 transport bandwidth is again being doubled, from 500MB/sec per lane bidirectional to 1GB/sec per lane bidirectional, which for an x16 device means doubling the available bandwidth from 8GB/sec to 16GB/sec. This is accomplished by increasing the frequency of the underlying bus itself from 5 GT/sec to 8 GT/sec, while decreasing overhead from 20% (8b/10b encoding) to 1% through the use of a highly efficient 128b/130b encoding scheme. Meanwhile latency doesn’t change – it’s largely a product of physics and physical distances – but merely doubling the bandwidth can greatly improve performance for bandwidth-hungry compute applications.

As with any other specialized change like this the benefit is going to heavily depend on the application being used, however AMD is confident that there are applications that will completely saturate PCIe 3.0 (and thensome), and it’s easy to imagine why.

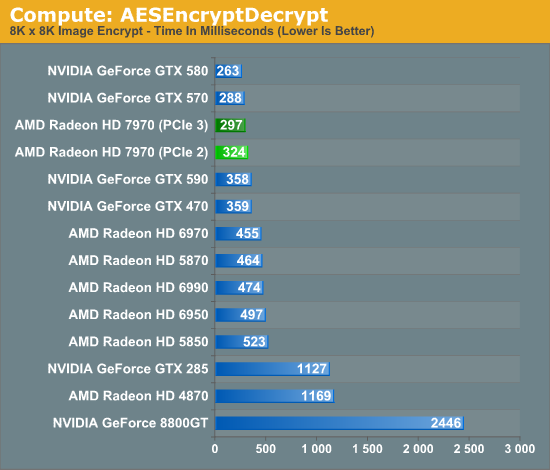

Even among our limited selection compute benchmarks we found something that directly benefitted from PCIe 3.0. AESEncryptDecrypt, a sample application from AMD’s APP SDK, demonstrates AES encryption performance by running it on square image files. Throwing it a large 8K x 8K image not only creates a lot of work for the GPU, but a lot of PCIe traffic too. In our case simply enabling PCIe 3.0 improved performance by 9%, from 324ms down to 297ms.

Ultimately having more bandwidth is not only going to improve compute performance for AMD, but will give the company a critical edge over NVIDIA for the time being. Kepler will no doubt ship with PCIe 3.0, but that’s months down the line. In the meantime users and organizations with high bandwidth compute workloads have Tahiti.

292 Comments

View All Comments

GTVic - Thursday, December 22, 2011 - link

The first Fermi version they demo'd was a mock-up held together with wood screws. That is not a good launch...RussianSensation - Thursday, December 22, 2011 - link

And the real launch version produced Tessellation performance that took HD7970 to pass, had compute performance that HD7970 can barely best today, had Mega Texture support that HD7970 just added now 2 years later, had scalar SIMD architecture that took AMD 2 years to release.Scali - Friday, December 23, 2011 - link

HD7970 doesn't actually surpass Fermi's tessellation, apart from tessellation factors 10 and below:http://www.pcgameshardware.de/aid,860536/Test-Rade...

From factor 11 to 64, Fermi still reigns supreme.

(This is with AMD's SubD11 sample from the DirectX 11 SDK).

Scali - Friday, December 23, 2011 - link

Uhhh no. They demo'ed a real Fermi obviously.It was just a development board, which didn't exactly look pretty, and was not in any way representative of the card that would be available to end-users.

So they made a mock-up to show what a retail Fermi WOULD look like, once it hits the stores.

Which is common practice anyway in the industry.

fllib19554 - Thursday, January 12, 2012 - link

off yourself cretin.futurepastnow - Thursday, December 22, 2011 - link

You misspelled "impressive."slayernine - Thursday, December 22, 2011 - link

What Wreckage really meant to say was that it was disappointing for nVidia to get pummelled so thoroughly.unaligned - Friday, December 23, 2011 - link

A year old card pummeled by the newest technology? I would hope so.MagickMan - Thursday, December 22, 2011 - link

Go shoot yourself in the face, troll.rs2 - Thursday, December 22, 2011 - link

Yes, yes. 4+ billion transistors on a single chip is not impressive at all. Why, it's not even one transistor for every person on the planet yet.