Intel Unveils Meteor Lake Architecture: Intel 4 Heralds the Disaggregated Future of Mobile CPUs

by Gavin Bonshor on September 19, 2023 11:35 AM ESTSoC Tile, Part 3: Disaggregating Xe Media and Display Engine From Graphics

As we noted earlier, Intel has completely redesigned its graphics, media, and display engine for Meteor Lake and, as such, separates all three entities from each other. While we'll cover the new graphics tile next, we'll start with everything that's not part of the graphics tile. Opting for a disaggregated architecture allows Intel to not only shuffle things around from an IP perspective but also allows Intel to integrate new IPs such as cores, graphics, and I/O as and when advancements have been made at a silicon level, but the design allows unties Intel from being limited to a specific manufacturing process.

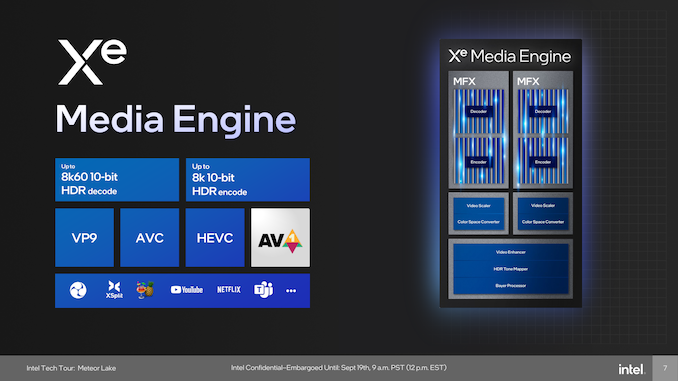

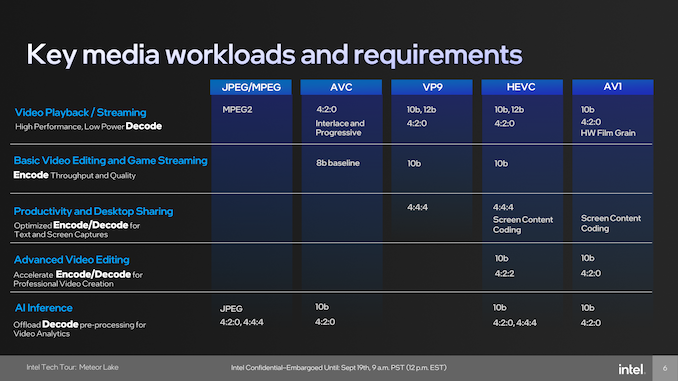

Starting things off, we have the Xe Media Engine, which is embedded within the SoC tile. Within the Xe Media Engine are two Multi-Format Codecs (MFX), designed and responsible for all the encoding and decoding tasks. Intel's Meteor Lake with Xe supports the latest codecs ranging from AV1 (decode and encode), HEVC, AVC, and VP9, with up to 8K60 HDR decode supported. For encoding, there's support for up to 8K resolutions with 10-bit color and HDR. Aiming to improve power efficiency on-chip with encode/decode workloads, having a dedicated Media Engine separate from the graphics allows Intel to find granular power savings as things are directed to the Xe Media Engine, which means the graphics tile doesn't need to be powered up to accomplish encode or decode tasks.

The Xe Media Engine provides various functionalities across a large spectrum of different video codecs. This ranges from JPEG/MPEG and AVC to the more advanced VP9, HEVC, and AV1 codecs. Designed to give Meteor Lake a solid level of computational efficiency for video processing, the Xe Media Engine balances the gaps between high-performance output and power efficiency, rendering it particularly well-suited for various applications, from real-time video streaming to high-fidelity playback. There's also support for diverse color formats and bit depths, including but not limited to 4:2:0 at 10-bit and 12-bit, which means it's versatile for video editing and video encoding and should satisfy content creator's needs.

Xe Display Engine: Also Within the SoC

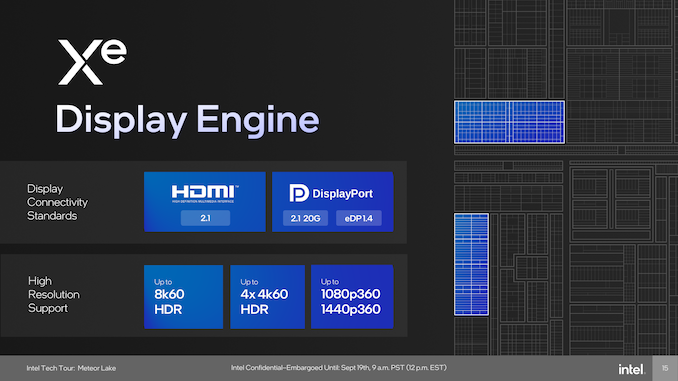

Much like the Xe Media Engine, the Xe Display Engine is also found within the SoC tile on Meteor Lake. Decoupling this directly from the graphics tile and embedded into the SoC allows it to communicate directly with the Xe Media Engine, saving power and improving overall battery life. The engine supports up to four display pipes, two of which have been designed and optimized for low power consumption, further boosting overall efficiency for Meteor Lake.

Looking at compatibility, the Xe Display Engine looks to use the latest connections and ports, including native support for HDMI 2.1, DisplayPort 2.1, Embedded DisplayPort (eDP) 1.4. and even DSC 1.2a. Via these blocks, Meteor Lake can support displays up to 8K60 HDR, or up to 4 x 4K60 HDR displays, and this is on top of 1080p360 and 1440p360 too. This gives Meteor Lake substantial display and multimedia device support, including current and up-and-coming panels.

107 Comments

View All Comments

PeachNCream - Thursday, September 21, 2023 - link

Nice trolling lemur! You landed like an entire page of nerd rage this time. You're a credit to your profession and if I could give you an award for whipping dead website readers into a frenzy (including regulars who have seen you do this for years now) I would. Congrats! 10/10 would enjoy again.IUU - Thursday, September 28, 2023 - link

Intel does not need to do anything about its architecture to to match or surpass m3. It just needs to build its cpus on a similar node. Which is not happening anytime soon, thus perpetuating the illusion of efficiency of apple cpus.Two things more. First it is hilarious to compare the prowess of Intel on designing cpus to that of Apple. Apple has long time "building" machines like a glorified Dell borrowing cpus from IBM or Intel and only recently understood the scale and effort needed to design your silicon by improving on ARM designs.

Secondly, it is misguided to say that if a cpu needs 10 times more wattage on the same node to achieve 2 or 3 times the performance is less efficient. This is not how physics works . If Intel built their cpus on N3 of tsmc they would be 2 or 3 times faster best case scenario. Wattage does not scale linearly with performance. This is the same as saying that a car that has 10 times the power would be 10 times faster. Lololol.

Apple designs good cpus recently , but all the hype about its efficiency is just hype. Even if we assume the design is totally coming from Apple , which it doe not, being a very good modification at best, it does not even build its nodes. By large its efficiency is TSMC efficiency. If it were not for TSMC Apple would be non existent on the performance charts.

Silma - Tuesday, September 19, 2023 - link

TLDR:- Intel 4 < TSMC N6

- To not be late, Intel 3 must arrive within 3 months,which is highly doubtful, since Intel 4 isn't even shipping yet

- I assume Intel 3 < TSMC N6, otherwise, why bother enriching the competition?

- Parts of the new tech stack looks promising, but Intel refrains from any real performance claims, or any comparison with offerings from AMD or Apple.

- Did Intel announce another architecture for desktop computers, probably more similar to that of AMD, e.g. perhaps many performance tiles plus one cache tile?

Drumsticks - Tuesday, September 19, 2023 - link

Maybe. Or maybe TSMC6 is cheaper, and Intel doesn't need the power savings or area savings of I4 over TSMC6 for what the non-compute tiles need to accomplish. It's not exactly uncommon to see the SoC / IO tile on a lower node, doesn't AMD do the same thing?Roy2002 - Tuesday, September 19, 2023 - link

Intel 4 and 3 are basically the same with the same device density as 3 is enhanced 4. I assume it has slightly higher density value than TSMC 5nm and performance is slightly better. Let's see.kwohlt - Tuesday, September 19, 2023 - link

Intel 4 is not library complete. It can't be used for the SoC tile.sutamatamasu - Tuesday, September 19, 2023 - link

I wonder if current processor have an dedicated NPU, then what the heck happen with GNA?It still in there or they're remove it?

Exotica - Tuesday, September 19, 2023 - link

Intel should've either implemented TB5 in Meteor Lake or waited until after Meteor Lake shipped to announce TB5. Because as cool and impressive as meteor lake seems, for some of us, it's already obsolete in that it makes no sense to buy a TB4 laptop/PC and instead wait on TB5 silicon to hit the market.FWhitTrampoline - Tuesday, September 19, 2023 - link

Why use TB4 or USB4/40Gbs and have to deal with the extra latency and bandwidth robbing overhead compared to PCI-SIG's OCuLink that's just pure PCIe signalling delivered over an external OCuLink Cable. OCuLink and PCIe requires no extra protocol encapsulation and encoding/decoding steps at the PCIe link stage so that's lower latency there compared to USB4/TB4 and later generations that have to have extra encoding/decoding of any PCIe protocol packets to send that out over TB4/USB4. And for external GPUs 4 lanes of PCIe 4.0 connectivity can provide up to 64Gbs of bandwidth over an OCuLink port/cable and OCuLonk ports can be 8 PCIe lanes and wider there.Once can obtain an M.2/NVMe slot to OCuLink adapter and get an external OCuLink connection of up to 64Gbs as long as the M.2 is 4, PCIe 4.0 lanes wide and no specialized controller chip required on the MB to drive that. And GPD on their Handhelds offers a dedicated OCuLiink port and an external portable eGPU that supports OCuLink or USB4/40Gbs-TB interfacing. TB5 and USB4-V2 will take years to be adopted whereas OCuLink is just PCIe 3.0/4.0 there delivered over an external cable.

Exotica - Tuesday, September 19, 2023 - link

Unlike thunderbolt, Occulink doesn't have hotplugging, meaning your device must be connected at cold boot. Not so good for external storage needs.