The Intel 12th Gen Core i9-12900K Review: Hybrid Performance Brings Hybrid Complexity

by Dr. Ian Cutress & Andrei Frumusanu on November 4, 2021 9:00 AM ESTCPU Tests: Core-to-Core and Cache Latency, DDR4 vs DDR5

Starting off with the first of our synthetic tests, we’re looking into the memory subsystem of Alder Lake-S, as Intel has now included a great deal of changes to the microarchitecture, both on a chip-level, as well as on a platform-level due to the new DDR5 memory compatibility.

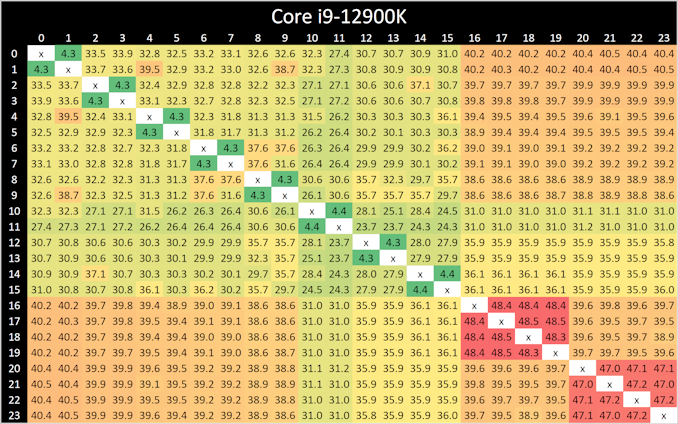

In our core-to-core latency test which showcases the physical topology of the chip, there’s a few things to note. Beginning with the P-cores, which are logically enumerated in the operating system as cores 0 to 15, we can see that latencies are about the same as what we’ve seen on Rocket Lake, although with a few nanosecond differences in the results. The latencies appear to be a bit more topologically uniform, which might indicate that Intel might have finally gotten rid of their uni-directional coherency snoop ring for a bi-directional one.

Latencies between the SMT siblings are also interesting as they decrease from 5.2ns on the Willow Cove cores to 4.3ns on the new Golden Cove cores. The actual L1 access latencies haven’t changed between the two microarchitectures, which means that Intel has improved the LOCK instruction cycle latency.

Between the Golden Cove cores and the smaller Gracemont cores we see higher latencies, as that was to be expected given their lower clock speeds and possible higher L2 overhead of the Gracemont cluster.

What’s however a bit perplexing is that the core-to-core latencies between Gracemont cores is extremely slow, and that’s quite unintuitive as one would have expected coherency between them to be isolated purely on their local L2 cluster. Instead, what seems to be happening is that even between two cores in a cluster, requests have to travel out to the L3 ring, and come back to the very same pathway. That’s quite weird, and we don’t have a good explanation as to why Intel would do this.

Cache Latencies and DDR5 vs DDR4

Next up, let’s take a look at the new cache hierarchy of Alder Lake, both from the view of the Golden Cove cores as well as the Gracemont cores, in DDR5 as well as DDR4.

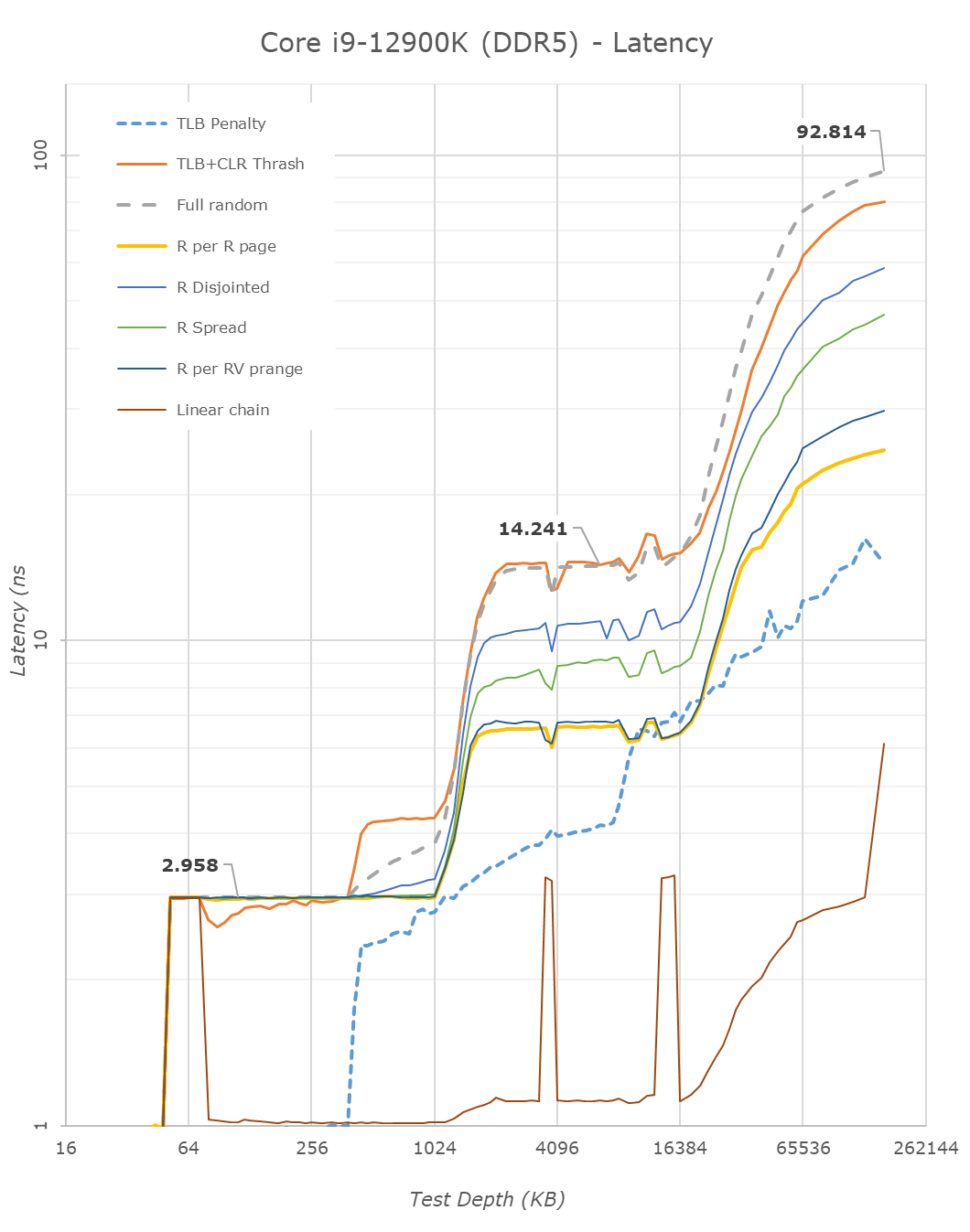

Alder Lake changes up the big cores cache quite considerably. First off, the L1D remains identical – so not much to report there.

On the L2 side of things, compared to Rocket Lake’s Willow Cove cores, Alder Lake’s Golden Cove cores considerably increase the L2 cache from 512KB to 1.25MB. This does come at a 15% latency degradation for this cache, however given the 2.5x increase in size and thus higher hit rates, it’s a good compromise to make.

The Gracemont E-cores have a large 2MB L2 which is shared amongst the 4 cores in a cluster, so things do look quite differently in terms of hierarchy. Here latencies after 192KB do increase for some patterns as it exceeds the 48-page L1 TLB of the cores. Same thing happens at 8MB as the 1024-page L2 TLB is exceeded.

The L3 cache of the chip increases vastly from 16MB in RKL to 30MB in ADL. This increase also does come with a latency increase – at equal test depth, up from 11.59ns to 14.24ns. Intel’s ring and cache slice approach remains considerably slower than AMD’s CCX, which at a similar L3 size of 32MB comes in at 10.34ns for equivalent random-access patterns.

On the DRAM side of things, we can start off with the RKL DDR4 to ADL DDR4 results. The memory latency at 160MB goes up from 85ns to 90ns – generally expected given the larger memory subsystem of the new chip.

Shifting over from DDR4 to the DDR5 results on Alder Lake, at JEDEC speeds, comparing DDR4-3200 CL20 to DDR4-4800 CL40, the officially supported speeds of the chip, we see memory latency only go up to 92.8ns, which is actually below our expectations. In other prefetcher-friendly patterns, latency goes up by a larger 5ns, but still that’s all within reasonable figures, and means that DDR5 latency regressions we feared are overblown, and the chip is able to take advantage of the new memory type without any larger issues.

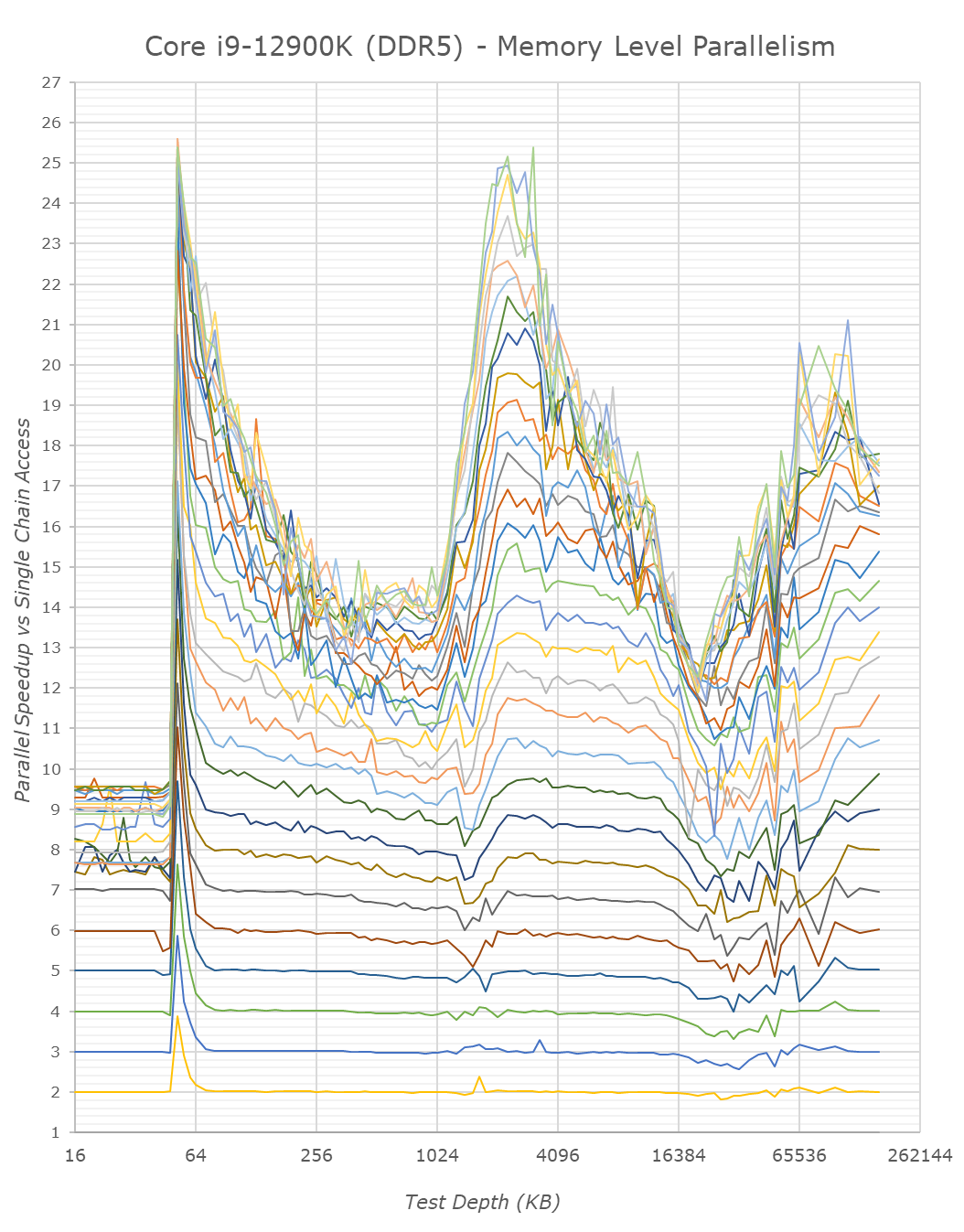

We only ever whip out our memory level parallelism test when there’s a brand-new microarchitecture which changes things quite considerably in regards to how it handles MLP. Alder Lake and its Golden Cove and Gracemont cores are such designs.

Memory level parallelism is the characteristic of a CPU being able to have multiple pending memory accesses – instead of doing things serially, out of order CPUs are able to fetch data from multiple memory locations at the same time. The definition of how many accesses this ends up as, depends on the design within the core, such as MHSR’s, but also the actual parallelism of the various caches as well as the fabric itself. Our test here compares the relative speedup of doing parallel access of random pointer chain chasing – a speedup of 2x means that the core is able to access two chains simultaneously with no degradation of per-element access times. At some point, we’ll be hitting bottlenecks of the various memory elements of the core and memory subsystem. A higher MLP speedup allows for faster execution in workloads which have data-level parallelism, and also improves the ability to hide latency in terms of performance.

Intel’s Golden Cove core is here a massive uplift in terms of its MLP capabilities. The L2 cache of the chip, because it’s so much larger, likely also has a lot more physical banks to it, likely allowing more parallel accesses.

On the L3 cache, Intel also notably mentioned that the new design is able to handle more outstanding transfers, as we immediately see this in the results of Golden Cove. Our test here only tracked up to 30 parallel accesses and we didn’t have time to check out a more extended test, but it does seem the core would be able to hit higher figures – at least until it hits TLB limits, where things slow down. The MLP capabilities here are similar, if not greater, than what AMD showcases in their Zen CPUs, something we had noted as being a strength of their microarchitecture.

MLP at deeper DRAM regions is essentially double that of Rocket Lake – at least on the DDR5 variant of Alder Lake. The DDR4 results reduce the MLP advantage, likely because the chip has to deal with only 2 memory channels rather than 4 on the DDR5 test, this allows the DDR5 variant more parallel sparse accesses to DRAM banks. Interestingly, Intel still doesn’t do as well as AMD even with DDR5 – I’m not sure where exactly the differences stem from, but it must be further down the fabric and memory controller side of things.

From the E-core Gracemont cores, the results also look good, albeit the L3 parallelism looks lower – maybe that’s a limit of the outstanding requests from the L2 cluster of the GRM cores – or maybe some interface limitation.

I think the MLP improvements of Alder Lake here are extremely massive, and represent a major jump in terms of memory performance of the design, something which undoubtedly lead to larger IPC gains for the new microarchitecture.

474 Comments

View All Comments

ajollylife - Sunday, November 7, 2021 - link

I agree. I've got a 3995wx everything on qvl, even with an optane drive. Got too annoyed with the bugs and found a 5950x worked better for a high performance desktop. Going to swap to a 12900k once i can find parts.TheJian - Sunday, November 7, 2021 - link

If you know how to use mem timings, you idiots that depend on SPD's wouldn't have these problems (that covers about 90% of this crap, and knowing other bios settings solves almost anything else besides REAL failures). I've been building systems for decades (and owned a PC biz for 8yrs myself) and a MB's QVL list was barely used by anyone I know (perhaps to look up some ODD part but otherwise...Just not enough covered at launch etc). If I waited for my fav stuff to be included in each list I'd never build. Just buy top parts and you don't worry much about this crap.That said, if my job was on the line, I'd check the list, but not because I was worried about ever being wrong...LOL. I just don't have a liars face. I'd be laughing about how stupid I think it is after so many builds and seeing so many "incompatible memory" fixed in seconds in the hands of someone not afraid to disable the SPD and get to work (or hook up with a strap before blowing gigs of modules, nics repeatedly etc). Even mixing modules means nothing then (again, maybe if I was pitching servers...DUH....1 error can be millions) after just trying to make issues exists with mixing/matching but with timings CORRECT. No, they will work, if set correct barring some REAL electrical issue (like a PSU model from brand X frying a particular model mboard - say dozens in a weekend, a few myself!).

Too many DIY people out that that really have no business building a PC. No idea what ESD is (no just because it took a hit and still works doesn't mean it isn't damaged), A+ what?? Training? Pfft, it's just some screws and slots...Whatever...Said the guy with machine after machine that have never quite worked right...LOL. If you live in SF or some wet joint OK (leo leporte etc? still around), otherwise, just buy a dell/hp and call it a day. They exist because most of you are incapable of doing the job correctly, or god forbid troubleshooting ANYTHING that doesn't just WORK OOB.

Qasar - Sunday, November 7, 2021 - link

blah blah blah blah blahMidland_Dog - Saturday, November 27, 2021 - link

people like you cost amd salessilly amdumb

cyberpunx_r_ded - Friday, November 5, 2021 - link

sounds like a Mobo problem, not a CPU problem....for someone who has put together "hundreds of systems" you should know that by the symptoms.That motherboard is known to be dog sh1t btw.

DominionSeraph - Saturday, November 6, 2021 - link

Note Intel doesn't allow "dog sh1t motherboards" to happen, especially at the $300+ price point. That makes it an AMD issue.I can refurb Dell after Dell after Dell after Dell, all of them on low-end chipsets and still on the release BIOS, and they all work fabulously.

Meanwhile two years into x570 and AMD is still working on getting USB working right.

I think I'll put this thing on the market and see if I can recoup the better part of an i9 12900k build. I may have to drop down to one of the i7 6700's or the i7 4770k system I have until they're in stock, but that's really no issue.

Netmsm - Saturday, November 6, 2021 - link

It's a pleasure to not have p*gheaded amateurs in the AMD zone.Others are telling you it's not AMD issue but you spamming it's AMD, AMD, AMD... having got the wrong and of the stick.

Wrs - Saturday, November 6, 2021 - link

@Netmsm Regardless of whether the blame lies with ASRock for the above issue, it remains a fact that AMD didn't fix a USB connectivity problem in Zen 3 until 6-7 months after initial availability. Partly that was because the installed base of guinea pigs was constricted by limited product, but it goes to show that quick and widespread product rollouts have a better chance of ironing out the kinks. (Source if you've been under a rock heh https://www.anandtech.com/show/16554/amd-set-to-ro...And then recently we had Windows 11 performance regressions with Zen 3 cache and sandboxed security. These user experience hiccups suggest one company perceptibly lags the other in platform support. It's just something I've noticed switching between Intel and AMD. I might think this all to be normal were I loyal to one platform.

Netmsm - Sunday, November 7, 2021 - link

I didn't realize we're here to discuss minor issues/incompatibilities of the Intel's rival. I thought we're here to talk about major inefficiencies besides improvements of Intel's new architecture. Sorry!Wrs - Sunday, November 7, 2021 - link

@Netmsm That's no minor issue/incompatibility. Maybe for you, but a USB dropout is not trivial! Think missing keystrokes, stuttering audio for USB headsets and capture cards. It didn't affect every user, and was intermittent, which was part of the difficulty. I put off a Ryzen 5000 purchase for 2 months waiting for them to fix it. (I also put it off for 4 months before that because of lack of stock lol.)