Intel Architecture Day 2021: Alder Lake, Golden Cove, and Gracemont Detailed

by Dr. Ian Cutress & Andrei Frumusanu on August 19, 2021 9:00 AM ESTConclusions

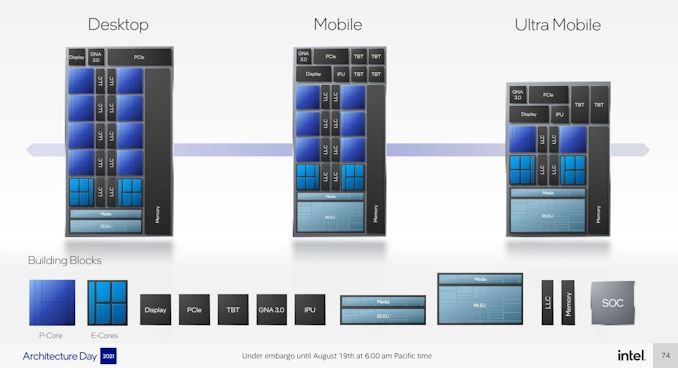

Alder Lake is set to come to market for both desktop and mobile, and we’re expecting the desktop hardware to start to appear by the end of the year – perhaps a little later for the rest of the family, but all-in-all we expect Intel is experiencing some serious squeaky bum time regarding how all the pieces will fit in place at that launch. The two main critical factors are operating systems and memory.

Because Alder Lake is Intel’s first full-stack attempt to commercialize a hybrid design, it has had to work closely with Microsoft to enable all the features it needs to make managing a hybrid core design properly beneficial to users. Intel’s new Thread Director Technology couples an integrated microcontroller per P-core and a new API for Windows 11 such that the scheduler in the operating system can take hints about the workflow on the core at a super fine granularity – every 30 microseconds or so. With information about what each thread is doing (from heavy AVX2 down to spin lock idling), the OS can react when a new thread needs performance, and choose which threads need to be relegated down to the E-core or as a hyperthread (which is classified as slower than an E-core).

When I first learned Alder Lake was going to be a hybrid design, I was perhaps one of the most skeptical users about how it was going to work, especially with some of the limits of Windows 10. At this point today however, with the explanations I have from Intel, I’m more confident than not that they’ve done it right. Some side off-the-record conversations I have had have only bolstered the idea that Microsoft has done everything Intel has asked, and users will need Windows 11 to get that benefit. Windows 10 still has some Hardware Guided Scheduling, but it’s akin to only knowing half the story. The only question is whether Windows 11 will be fully ready by the time Alder Lake comes to market.

For memory, as a core design, Alder Lake will have support for DDR4 and DDR5, however only one can be used at any given time. Systems will have to be designed for one or the other – Intel will state that by offering both, OEMs will have the opportunity to use the right memory at the right time for the right cost, however the push to full DDR5 would simplify the platform a lot more. We’re starting to see DDR5 come to the consumer market, but not in any volume that makes any consumer sense – market research firms expect the market to be 10% DDR5 by the end of 2022, which means that consumers might have to be stay with DDR4 for a while, and vendors will have to choose whether to bundle DDR5 with their systems. Either way, there’s no easy answer to the question ‘what memory should I use with Alder Lake’.

Through The Cores and The Atoms

From a design perspective, both the P-core and E-core are showcasing substantial improvements to their designs compared to previous generations.

The new Golden Cove core has upgraded the front-end decoder, which has been a sticking point for analysis of previous Cove and Lake cores. The exact details of how they operate are still being kept under wraps, but having a 6-wide variable length decoder is going to be an interesting talking point against 8-wide fixed-length decoders in the market and which one is better. The Golden Cove core also has very solid IPC figure gains, Intel saying 19%, although the fact there are some regressions is interesting. Intel did compare Golden Cove to Cypress Cove, the backported desktop core, rather than Willow Cove, the Tiger Lake core, which would have been a more apt comparison given that our testing shows Willow Cove slightly ahead. But still, around 19% is a good figure. Andrei highlights in his analysis that the move from a 10-wide to a 12-wide disaggregated execution back-end should be a good part of that performance, and that most core designs that go down this route end up being good.

However, for Gracemont, Intel has taken that concept to the extreme. Having 17 execution ports allows Intel to clock-gate each port when not in use, and even when you couple that with a smaller 5-wide allocation dispatch and 8-wide retire, it means that without specific code to keep all 17 ports fed, a good number are likely to be disabled, saving power. The performance numbers Intel provided were somewhat insane for Gracemont, suggesting +8% performance over Skylake at peak power, or a variety of 40% ST perf/power or 80% MT perf/power against Skylake. If Gracemont is truly a Skylake-beating architecture, then where have you been! I’m advocating for a 64-core HEDT chip tomorrow.

One harsh criticism Intel is going to get back is dropping AVX-512 for this generation. For the talk we had about ‘no transistor left behind’, Alder Lake dropped it hard. That’s nothing to say if the functionality will come back later, but if rumors are believed and Zen 4 has some AVX-512 support, we might be in a situation where the only latest consumer hardware on the market supporting AVX-512 is from AMD. That would be a turn-up. But AMD’s support is just a rumor, and really if Intel wants to push AVX-512 again, it will have a Sisyphean task to convince everyone it’s what the industry needs.

Where We Go From Here

There are still some unanswered questions as to the Alder Lake design, and stuff that we will test when we get the hardware in hand. Intel has an event planned for the end of October called the Intel InnovatiON event (part of the ON series), which would be the right time to introduce Alder Lake as a product to the world. Exactly when it comes to retail will be a different question, but as long as Intel executes this year on the technology, it should make for an interesting competition with the rest of the market.

223 Comments

View All Comments

abufrejoval - Saturday, August 21, 2021 - link

Since AVX-512 isn't new, I'm somewhat doubtful on the bug theory.And since Intel doesn't do chiplets yet, they can't be reusing that silicon for server CPUs either.

It really has me think that the AVX-512 guys tried to push their baby through into production until the bloody final battle, when the E/P-Core symmetry team shut them down (for now, it's all fuses, right?).

It's really very much a matter of how you want to use these resources and educating both operating systems and users about their potential and limitations. If all you see in E-cores is a way to run a P-core task on less energy budget, that symmetry is critical. If you see E-cores as an add-on resource that somewhat functionally limited (but might have better side-channel resilience or run special purpose VMs etc.), yet available for low silicon real-estate, it's another story.

On notebooks on batteries, the symmetric view wins out. For anything on a powerline, the E-cores may make some sense as functionally constrained extra resources, I can't see the power savings vs. good idle there (well, perhaps a single E-core, like the Tegra 3 had against it's quad P-cores).

It's very hard to maintain real flexibility when things get baked into silicon.

I'd say product managers got the better over the engineers and what you get is a compromise, which hardly ever ideal nor easy to understand without the context of its creation.

mode_13h - Sunday, August 22, 2021 - link

> It really has me think that the AVX-512 guys tried to push their baby through into> production until the bloody final battle,

That doesn't explain the backport of VNNI to AVX2, unless that was already being done for other reasons.

Intel went through this once, already, with Lakefield. That was like 2 years ago, and forced the same situation of the P-core being kneecapped. So, this thing can't have been a surprise.

Now, wouldn't it be cool if BIOS gave you a choice between enabling the E-cores and having AVX-512 on the P-cores? I know it'd create more headaches for the customer support teams at Intel and many OEMs, but that would at least be a more customer-centric way to make the tradeoff.

Spunjji - Tuesday, August 24, 2021 - link

Giving customers more choice for no additional cost is not the Intel way!Oxford Guy - Thursday, August 26, 2021 - link

Some here fervently believe enthusiasts who build their own PCs aren’t going to enter BIOS to turn on XMP...Spunjji - Friday, August 27, 2021 - link

@Oxford Guy - only ever seen people argue the majority of users won't do that, not enthusiasts specifically.SystemsBuilder - Friday, August 20, 2021 - link

Breaking out VNNI from AVX512 and keeping it in Alder Lake is to accelerate Neural Net inference. Many other parts of AVX512 (i.e. AVX512F etc) are necessary to sufficiently accelerate NN learning.Intel probably thought that Alder Lake CPUs would only be used in inference scenarios and therefor reserved AVX512 and AMX to Sapphire rapids server, workstation and hopefully the HEDT platform road maps.

Intel forgot (or more likely did not care) that companies have, after 5 years of AVX512 with implementations as far down into the consumer stack as Ice Lake and Tiger Lake lap tops, tuned libraries to take advantage of AVX512 in OTHER scenarios than deep learning. Those libraries are now going to be regressing to AVX2 when run on Alder lake CPUs, effectively knee capped, executed on P and crap cores, ops sorry, meant E cores.

mode_13h - Saturday, August 21, 2021 - link

To be fair, I think Intel had further motives for porting VNNI to AVX2. They sell Atom processors into applications where inferencing is a useful capability. Skylake CPUs are already pretty good at inferencing, with just baseline AVX2, so VNNI can only help.Still, the situation is something of an own-goal. I'll bet Intel will be nursing that wound for the next few years. I don't expect they'll make the same decision/mistake in Raptor Lake.

StoykovK - Friday, August 20, 2021 - link

Intel stated that ADL has 6 decoders from 4, but didn't Skylake has 5 (4 simple + 1 complex)?I'm a little bit confused. It looks like, from architecture point, Golden Cove compared to WillowCove is bigger update, than WillowCove to SkyLake, but both result ~20% IPC.

E-cores: Really good idea to get high score in multi-core benchmarks. GoldenCove looks like ~33% faster than E-cores, but taking a lot more power. Does anybody have an idea how wide is E-cores AVX- 128bit or 256bit.

TristanSDX - Friday, August 20, 2021 - link

SSE - 128 bit, AVX - 256 bit, AVX-512 - 512 bitStoykovK - Friday, August 20, 2021 - link

Zen/Zen+, Sandy Bridge, Ivy Bridge fuses 2x128bit units in order to execute single 256bit AVX.