Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

by Dr. Ian Cutress on July 30, 2019 9:30 AM EST- Posted in

- CPUs

- Intel

- 10nm

- Microarchitecture

- Ice Lake

- Project Athena

- Sunny Cove

- Gen11

Wi-Fi 6: Implementing AX over AC*

In consumer products, Intel has been placing its new Wi-Fi initiative into every chipset it can find. We’ve seen CNVi-enabled solutions occur on the desktop and in the notebook space for almost two years now, with the goal to make high-performance and low-power Wi-Fi ubiquitous, and to push Intel’s wireless solutions everywhere. Ice Lake is where Intel enables Wi-Fi 6 in such a solution.

If you’ve never come across the term CNVi before, it is Intel’s proprietary interface link and controller which connects the logic parts of the wireless connection on the chipset to the antenna and radio frequency analog parts which are found on a different module. This allows Intel’s partners to use different antenna ‘RF’ modules depending on what it wants to support, such as single antenna designs, dual antenna designs, or higher bandwidth modes.

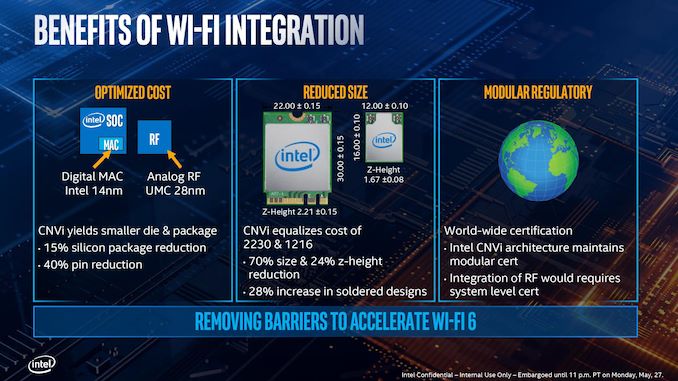

Because CNVi is a proprietary interface, Intel has no plans to license it, and therefore the only RF modules you can buy to support it come from Intel. Intel states that its CNVi solution enables the high frequency digital logic to be built on its 14nm process with the chipset, and the RF analog side can be built on 28nm UMC which is better for analog signals and performance than any of Intel’s currently available manufacturing processes. Overall Intel states that using an external RF chip in this fashion affords a 15% silicon package reduction and a 40% pin reduction.

CNVi RF modules can either be an M.2 module (2230 = 22mm x 30mm) or as a soldered module (1216), which respectively allows for modularity, or for decreasing z-height for thin and light designs. Intel also states that this method of supplying the Wi-Fi, as separate digital and analog silicon, allows Wi-Fi certification to be done at the module level, rather than at the system level, simplifying the process for its partners.

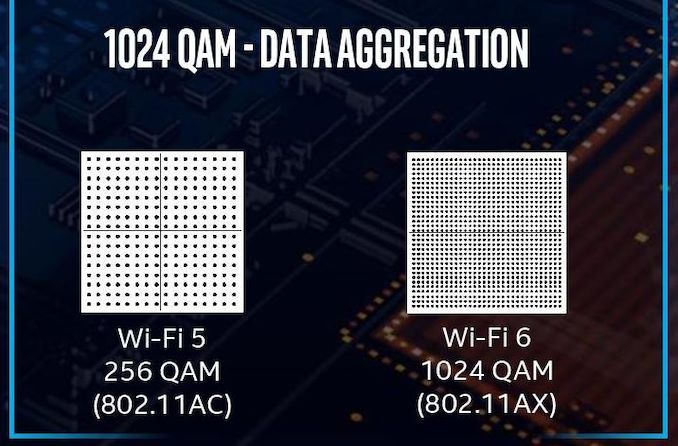

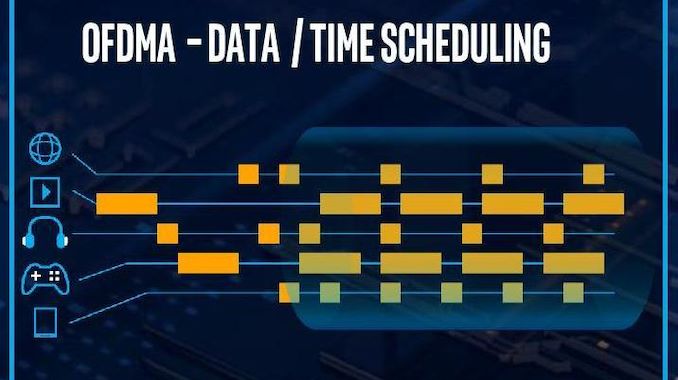

As an overarching technology, Wi-Fi 6 promises better bandwidth than standard Wi-Fi 5, as well as support for more devices on the same network. Technically this increased bandwidth comes down to data/time aggregation through the air as a benefit of OFDMA support, as well as 1024-QAM signaling design rather than 256-QAM signaling for increased throughput.

Wi-Fi 6 also has a lot of additional optional elements to the standard, which Intel believes will cause a good deal of confusion in the market. Naturally, Intel suggests that its partners that use a CNVi Wi-Fi 6 implementation also promote Wi-Fi 6 access points built on Intel’s platforms for simpler integration.

At this point in time, there are two main Wi-Fi 6 controllers: Intel’s AX200/AX201 2x2 CNVi module which uses the on-die enhancements, and Rivet Network’s AX1650 M.2 module which doesn’t use any of the on-die enhancements as it connects through a PCIe lane on the chipset. Technically both are built with the same silicon, as the companies are working together on the design, however Rivet is implementing its own acceleration techniques due to engines inside the hardware.

*The asterisk in the title of this page is because you still need external hardware in order to enable it, and to do it in the best way requires Intel-only hardware. You can use other vendor hardware, but you don’t need something special on the SoC to enable that.

107 Comments

View All Comments

The_Assimilator - Wednesday, July 31, 2019 - link

Getting Thunderbolt on-die is huge for adoption. While I doubt many laptop manufacturers will enable more than a single TB port, desktop is an entirely different kettle of fish.umano - Wednesday, July 31, 2019 - link

I am afraid but I cannot consider 4 cores cpu as premiumKhenglish - Wednesday, July 31, 2019 - link

This honestly is looking like the worst architecture refresh since Prescott. IPC increases are getting almost completely washed out by loss in frequency. I wonder if this would have happened if Ice Lake came out on 14nm. Is the clock loss from uArch changes, process change, or a mix of both?Performance of an individual transistor has been decreasing since 45nm, but overall circuit performance kept improving due to interconnect capacitance decreasing at a faster rate at every node change. It looks like at Intel 10nm, and TSMC 7nm that this is no longer true, with transistor performance dropping off a cliff faster than interconnect capacitance reduction. 5nm and 3nm should be possible, but will anyone want to use them?

Sivar - Wednesday, July 31, 2019 - link

"...with a turbo frequency up to 4.1 GHz"This is the highest number I have come across for the new 10th generation processors, and according to SemiAccurate (which is accurate more often than not), this is likely not an error.

If this value is close to desktop CPU limitations, the low clock speed all but erases the 18% IPC advantage -- an estimate likely based on a first-gen Skylake.

Granted, the wattage values are low, so higher-wattage units should run at least a bit faster.

Farfolomew - Wednesday, July 31, 2019 - link

I’m a bit confused by the naming scheme. Ian, you say: “The only way to distinguish between the two is that Ice Lake has a G in the SKU and Comet Lake has a U”But that’s not what’s posted in several places throughout the article. The ICL processors are named Core iX-nnnnGn where CML are Core iX-nnnnnU. Comet lake is using 5 digits and Ice Lake only 4 (1000 vs 10000 series).

Is this a typo or will ICL be 1000-series Core chips?

name99 - Wednesday, July 31, 2019 - link

Regarding AI on the desktop. The place where desktop AI will shine is NLP. NLP has lagged behind vision for a while, but has acquired new potency with The Transformer. It will take time for this to be productized, but we should ultimately see vastly superior translation (text and speech), spelling and grammar correction, decent sentiment analysis while typing, even better search.Of course this requires productization. Google’s agenda is to do this in the cloud. MS’ agenda I have no idea (they still have sub-optimal desktop search). So probably Apple will be first to turn this into mainstream products.

Relevant to this article is that I don’t know the extent to which instructions and micro-architectures optimized for CNNs are still great for The Transformer (and the even newer and rather superior Transformer-XL published just a few months ago). This may all be a long time happening on the desktop if INTC optimized too much purely for vision, and it takes another of their 7 years to turnaround and update direction...

croc - Thursday, August 1, 2019 - link

It seems that Ice Lake / Sunny Cove will have hardware fixes for Spectre and Meltdown. I would like to see some more information on this, such as how much speed gain, whether the patch is predictive (so as to block ALL such OOE / BP exploits) etc.MDD1963 - Thursday, August 1, 2019 - link

A month or so ago, we heard a few rumors that the CPUs were ahead ~18% in IPC (I see that number again in this article), but are down ~20+% in clock speed.... ; it would be nice to see at least one or two performance metrics/comparisons on a shipped product. :)isthisavailable - Thursday, August 1, 2019 - link

Unlike Ryzen mobile, intel’s “upto” 64 EUs part will probably only ship in like 2 laptops. Therefore amd has more designs in my book. I don’t understand people who buy expensive 4K laptops with intel integrated gfx which can’t even render windows 10 ui smoothly.Looking forward to Zen2 + navi based 7nm APU.

Bulat Ziganshin - Thursday, August 1, 2019 - link

> it can be very effective: a dual core system with AVX-512 outscored a 16-core system running AVX2 (AVX-256).it's obviously wrong - since ice lake has only one avx-512 block but two avx2 blocks, it's not much faster in avx-512 mode compared to avx2 mode

the only mention of HEDT cpus at the page linked is "At a score of 4519, it beats a full 18-core Core i9-7980XE processor running in non-AVX mode". Since AVX-512 can process 16 32-bit numbers in a single operation, no wonder that a single avx-512 core matches 16 scalar cores