Intel's Xeon Cascade Lake vs. NVIDIA Turing: An Analysis in AI

by Johan De Gelas on July 29, 2019 8:30 AM ESTWho Will Win the Next Enterprise Market?

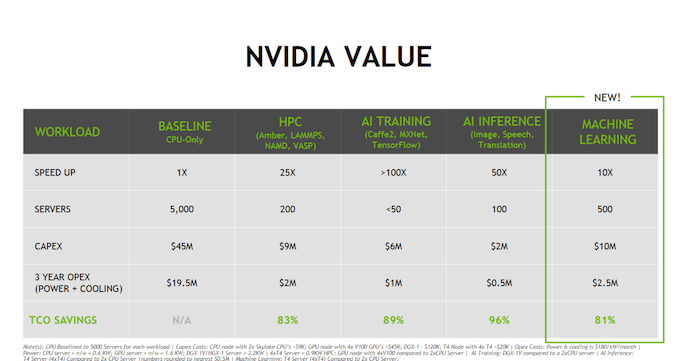

At their last investors day, one of NVIDIA’s slides made it clear what the next battle in the enterprise space will be all about: data analytics. Note how an expensive dual Xeon “Skylake” Scalable is considered as baseline. That is quite a statement; reducing one of the latest Intel powered systems to a completely outperformed humble baseline.

NVIDIA’s entire business model revolves around the theory that buying expensive hardware like DGXs and Teslas is good for your TCO (“the more you buy, the more you save”). Don’t buy 5000 servers, buy 50 DGXes. Despite the fact that a DGX consumes 5 times more power, and costs $120k instead of $9k, you will be much better off. Of course, this is marketing at its best – or at its worst, depending on how you look at it. But even if the numbers are slightly exaggerated, it is a strong message: “from our deep learning stronghold to the Intel’s current growth market (Inference, HPC and machine learning), we will beat Intel by a large margin”.

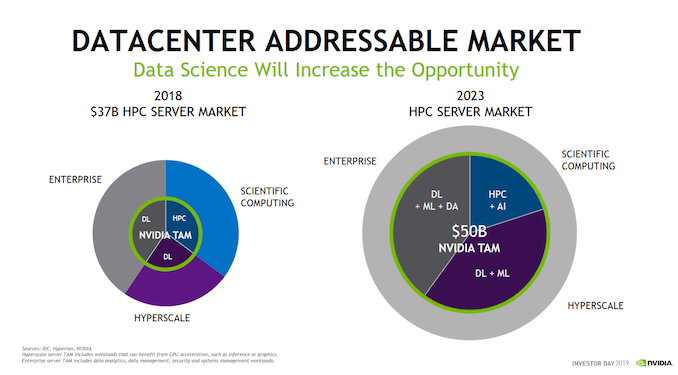

Not convinced? This is how NVIDIA and IDC see the market evolving.

Currently the compute intensive or high-performance sub-market is about $37 billion out of a total $100 billion market. NVIDIA believes that this sub-market will double by 2023 and that they will be able to address $50 billion. In other words, the data analytics market – in a broad sense – will be almost half of the complete server market.

Even if this is an overestimation, it is clear that times are changing, and the stakes are very high. Neural networks are much better suited to GPUs, but if Intel can make sure that most of data pipeline runs better on CPUs and you only need a GPU for the most intensive and scalable neural networks, it will push NVIDIA back to a more niche role. On the other hand, if NVIDIA can accelerate a much larger part of the data pipeline, it will conquer markets that mostly belong to Intel and expand rapidly. And in the midst of this heated battle, IBM and AMD must make sure they get their share of the market. IBM will be offering better NVIDIA GPU based servers, and AMD will try building the right software ecosystem.

56 Comments

View All Comments

C-4 - Monday, July 29, 2019 - link

It's interesting that optimizations did so much for the Intel processors (but relatively less for the AMD ones). Who made these optimizations? How much time was devoted to doing this? How close are the algorithms to being "fully optimized" for the AMD and nVidia chips?quorm - Monday, July 29, 2019 - link

I believe these optimizations largely take advantage of AVX512, and are therefore intel specific, as amd processors do not incorporate this feature.RSAUser - Monday, July 29, 2019 - link

As quorm said, I'd assume it's due to AVX512 optimizations, the next generation of AMD Epyc CPU's should support it, and I am hoping closer to 3GHz clock speeds on the 64 core chips, since it seems the new ceiling is around the 4GHz mark for 16 all-core.It will be an interesting Q3/Q4 for Intel in the server market this year.

SarahKerrigan - Monday, July 29, 2019 - link

Next generation? You mean Rome? Zen2 doesn't have any AVX512.HStewart - Tuesday, July 30, 2019 - link

I believe AMD AVX 2 is dual-128 bit instead of 256bit - so AVX 512 would probably be quad 128bit .jospoortvliet - Tuesday, July 30, 2019 - link

That’s not really how it works, in the sense that you explicitly need to support the new instructions... and amd doesn’t (plan to, as far as we know).Qasar - Tuesday, July 30, 2019 - link

from wikipedia :" AVX2 is now fully supported, with an increase in execution unit width from 128-bit to 256-bit. "

" AMD has increased the execution unit width from 128-bit to 256-bit, allowing for single-cycle AVX2 calculations, rather than cracking the calculation into two instructions and two cycles."

which is from here : https://www.anandtech.com/show/14525/amd-zen-2-mic...

looks like AVX2 is single 256 bit :-)

name99 - Monday, July 29, 2019 - link

Regarding the limits of large batches: while this is true in principle, the maximum size of those batches can be very large, is hard to predict (at leas right now) and there is on-going work to increase the sizes, This link describes some of the issue and what’s known:http://ai.googleblog.com/2019/03/measuring-limits-...

I think Intel would be foolish to pin many hopes on the assumption that batch scaling will soon end the superior performance of GPUs and even more specialized hardware...

brunohassuna - Monday, July 29, 2019 - link

Some information about energy consumption would very useful in comparisons like thatozzuneoj86 - Monday, July 29, 2019 - link

My first thought when clicking this article was how much more visibly-complex CPUs have gotten in the past ~35 years.Compare the bottom of that Xeon to the bottom of a CLCC package 286:

https://en.wikipedia.org/wiki/Intel_80286#/media/F...

And that doesn't even touch the difference internally... 134,000 transistors to 8 million and from 16Mhz to 4,000Mhz. The mind boggles.