Intel's 10nm Cannon Lake and Core i3-8121U Deep Dive Review

by Ian Cutress on January 25, 2019 10:30 AM ESTStock CPU Performance: Legacy Tests

We have also included our legacy benchmarks in this section, representing a stack of older code for popular benchmarks.

All of our benchmark results can also be found in our benchmark engine, Bench.

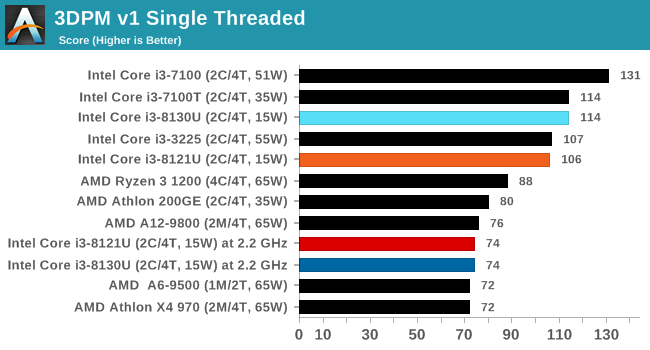

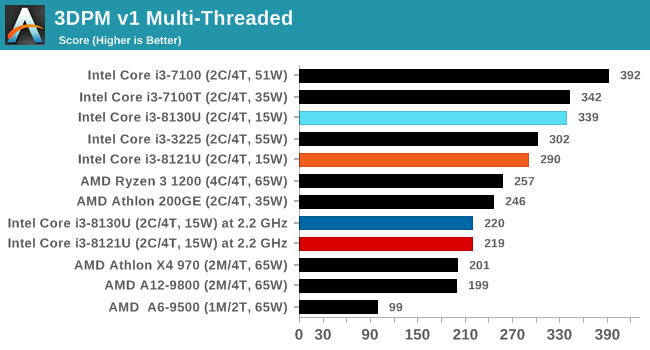

3DPM v1: Naïve Code Variant of 3DPM v2.1

The first legacy test in the suite is the first version of our 3DPM benchmark. This is the ultimate naïve version of the code, as if it was written by scientist with no knowledge of how computer hardware, compilers, or optimization works (which in fact, it was at the start). This represents a large body of scientific simulation out in the wild, where getting the answer is more important than it being fast (getting a result in 4 days is acceptable if it’s correct, rather than sending someone away for a year to learn to code and getting the result in 5 minutes).

In this version, the only real optimization was in the compiler flags (-O2, -fp:fast), compiling it in release mode, and enabling OpenMP in the main compute loops. The loops were not configured for function size, and one of the key slowdowns is false sharing in the cache. It also has long dependency chains based on the random number generation, which leads to relatively poor performance on specific compute microarchitectures.

3DPM v1 can be downloaded with our 3DPM v2 code here: 3DPMv2.1.rar (13.0 MB)

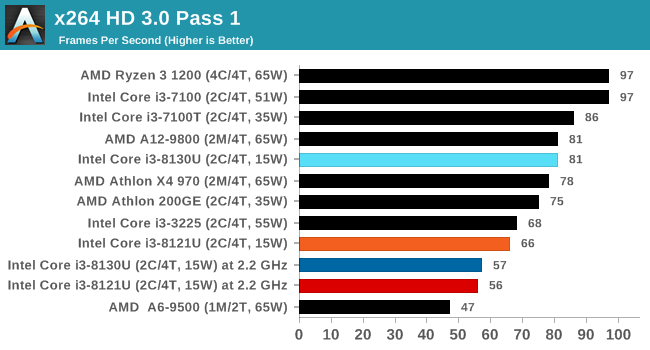

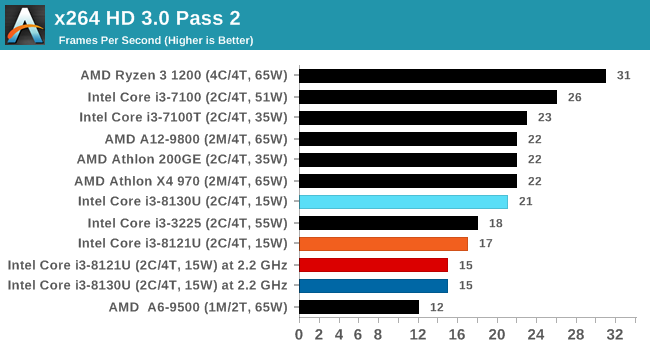

x264 HD 3.0: Older Transcode Test

This transcoding test is super old, and was used by Anand back in the day of Pentium 4 and Athlon II processors. Here a standardized 720p video is transcoded with a two-pass conversion, with the benchmark showing the frames-per-second of each pass. This benchmark is single-threaded, and between some micro-architectures we seem to actually hit an instructions-per-clock wall.

129 Comments

View All Comments

just4U - Saturday, January 26, 2019 - link

I don't recall AMD ever being in that position before. Even with the Athlon they were outmanned in all areas except for performance. Unfair business practices by Intel and a inability to keep up with demand on the manufacturing side took away any lead AMD had at the time. On top of that they were never competing price wise. Amd chips were sold for a fair amount less. I only recall one cpu being priced similar to Intel's top dog and it was dropped down to 30% less a few months later.edzieba - Friday, January 25, 2019 - link

"CLWB attempts to minimize the compulsory cache miss if the same data is accessed temporally after the line is flushed if the same data is accessed temporally after the line is flushed. "Probably unintentional, but appropriate!

Spunjji - Tuesday, January 29, 2019 - link

I liked that one, tooiwod - Friday, January 25, 2019 - link

Just two things.1. The Article should have been split into at least two parts, separating each by at least 3 to 7 days. First parts being Intel 10nm, 2nd Part being Cannon Lake and how it perform.

2. Basically Cannonlake sucks. Lets hope Icelake will not disappoint.

nevcairiel - Saturday, January 26, 2019 - link

This incarnation of 10nm is only ever going to be seen in this particular chip, so its really quite closely related. The production-grade 10nm we're getting end 2019 is already going to be one step up from that.iwod - Saturday, January 26, 2019 - link

Yes but the article is way too long for a single read.saylick - Friday, January 25, 2019 - link

Wow, this is why I visit Anandtech; the deep dives are truly deep dives, unlike how some other "tech blog" sites pawn off articles as "deep dives" when all they do is regurgitate information off of official technical slides. Kudos Ian!austinsguitar - Friday, January 25, 2019 - link

i bet amd has them shaking in their boots...PeachNCream - Friday, January 25, 2019 - link

"The CPU area is instead attached at three points, and there is an additional pad to stop the chassis from rubbing against the heatpipe. This means that the chip height combined with the PCB and the heatsink is enough to start to worry how the chassis brushes up against the internals? Interesting."This isn't an uncommon practice. Laptop bottom panels can flex so the placement of pads is quite typical. Even my old Core2 Dell Latitude e6400 has pads on the heat pipe.

KOneJ - Sunday, January 27, 2019 - link

Excellent point. I think I remember this on an old Toshiba C55D E-1200 APU and a Dell Latitude D610 based on a Dothan Pentium M.