AMD Reveals Threadripper 2 : Up to 32 Cores, 250W, X399 Refresh

by Ian Cutress on June 5, 2018 11:05 PM EST

One of the surprises from AMD’s first year of the newest x86 Zen architecture was the launch of the Threadripper platform. Despite the mainstream Ryzen processors already taking a devastating stab into the high-end desktop market, AMD’s Threadripper offered more cores at a workstation-friendly price. For 2018, the next generation is going to be using AMD’s updated 12nm Zeppelin dies, as well as including a few new tweaks into the system including better boost and faster caches.

This article is still a work in progress, and will be updated as more news comes in.

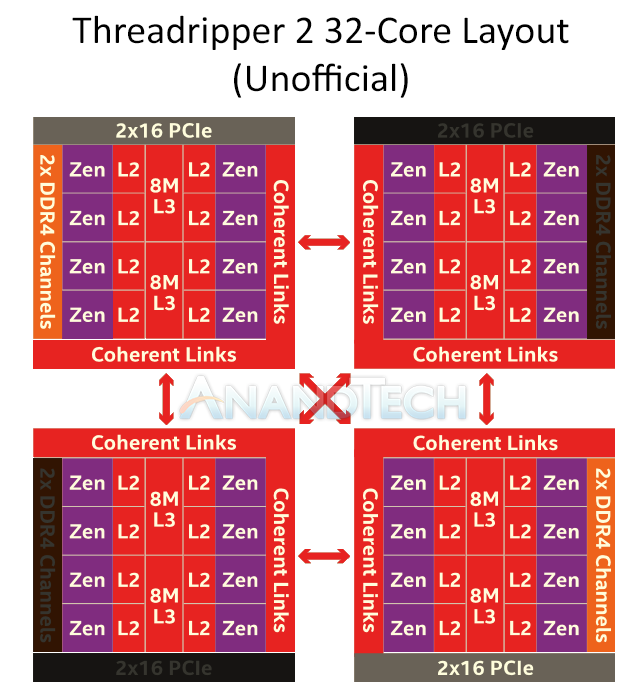

AMD’s Zeppelin silicon has 8 cores, and the first generation Threadripper uses two of them to get to the top-SKU of 16-cores. Inside the CPU however, there are four pieces of silicon: two active and two inactive. For this second generation of Threadripper, called Threadripper 2 or the Threadripper 2000-series, AMD is going to make these inactive dies into active ones, and substantially increase the core count for the high-end desktop and workstation user.

At the AMD press event at Computex, it was revealed that these new processors would have up to 32 cores in total, mirroring the 32-core versions of EPYC. On EPYC, those processors have four active dies, with eight active cores on each die (four for each CCX). On EPYC however, there are eight memory channels, and AMD’s X399 platform only has support for four channels. For the first generation this meant that each of the two active die would have two memory channels attached – in the second generation Threadripper this is still the case: the two now ‘active’ parts of the chip do not have direct memory access.

This technically adds latency to the platform, however AMD is of the impression that for all but the most memory bound tasks, this should not be an issue (usually it is suggested to just go buy an EPYC for those workloads). While it does put more pressure on the internal Infinity Fabric, AMD ultimately designed Infinity Fabric for scalable scenarios like this between different silicon with different levels of cache and memory access.

Update: AMD has just published a full copy of their slide deck for the Threadripper 2 presentation. In it are a few interesting factoids.

| AMD Threadripper CPUs | |||||

| Threadripper 2 32-Core Sample |

Threadripper 2 24-Core Sample |

Threadripper 1950X |

Threadripper 1920X |

||

| Socket | TR4 (LGA) 4094-pin |

||||

| CPU Architecture | Zen+ | Zen+ | Zen | Zen | |

| Cores/Threads | 32 / 64 | 24 / 48 | 16 / 32 | 12 / 24 | |

| Base Frequency | 3.0 GHz | 3.0 GHz | 3.4 GHz | 3.5 GHz | |

| Turbo Frequency | 3.4 GHz (WIP) | 3.4 GHz (WIP) | 4.0 GHz | 4.0 GHz | |

| L3 Cache | 64 MB ? | 48 MB ? | 32 MB | 32 MB | |

| TDP | 250W | 250W | 180W | 180W | |

| PCIe 3.0 Lanes | 60 + 4 | ||||

| Chipset Support | X399 | ||||

| Memory Channels | 4 | ||||

- Both the 24-core and 32-core sample CPUs are clocked at 3.0GHz base and 3.4GHz all-core turbo, with the latter being a work-in-progress according to the company.

- The 32-core system was equipped with DDR4-3200 memory. This is notable because the Ryzen processors based on the same 12nm Zeppelin dies officially max out at DDR4-2933.

- The codename for the processor family is listed as "Colfax". This is the first we've heard this codename from AMD.

- Despite the high TDP, both CPUs used in AMD's demos were air-cooled, using AMD's Wraith Ripper Air Cooler

Also announced at the presentation is the state of play of motherboards. According to the motherboard vendors These new Threadripper 2000-series processors will have a peak TDP rating of 250W, which is much higher than 180W we saw on the 1950X. We have been told by partners that the 250W rating is actually conservative, and users should expect lower power consumption in most scenarios. Nonetheless, it was stated by several motherboard vendors that some of the current X399 motherboards on the market might struggle with power delivery to the new parts, and so we are likely to see a motherboard refresh. That is not saying that the current X399 offerings will not work, however they might not offer overclocking to the level that users might expect. At Computex there are new X399 refresh motherboards being demonstrated by a few companies, and we will report on them in due course. Other specifications are expected to match the previous generation, such as PCIe lane counts, despite the newly active dies.

MSI's 19-phase X399 Refresh Motherboard

The launch for these new processors, according to our moles is in early August. This aligns with what AMD stated at the beginning of the year at CES, and is almost a year from the original Threadripper launch.

Pricing on the processors is set to be revealed either today or closer to the launch time. We will update this piece as more information comes in.

It will be interesting if AMD is going to go through the ‘unboxing’ embargo this time around, or just jump straight to full performance reviews. As always, come to AnandTech for the full story.

GIGABYTE's new X399 Refresh Motherboard

| Want to keep up to date with all of our Computex 2018 Coverage? | ||||||

Laptops |

Hardware |

Chips |

||||

| Follow AnandTech's breaking news here! | ||||||

203 Comments

View All Comments

Kevin G - Wednesday, June 6, 2018 - link

The Xeons E5/E7 did split the memory controller between different rings internally. This permitted the previous 18 core and 24 core chips to act as two NUMA nodes per socket.However the number of QPI links varied per ring and there was only a single PCIe root complex per die.

Ian Cutress - Tuesday, June 5, 2018 - link

It's two dies get two channels each and two other dies get zero.I love you too, btw

CajunArson - Wednesday, June 6, 2018 - link

Great, so now that AMD has abandoned on-die memory controllers in high-end parts, when can we expect your article claiming that Intel must make sure to go back to 1990's era off-chip memory controllers since they are clearly idiots who "can't keep up" with AMD?sor - Wednesday, June 6, 2018 - link

Intel already does this. Someone above pointed this out to you. You seem to be looking for a fight.CajunArson - Wednesday, June 6, 2018 - link

No, the guy above is an idiot who has never heard of a NUMA node on his life and neither have you.Claiming that an on-die ring bus (which isn't even accurate for Skylake X) is exactly the same thing as having to dump every memory request for half your CPU through and over-glorified PCIe connector is flat out wrong.

Look up what the term "NUMA node" means some time. Then realize that having four of them in a single socket (and massively unbalanced to boot) is not something to be bragging about.

.vodka - Wednesday, June 6, 2018 - link

Then we'll see if AMD has polished their interconnect enough that two dies not having direct memory access isn't a major problem for the intended workloads on this platform.Their simulations and tests must have been good enough to greenlight this. If pricing is right, it'll be good for some people. I guess there will be an option in the BIOS to just disable those two extra dies and run it like a 1st gen TR while enjoying the rest of the 2nd gen improvements which are significant.

Time will tell.

Gothmoth - Wednesday, June 6, 2018 - link

Is this Retard above allowed to insult people... 😂 He googled Numa now he think he is an expert.... Lolevernessince - Wednesday, June 6, 2018 - link

You clearly have no idea what NUMA is. It's a performance benefit to have certain cores have direct access to memory and other's not.https://en.wikipedia.org/wiki/Non-uniform_memory_a...

AMD improves memory latency and cache misses by assigning the closest cores to the closest resources.

If this was a performance issue it would have shown up in the first threadripper. Clearly it's working well as Threadripper performs just as well as Intel counterparts at half the price.

iwod - Wednesday, June 6, 2018 - link

Well most people don't. Even those who programmed low level enough don't either. or at least they understand but not too sure how best to handle it. Go and ask FreeBSD Devs.On my Desktop, I am glad I have the choice of 32 Core. Now Bring me Zen 2.

CajunArson - Wednesday, June 6, 2018 - link

Oh yeah it's such a "performance benefit" to have to rewrite your entire software stack to have to keep track of the physical location of each byte to prevent performance from going off a cliff.That's like saying that having a cast on your leg is a "performance benefit" because having a broken leg is a great thing.

The better solution is to not have to worry about it by having a chip that doesn't need to have massively unbalanced memory allocation in the first place. In other words, having a cast on your broken leg sure isn't a "performance benefit" compared to not having a broken leg.

Did you even bother to read that Wikipedia article?