Assessing Cavium's ThunderX2: The Arm Server Dream Realized At Last

by Johan De Gelas on May 23, 2018 9:00 AM EST- Posted in

- CPUs

- Arm

- Enterprise

- SoCs

- Enterprise CPUs

- ARMv8

- Cavium

- ThunderX

- ThunderX2

Java Performance: Huge Pages Investigated

Since experience tells us that it is quite rare for one CPU to beat another in a benchmark by a factor 3, we investigated the matter further. The most obvious candidate was Huge Pages, or as everybody besides the Linux community calls it: "Large Pages".

Every modern CPU caches the virtual-to-physical memory mappings in their TLBs. The "normal" size of a page is 4 KB, so with 1536 entries, the Skylake core can only cache about 6 MB per core. Consequently, as DRAM capacity has grown the past 15 years from a few GB to hundreds of GBs, TLB misses have become more and more of a concern. A TLB miss is quite expensive – costing several memory accesses in total – as you need to read out several tables to finally find the physical address.

All modern CPU support larger pages. In the x86-64 (Intel & AMD) a 2 MB large page is the most popular option, while a 1 GB page is also available. Meanwhile a large page on the ThunderX2 is no less than 0.5 GB. Using large pages reduces the number of TLB misses (although the number of entries in the TLB is typically much lower for large pages), and also they reduce the number of memory accesses needed if a TLB miss occurs.

However, it took a while before Linux supported this feature in an easy to handle way. Memory fragmentation, conflicting and hard to configure settings, incompatibilities, and especially very confusing names caused a lot of trouble. In fact, many software vendors still advise server admins to disable large pages. So while it was quickly embraced for benchmarks, the software community as a whole is still hesitant.

To that end, let's see what happens if we enable Transparent Huge Pages and keep the best settings we discussed on the previous page.

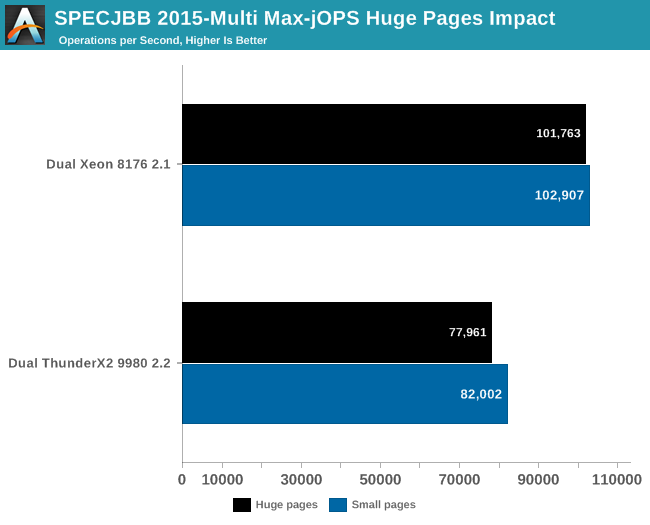

Overall, for Max-jOPs the performance impact is nothing spectaculair; in fact it's a slight regression. The Xeon loses about 1% of its throughput, the ThunderX2 about 5%.

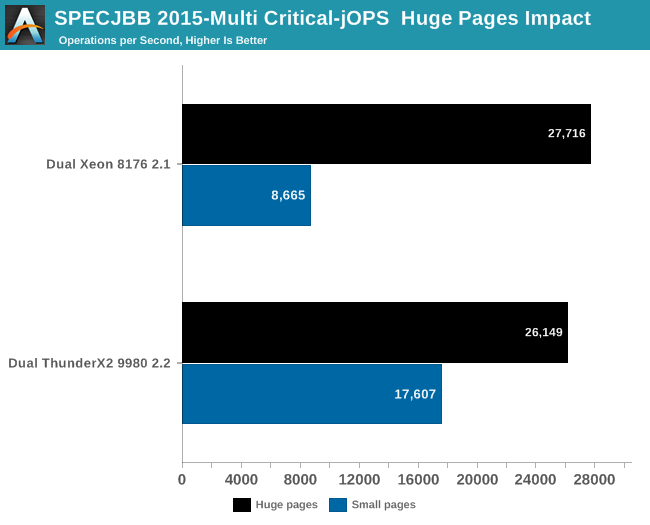

Moving on, let's check out the Critical-jOPS metric, where throughput is measured with a 99 percentile response time constraint.

A massive difference! Instead of taking a massive beating, the Intel setup edges out the ThunderX2. Still, it must be said that performance with 4 KB pages seems to be a major weakness with Intel's architecture.

97 Comments

View All Comments

DrizztVD - Wednesday, May 23, 2018 - link

It amazes me how the one big advantage ARM could have is the power efficiency, yet no power efficiency numbers in this review? It's like someone just isn't thinking about what can best showcase the ARM advantage and testing it.boeush - Thursday, May 24, 2018 - link

You must have missed this bit:"So as is typically the case for early test systems, we are not able to do any accurate power comparisons.

In fact, Cavium claims that the actual systems from HP, Gigabyte and others will be far more power efficient."

This was an early (and apparently quite buggy, especially from the power management standpoint) test system. It's not representative of final production systems in these respects, so doing what you request on it would only put a very crude lower bound on efficiency, at best.

That's why the final section of the write-up has a title ending in ": so far"... (obviously, there will be more to come if/when real production-quality systems are available for benchmarking/analysis.)

ZolaIII - Thursday, May 24, 2018 - link

It's broken currently on the MB. If you want to see real power/performance metrics for a SoC made on comparable lithography to the lintels 14 nm (aka TSMC 10nm) & with optimised software read this:https://blog.cloudflare.com/neon-is-the-new-black/

drwho9437 - Wednesday, May 23, 2018 - link

Thanks Johan, I've been reading since Ace's. I can't believe it has been more almost 20 years. Even though I don't work in this market I still read everything you write.JohanAnandtech - Friday, May 25, 2018 - link

It was indeed almost 20 years ago that I published my first article about the K6-2 vs Pentium MMX. And Anand's star was about to rise with the launch of the K6-3 :-).Spatz - Wednesday, May 30, 2018 - link

Wow. Aces hardware... that used to be my go to for hardware reviews back in the day. I can’t believe your still at it! This article was great. Keep up the good work.beginner99 - Thursday, May 24, 2018 - link

So it for sure is an option. however I d not get the focus on price. The CPU cost is a small fraction of the total server cost and a tiny if infrastructure cost (network, HVAC,...) is included. Add to that the software and data running on that server and if your CPU is 5% faster at same power it costing $5000 more might be totally worth it.Apple Worshipper - Thursday, May 24, 2018 - link

Errmm... does ARM feature SMT now?Ryan Smith - Thursday, May 24, 2018 - link

Not in Arm's own cores. But in Cavium's ThunderX2, yes.sgeocla - Thursday, May 24, 2018 - link

What's up with EPYC comparison missing in almost all benchmarks?EPYC has been out for a while and the only benchmarks are from almost a year ago?