The Intel Core i9-7980XE and Core i9-7960X CPU Review Part 1: Workstation

by Ian Cutress on September 25, 2017 3:01 AM ESTOpinion: Why Counting ‘Platform’ PCIe Lanes (and using it in Marketing) Is Absurd

It’s at this point that I’d like to take a detour and discuss something I’m not particularly happy with: counting PCIe lanes.

The number of PCIe lanes on a processor, for as long as I can remember, has always been about which lanes come directly from the PCIe root, offering full bandwidth and with the lowest possible latency. In modern systems this is the processor itself, or in earlier, less integrated systems, the Northbridge. By this metric, a standard Intel mainstream processor has 16 lanes, an AMD Ryzen has 16 or 20, an Intel HEDT processor has 28 or 44 depending on the model, and an AMD Ryzen Threadripper has 60.

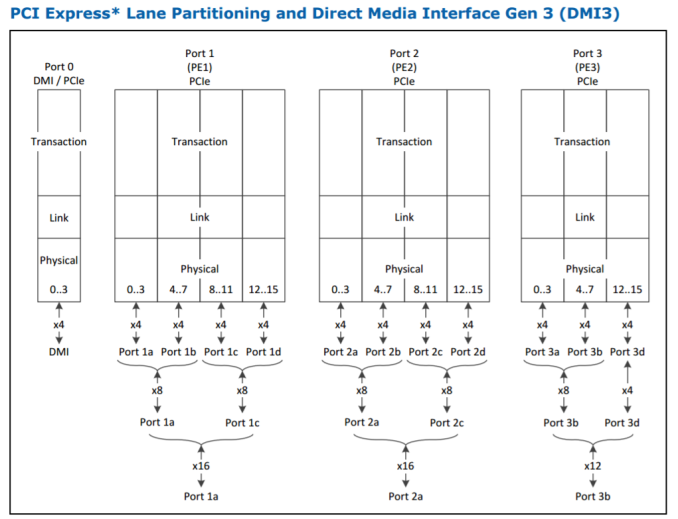

In Intel’s documentation, it explicitly lists what is available from the processor via the PCIe root complexes: here 44 lanes come from two lots of sixteen and one twelve lane complex. The DMI3 link to the chipset is in all but name a PCIe 3.0 x4 link, but is not included in this total.

The number of PCIe lanes on a chipset is a little different. Chipsets are for all practical purposes PCIe switches: using a limited bandwidth uplink, it is designed to carry traffic from low bandwidth controllers, such as SATA, Ethernet, and USB. AMD is limited in this regard, due to spending more time re-entering the pure CPU performance race over the last few years and outsource their designs to ASMedia. Intel has been increasing its PCIe 3.0 lane support on its chipsets for at least three generations, now supporting up to 24 PCIe 3.0 lanes. There are some caveats on what lanes can support which controllers, but in general we consider this 24.

Due to the shared uplink, PCIe lanes coming from the chipset (on both the AMD and Intel side) can be bottlenecked very easily, as well as being limited to PCIe 3.0 x4. The chipset introduces additional latency compared to having a controller directly attached to the processor, which is why we rarely see important hardware (GPUs, RAID controllers, FPGAs) connected to them.

The combination of the two lends itself to a variety of platform functionality and configurations. For example, for AMD's X399 platform that has 60 lanes from the processor, the following combinations are 'recommended':

| X399 Potential Configurations | |||

| Use | PCIe Lanes | Total | |

| Content Creator | 2 x Pro GPUs 2 x M.2 Cache Drives 10G Ethernet 1 x U.2 Storage 1 x M.2 OS/Apps 6 x SATA Local Backup |

x16/x16 from CPU x4 + x4 from CPU x4 from CPU x4 from CPU x4 from CPU From Chipset |

52 Lanes |

| Extreme PC | 2 x Gaming GPUs 1 x HDMI Capture Card 2 x M.2 for Games/Stream 10G Ethernet 1 x M.2 OS/Apps 6 x SATA Local Backup |

x16/x16 from CPU x8 from CPU x4 + x4 from CPU x4 from CPU x4 from CPU From Chipset |

56 Lanes |

| Streamer | 1 x Gaming GPU 1 x HDMI Capture Card 2 x M.2 Stream/Transcode 10G Ethernet 1 x U.2 Storage 1 x M.2 OS/Apps 6 x SATA Local Backup |

x16 from CPU x4 from CPU x4 + x4 from CPU x4 from CPU x4 from CPU x4 from CPU From Chipset |

40 Lanes |

| Render Farm | 4 x Vega FE Pro GPUs 2 x M.2 Cache Drives 1 x M.2 OS/Apps 6 x SATA Local Backup |

x16/x8/x8/x8 x4 + x4 from CPU x4 from CPU From Chipset |

52 Lanes |

What has started to happen is that these companies are combining both the CPU and chipset PCIe lane counts, in order to promote the biggest number. This is despite the fact that not all PCIe lanes are equal, they do not seem to care. As a result, Intel is cautiously promoting these new Skylake-X processors as having ’68 Platform PCIe lanes’, and has similar metrics in place for other upcoming hardware.

I want to nip this in the bud before it gets out of hand: this metric is misleading at best, and disingenuous at worst, especially given the history of how this metric has been provided in the past (and everyone will ignore the ‘Platform’ qualifier). Just because a number is bigger/smaller than a vendor expected does not give them the right to redefine it and mislead consumers.

To cite precedent: in the smartphone space, around 4-5 years ago, vendors were counting almost anything in the main processor as a core to provide a ‘full core count’. This meant that GPU segments became ‘cores’, special IP blocks for signal and image processing became ‘cores’, security IP blocks became ‘cores’. It was absurd to hear that a smartphone processor had fifteen cores, when the main general purpose cores were a quartet of ARM Cortex A7 designs. Users who follow the smartphone industry will notice that this nonsense stopped pretty quickly, partly due to anything being called a core, but some hints towards artificial cores potentially being placed in the system. If allowed to continue, this would have been a pointless metric.

The same thing is going to happen if the notion of ‘Platform PCIe Lanes’ is allowed to continue.

152 Comments

View All Comments

Krysto - Monday, September 25, 2017 - link

Yes, it's total bullshit that they are misinterpreting what TDP is. I imagine this is how they'll get away with claiming a lower TDP than the real one in the 8700k chip, too, which has low base clock speed, but the super-high Turbo-Boost, which probably means the REAL TDP will go through the rough when that Turbo Boost is maximized.This is how Intel will get to claim that its chips are still faster than AMD "at the same TDP" (wink wink, nudge nudge).

Demigod79 - Monday, September 25, 2017 - link

"What a load of ignorance. Intel tdp is *average* power at *base* clocks, uses more power at all core turbo clocks here. Disable turbo if that's too much power for you."I find it ironic that you would call someone ignorant, then reveal your own ignorance about the TDP and turbo clocks.

Spunjji - Monday, September 25, 2017 - link

It is now, it wasn't before. Wanna bet on how many people noticed?SodaAnt - Monday, September 25, 2017 - link

I'm quite curious what happens if your system cooling simply can't handle it. I suspect if you designed a cooling solution which only supported 165W the CPU would simply throttle itself, but I'm curious by how much.ZeDestructor - Monday, September 25, 2017 - link

Strictly speaking, all forms of Turbo boost are a form of vendor-sanctioned overclocking. The fact that measured power goes beyond TDP when at max all-core turbo should really not be all that surprising. The ~36% increase in power for ~31% increase in clocks is pretty reasonable and inline when you keep that in mind. Especially when you factor that there has to have been a bit of extra voltage added for stability reasons (power scales linearly with clocks and current, and quadratically to exponentially with voltage).Demigod79 - Monday, September 25, 2017 - link

I agree. Everything looked good until that page. 190 watts is unacceptable, and Intel needs to correct this right away - either make the CPU run within the TDP limit, or update the TDP to 190 watts in the specs.HStewart - Monday, September 25, 2017 - link

It funny that people complain about CPU watts but never about external GPU watts. Keep in mind the GPU is smaller amount of area.artk2219 - Monday, September 25, 2017 - link

They most certainly do, that is one of the biggest gripes against Vega 64, people do seem to have short memory on how high GPU TDP's used to be however.IGTrading - Tuesday, September 26, 2017 - link

On a video card, the same manufacturer takes responsibility for the GPU, cooling system, design, PCB, components and warranty.On the CPU, you have somebody else designing the cooling system, the motherboard, the power lines and they all have to offer warranty for their components while Intel is only concerned with the CPU.

If the CPU is throttling or burnt out, they will say "sufficient cooling was not provided" and so on ...

It is a whole lot different.

whatevs - Tuesday, September 26, 2017 - link

Thermal throttling is not a burn out and not a warranty event, you don't get to warranty your gpu when it throttles under load, cooling warranty does not include cpu/gpu chip performance andIntel designed the ATX specification and the electrical specification for the boards.

You clearly don't know the things you're talking about.