Sizing Up Servers: Intel's Skylake-SP Xeon versus AMD's EPYC 7000 - The Server CPU Battle of the Decade?

by Johan De Gelas & Ian Cutress on July 11, 2017 12:15 PM EST- Posted in

- CPUs

- AMD

- Intel

- Xeon

- Enterprise

- Skylake

- Zen

- Naples

- Skylake-SP

- EPYC

AMD's EPYC Server CPU

If you have read Ian's articles about Zen and EPYC in detail, you can skip this page. For those of you who need a refresher, let us quickly review what AMD is offering.

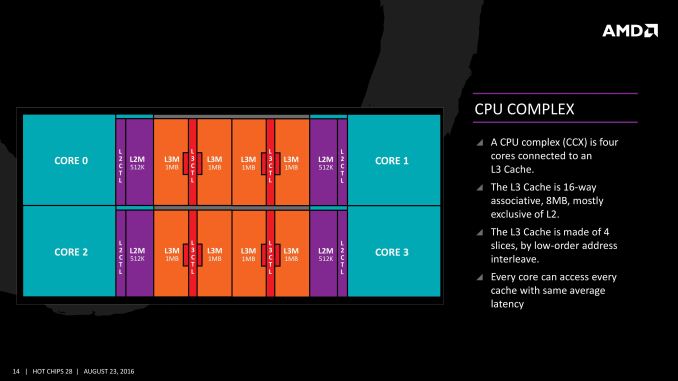

The basic building block of EPYC and Ryzen is the CPU Complex (CCX), which consists of 4 vastly improved "Zen" cores, connected to an L3-cache. In a full configuration each core technically has its own 2 MB of L3, but access to the other 6 MB is rather speedy. Within a CCX we measured 13 ns to access the first 2 MB, and 15 to 19 ns for the rest of the 8 MB L3-cache, a difference that's hardly noticeable in the grand scheme of things. The L3-cache acts as a mostly exclusive victim cache.

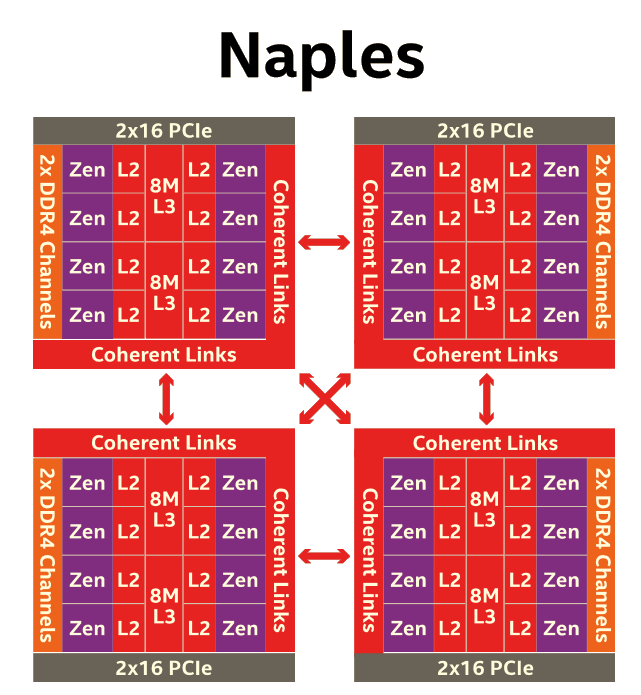

Two CCXes make up one Zeppelin die. A custom fabric – AMD's Infinity Fabric – ties together two CCXes, the two 8 MB L3-caches, 2 DDR4-channels, and the integrated PCIe lanes. That topology is not without some drawbacks though: it means that there are two separate 8 MB L3 caches instead of one single 16 MB LLC. This has all kinds of consequences. For example the prefetchers of each core make sure that data of the L3 is brought into the L1 when it is needed. Meanwhile each CCX has its own separate (not inside the L3, so no capacity hit) and dedicated SRAM snoop directory (keeping track of 7 possible states). In other words, the local L3-cache communicates very quickly with everything inside the same CCX, but every data exchange between two CCXes comes with a tangible latency penalty.

Moving further up the chain, the complete EPYC chip is a Multi Chip Module(MCM) containing 4 Zeppelin dies.

AMD made sure that each die is only one hop apart from the other, ensuring that the off-die latency is as low as reasonably possible.

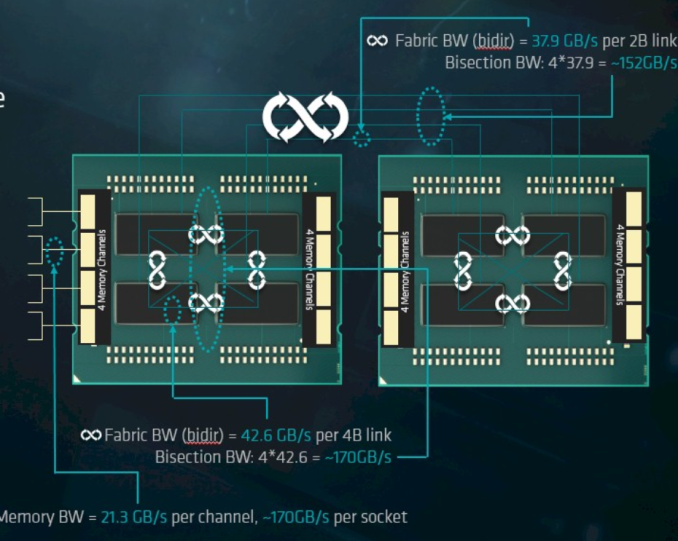

Meanwhile scaling things up to their logical conclusion, we have 2P configurations. A dual socket EPYC setup is in fact a "virtual octal socket" NUMA system.

AMD gave this "virtual octal socket" topology ample bandwidth to communicate. The two physical sockets are connected by four bidirectional interconnects, each consisting of 16 PCIe lanes. Each of these interconnect links operates at +/- 38 GB/s (or 19 GB/s in each direction).

So basically, AMD's topology is ideal for applications with many independently working threads such as small VMs, HPC applications, and so on. It is less suited for applications that require a lot of data synchronization such as transactional databases. In the latter case, the extra latency of exchanging data between dies and even CCX is going to have an impact relative to a traditional monolithic design.

219 Comments

View All Comments

sharath.naik - Wednesday, July 12, 2017 - link

http://www.anandtech.com/show/10158/the-intel-xeon...Here is the link for you a single Xeon E5 v4 22 core does 5.3 (Dual at 5.9)jobs a day compared to dual Epyc 6.3. Ok they are 7% apart for dual socket but only 15% faster for dual epyc compared to single Xeon E5. Big Data does not do well in NUMA set up, same is the case with any regular large data applications. Try running EPYC without splitting spark into multiple processes, you will see how terrible a dual EPYC is going to be (the review mentions it but does not give a graph). Now this is terrible, to use EPYC first you need to change the way you build and run the applications and then expect 7-15% advantage vs a 2000$ CPU. It simple shows that EPYC is only use full for VMs and some synthetic tests. Any applications that deal with data can and should stay away from EPYC

warreo - Friday, July 14, 2017 - link

Why are you comparing Spark 1.5 benchmarks against 2.1.1? Johan pointed out in the article why they are not comparable and why he is using the new 2.1.1 benchmark.The exact Dual Xeon E5 2699 v4 you are referencing that did 5.9 jobs per day in Spark 1.5 only does 4.9 jobs per day on Spark 2.1.1. If we assume a similar % gap between dual and single as it was in Spark 1.5, then a single Xeon E5 2699 v4 would be capable of only 4.4 jobs per day in Spark 2.1.1, which is a 43% difference compared to dual Epycs.

Even leaving that aside, your exact arguments can be applied to the new Xeons as well, which are only 5% faster than the Epycs. Do you think the new Xeons suck as well?

Same thing for splitting Spark into multiple processes and needing to re-write applications -- you also run into the exact same issue with the new Xeons (which Johan also explictly points out).

Based on your arguments, I'm confused why you are taking aim only at Epyc and not the new Xeons. Please let me know if I'm missing something here.

AleXopf - Wednesday, July 12, 2017 - link

Username checks outdeltaFx2 - Wednesday, July 12, 2017 - link

"four 8core desktop dies" Oh, on the contrary. It's really a 4 die MCM server part, and each die is being sold as a desktop part. Nobody puts interconnect (fabric) on a desktop part. MCM is something intel has also done way back in the dual core era, and IBM continues to do. Don't float that canard re. desktop parts, it's just a design choice. AMD isn't trying to beat Intel in every market, just in some, and it does that. It might not win in HPC or big enterprise database (idk), but if you are a public cloud provider in the business of renting 4c8t or 8c16t VMs, AMD has a solid product. Now throw in the 128 PCIe lanes, which intel can't come close to. In fact, a 32c Naples in 1P is something that Intel has nothing to compete against for applications like storage, GPGPU, etc. The question isn't if it's good enough to run Intel out of business in the server space; that's not happening. It didn't when AMD had a superior product in Opteron. The question is, is it good enough for 5-10% market share in 2018-2019?"Intel cores are superior than AMD so a 28 core xeon is equal to ~40 cores if you compare again Ryzen core so this whole 28core vs 32core is a marketing trick". And yet all the numbers presented above point to the opposite. Ryzen != Epyc and i7700K != Syklake EP/SP, if that's where you're getting your numbers from. If not, present data.

Amiga500 - Wednesday, July 12, 2017 - link

No surprise that the Intel employee is descending to lies and deceit to try and plaster over the chasms! They've also reverted to bribing suppliers to offer Ryzen with only crippled memory speeds too (e.g. pcspecialist.co.uk - try and get a Ryzen system with >2133 MHz memory, yet the SKL-X has up top 3600 MHz memory --- the kicker is - they used to offer Ryzen at up to 3000 MHz memory!). It would seem old habits die hard.Hopefully the readers are wise enough to look at the performance data and make their decisions from that.

If OEMs are willing to bend to Intels dirty dollars, I trust customers will eventually choose to take their business elsewhere. We certainly won't be using pcspecialist again in the near future.

Shankar1962 - Wednesday, July 12, 2017 - link

Look at the picture in this article and see what the big players reported when they upgraded to SkylakeDon't hate a company for the sake of argument. The world we live today from a hardware technology standpoint is because of Intel and respect it

https://www.google.com/amp/s/seekingalpha.com/amp/...

Shankar1962 - Wednesday, July 12, 2017 - link

I agree. Intel has been a data center leader and pioneered for decades now. It has proven track record and overall platform stability consistency and strong portfolio and roadmap. With intel transforming to a data company i see that the best is yet to come as it did smart acquisitions and I believe products with IP from those aquired companies are still nnot fully integrated. Everyone loves an underdog and its clear that everyones excited as someone is getting 5% share and Intel won't be sitting....they did it in the past they will do it again:)0ldman79 - Wednesday, July 12, 2017 - link

I find the power consumption info quite interesting, especially considering the TDP ratings for the processors.The platform makes a difference, though I wonder what the actual difference is. Intel and AMD have been rating their TDP differently for years now.

Atom11 - Wednesday, July 12, 2017 - link

After all these tests we still know nothing about AVX512. According to the specs, the floating point should be about 2x faster on CPU with AVX512 in compare to CPU without AVX512. There should be a clear line between Gcc and Icc. Gcc compiler does not support AVX512 anyway and it otherwise also has a relatively limited vectorization support. Not using Icc means, not using the only compiler which actually supports the Intel hardware features. But it yes, it is a difficult comparison, because you need both Instructions and Software which uses those instructions optimized the best way possible and some users simply don't bother about using optimized software. It would be nice to see comparison between: GCC+ AMD and ICC+Intel. So that only compiler is changed, but also the code is written so that it is possible for it to be efficiently vectorized and threaded. What can I get on Intel, if I use best possible software stack and what can I get on AMD? The current article only answers the question: What can i get on AMD and Intel if I dont bother with software stack and optimization.yuhong - Wednesday, July 12, 2017 - link

Inphi has a press release about shipping 1 million DDR3 LR-DIMM buffers six months before the launch of Haswell-E: https://www.inphi.com/media-center/press-room/pres... I wonder how many they shipped total so far (and also Montage).