AMD 7th Gen Bristol Ridge and AM4 Analysis: Up to A12-9800, B350/A320 Chipset, OEMs first, PIBs Later

by Ian Cutress on September 23, 2016 9:00 AM ESTMotherboards, Sockets, Pins and Things

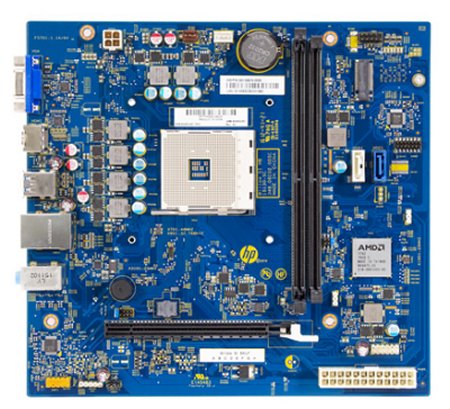

As an OEM only launch, details about exact systems coming to market (and how they are designed) is providing slim pickings. With a normal retail launch, we have several motherboard manufacturers to dig our teeth into when asking questions, however our relationships with the major OEMs such as HP, Dell or Lenovo are quite different and typically more product focused and less engineering. We’ve not seen any real Bristol Ridge related announcements on OEM systems coming into the market, but some do exist. Reddit user starlightmica saw this HP Pavilion 510-p127c in Costco this week:

$600 gets an A12-9800, 16GB of DDR4, a 1TB mechanical drive, an additional R7 2GB graphics card, 802.11ac WiFi, a DVDRW drive, and a smattering of USB ports (but no USB 3.1, which is interesting).

We reached out to HP, as this system was listed online with the blurriest of motherboard images.

This is a ‘Willow’ motherboard, and we can see the AM4 socket in the middle. Contrary to previous platforms, it is worth noting that the socket mounting holes are significantly more ‘square’ than previous motherboard designs. However, when we discussed the images of the South Korean overclocker near the beginning of this article, it looked like he was using a standard AMD Wraith cooler, which might suggest that this square mounting hole situation might just be HP designing the motherboard.

The board clearly has six phases as part of the power delivery, plus an additional phase for the memory. I would assume that since the system has dual channel support, HP has developed the two memory slots as having dual channel capability, and the abundance of traces from the APU seems to suggest that as well.

To the right of the DRAM slots seems to be a PCIe x1 slot, which is where I assume the WiFi module is held. Below this slot are two of the system SATA ports, followed by what looks like a chipset with a big AMD logo on it and then the 24-pin power connector.

The motherboard has a full PCIe 3.0 x16 sized slot, although as we discussed before, this will be limited to PCIe 3.0 x8 due to the design of the processor. To the left of this is clearly a Realtek audio codec, and judging by the 2.1 support on the rear panel, this is most likely an ALC269 or some other low-end codec. It is hard to tell where the network controller is here without the high-resolution image, but just above and to the left of the speaker looks like a small IC which looks similar to Realtek’s low-end solutions. Typically Realtek offers a deal when audio+networking chips are used in the same system, so I suspect that is what is happening here. Above this are our USB ports, an HDMI output, and a VGA port which must be using a DP-to-VGA IC onboard.

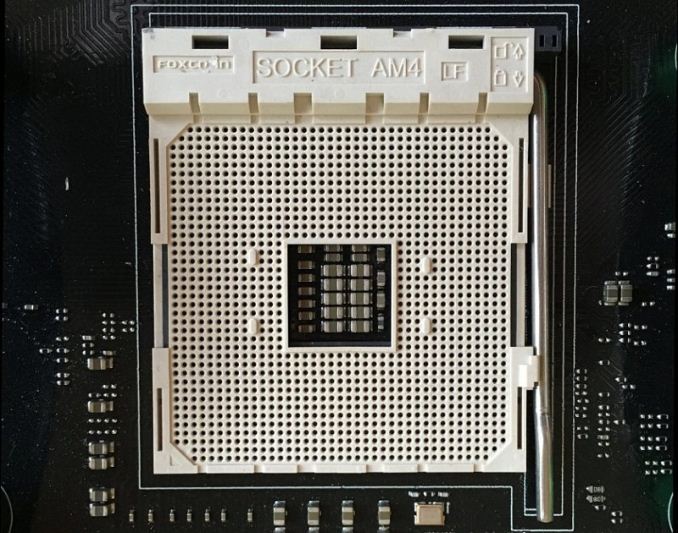

We have closer up images of the socket, thanks to the Hungarian website hwsw:

This looks like the standard ZIF socket we’ve come to love/loathe from AMD (I doubt there’s a way that keeps everyone happy anyway), and others have counted 1331 holes which may/may not do things.

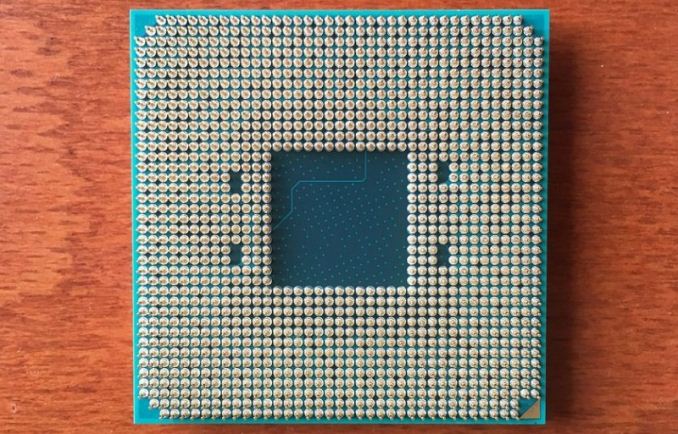

The rear of the CPU, also from hwsw, is what we would expect given the socket layout. It does mean that AMD is stuck at this level of connectivity, to anyone wishing for a quad-channel AMD platform suitable for consumers will have to wait until a future platform. It’s also worth noting that this looks like a similar size to when AMD CEO Lisa Su held up a Zen chip for the press back at the Zen announcements in August.

What Happens Now

Aside from spotting systems like the HP in Costco, no doubt a number of media outlets (us included) are trying to get hold of a number of the APUs for official reviews. As mentioned previously, that A12-9800 looks like an exciting all round part. We are working with AMD to secure the platform and the APUs for testing.

AMD has told us that Bristol Ridge APUs are designed to have price parity with the current Kaveri Refresh/Godavari models, however exact configurations of APUs and coolers, as well as a timeframe for the motherboard manufacturers to come out with their designs, is still to be decided.

I suspect that AMD will wait until closer to the Zen launch window to put Bristol Ridge on the shelves. Attacking the market with a new platform that goes from the high-end desktop through to all but the cheapest systems would mean a concerted effort to gain market share and recognition for catering to the performance needs of as many users as possible all at once. AMD has promised that Zen will trickle down the stack, however as we were told regarding their server and laptop plans later in 2017, that will mostly likely occur later in the year also.

If you’ve read through this piece, or merely skipped to the last page for the conclusions, here’s the take away from the Bristol Ridge for desktop launch:

- OEMs first, DIY builds later

- The A12 at 65W has better specifications than the best previous generation A10 at 95W

- Even at 65W, there is +30% frequency on the integrated graphics for the A12-9800

- The chipsets support USB 3.1 (10 Gbps) natively, but Type-C requires a small additional chip

- Bristol Ridge is more like an SoC, the chipset is entirely optional

- There are so many fun things you can do with PCIe and switches

- We expect the retail APUs to be price drop-ins for current APUs

- We’re trying to get these APUs for review. Stay tuned.

122 Comments

View All Comments

Alexvrb - Sunday, September 25, 2016 - link

Geekbench is trash at comparing across different architectures. It makes steaming piles look good. Only using SSE (first gen, ancient) on x86 processors would certainly be a part of the puzzle regarding Geekbench results. Thanks, Patrick.Not to take anything away from Apple's cores. I wouldn't be surprised that they have better performance per WATT than Skylake. Perf/watt is kind of a big deal for mobile, and Apple (though I don't care for them as a company) builds very efficient processor cores. With A10 using a big.LITTLE implementation of some variety, they stand to gain even more efficiency. But in terms of raw performance? Never rely on Geekbench unless maybe you're comparing an A9 Apple chip to an A10 or something. MAYBE.

ddriver - Monday, September 26, 2016 - link

Hey, it is not me who uses crap like geekbench and sunspider to measure performnace, it is sites like AT ;)BurntMyBacon - Monday, September 26, 2016 - link

@ddriver: "Hey, it is not me who uses crap like geekbench and sunspider to measure performnace, it is sites like AT ;)"LOL. My gut reaction was to call you out on blame shifting until I realized ... You are correct. There hasn't exactly been a lot of benchmark comparison between ARM and x86. Of course, there isn't much out there with which to compare either so ...

patrickjp93 - Monday, September 26, 2016 - link

Linpack and SAP. Both are massive benchmark suites that will give you the honest to God truth, and the truth is ARM is still 10 years behind.patrickjp93 - Monday, September 26, 2016 - link

They use it in context and admit the benchmarks are not equally optimized across architectures.patrickjp93 - Monday, September 26, 2016 - link

It doesn't even use SSE. It uses x86_64 and x87 scalar float instructions. It doesn't even give you MMX or SSE. That's how biased it is.patrickjp93 - Monday, September 26, 2016 - link

Just because you write code simply enough using good modern form and properly align your data and make functions and loops small enough to be easily optimized does not mean GCC doesn't choke. Mike Acton gave a great lecture at CPPCon 2014 showing various examples where GCC, Clang, and MVCC choke.Define very good.

Define detailed analysis. Under what workloads? Is it more efficient for throughput or latency (because I guarantee it can't be both)?

Yes, Geekbench uses purely scalar code on x86 platforms. It's ludicrously pathetic.

It's 8x over scalar, and that's where it matters, and it can even be better than that because of loop Muop decreases which allow the loops to fit into the detector buffers which can erase the prefetch and WB stages until the end of the loop.

No, they're not more powerful. A Pentium IV is still more powerful than the Helio X35 or Exynos 8890.

No, those are select benchmarks that are more network bound than CPU bound and are meaningless for the claims people are trying to make based on them.

BurntMyBacon - Monday, September 26, 2016 - link

@ddriver: "I've been using GCC mostly, and in most of the cases after doing explicit vectorization I found no perf benefits, analyzing assembly afterwards revealed that the compiled has done a very good job at vectorizing wherever possible."It's not just about vectorizing. I haven't taken a look at Geekbench code, but it is pretty easy to under-utilize processor resources. Designing workloads to fit within a processors cache for repetitive operations is a common way to optimize. It does, however, leave a processor with a larger cache underutilized for the purposes of the workload. Similar examples can be found for wide vs narrow architectures and memory architectures feeding the processor. Even practical workloads can be done various ways that are much more or less suitable to a given platform. Compression / Encoding methods are some examples here.

BurntMyBacon - Monday, September 26, 2016 - link

@patrickjp93: "Yes you can get 5x the performance by optimizing. Geekbench only handles 1 datem at a time on Intel hardware vs. the 8 you can do with AVX and AVX2. Assuming you don't choke on bandwidth, you can get an 8x speedup."If you have processor with a large enough cache to keep a workload almost entirely in cache and another with far less cache that has to access main memory repetitively to do the job, the difference can be an order of magnitude or more. Admittedly, the type of workload that is small enough to fit in any processor cache isn't common, but I've seen cases of it in benchmarks and (less commonly in) scientific applications.

patrickjp93 - Tuesday, September 27, 2016 - link

Heh, they're usually based on Monte Carlo simulations if they can.