Intel's 0.09-micron Process - More Details Emerge

by Anand Lal Shimpi on August 13, 2002 4:02 AM EST- Posted in

- CPUs

Getting Ready for Prescott - The 7th Layer

All of Intel's 0.13-micron parts presently employ 6 metal layers using copper interconnects to optimize circuit density and manufacturing cost; with the 90nm manufacturing process Intel has decided to add a 7th metal layer to allow for ~100M+ transistor designs such as Prescott and Montecito to be manufactured in the most efficient way possible.

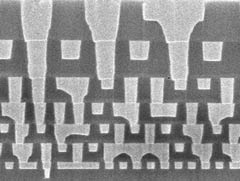

Can you count the 7 metal layers?

Some of the other features of Intel's 90nm process are beyond the scope of this article but include:

- 1.2nm gate oxide thickness (thinnest gate oxide in the industry)

- 50nm gate length initially, scaling down to even smaller gate lengths over the next two years (compared to 70nm gate lengths initially on the 0.13-micron process and currently 60nm)

- A new low-k Carbon-doped oxide dielectric to reduce wire-wire capacitance (thus reducing power)

The results of these improvements are of course, higher clock speeds and lower operating voltages. The first 90nm transistors will operate at a 1.20V and eventually scale down to even lower voltages; this should give you an idea of the core voltages you can expect to see on Prescott, depending on clock frequency of course.

0 Comments

View All Comments