Fall IDF 2006 - Day 1: 45/65nm, UMPC Update and Quad-Core

by Anand Shimpi & Larry Barber on September 26, 2006 5:03 PM EST- Posted in

- CPUs

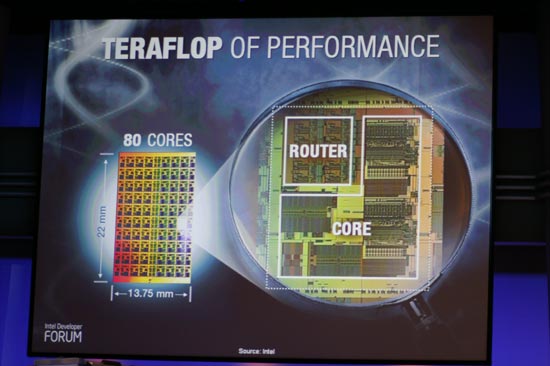

Intel's Answer to Cell: The Teraflop chip

When Sony's Cell architecture was first introduced, everyone looked to Intel for an answer - and the best we got was that the foreseeable future of multi-core computing would be x86 based. When Cell was first announced, a processor with 9 cores was unheard of as we were just being introduced to Intel's dual core offerings and quad core was just a pipedream. By the time the PlayStation 3 launches, dual socket Xeon systems will be able to have the power of 8 very powerful x86 cores and all of the sudden the number of cores in Cell stops being so impressive. But there is quite a bit of merit to Cell's architecture and design, as Intel has alluded to many times in the past, and today Intel showcased a processor that is very similar in design.

Intel outfitted a single chip with a total of 80 very simply cores, that combined can execute a peak rate of 1 trillion floating point operations per second. Each core uses a very simple instruction set, only capable of executing floating point code, and are individually quite weak. But the combined power of the 80 cores is quite impressive, and it's directly taking a page from the book of Cell. While Cell's SPEs are likely more powerful than each of the cores in the teraflop chip, the design mentality is similar.

The facial expression is a side effect of holding a wafer of teraflop chips

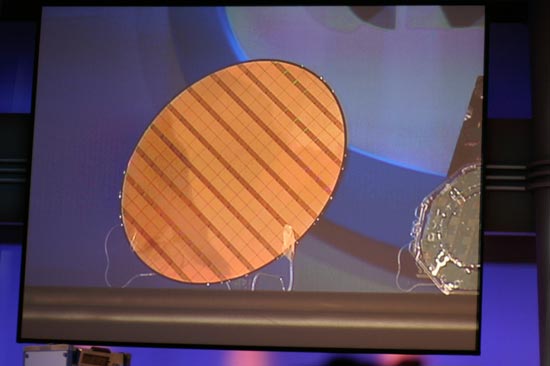

Intel showed off a wafer of these teraflop chips, with a target clock speed of 3.1GHz and power consumption of about 1W per 10 gigaflops - or 100W for 1 TFLOP. The chip is simply a technology demo and won't be productized in any way, but in the next 5 years don't be too surprised if you end up seeing some hybrid CPUs with a combination of powerful general purpose cores with smaller more specialized cores.

12 Comments

View All Comments

GNStudios - Wednesday, September 27, 2006 - link

Is Quad-core going to much faster than dual-core, like when core 2 duo came?Reply is appriciated. :-)

Niv KA - Wednesday, September 27, 2006 - link

I have reasons to belive that whatever will come after Gesher will be very different from what we have today. Gesher is translated to brigde in Hebrew. Therefore I have reason to belive that what ever Gesher will be, it will be a transition to a new technology.I know I repeated myself a few times.

-- Niv K Aharonovich

sprockkets - Wednesday, September 27, 2006 - link

It used a Netburst and most likely a prescott core processor to operate WTF?GhandiInstinct - Wednesday, September 27, 2006 - link

The day, in a press conference, the day in which multi-code is mastered in software, that we see in a video game demo, a full fledged Torando tearing down a metropolis.yacoub - Tuesday, September 26, 2006 - link

Good coverage so far: Lots of pics, informative text between them, and lots of new tech incoming from Intel! wootporkster - Tuesday, September 26, 2006 - link

Any news on Santa Rosa chipsets? I couldn't see them in the road map.porkster - Tuesday, September 26, 2006 - link

Intel and Microsoft have no idea when it comes to what people will buy and can afford.Ye, like in the picture we are all going to buy 3 and 4 of these flop devices for our cars. Without these devices being under $200, no one will take then serious.

It seems like anytime someone bring up a portable, they have to use an expensive cpu in it. I can't see why you can't jsut echo a wifi'ed screen from another computer at home or in the car. A device the is a terminal, not a separate computer.

mino - Tuesday, September 26, 2006 - link

"Years ago Micron talked about equipping a chipset with an on-die L3 cache to help improve performance, and it's looking like Intel will be doing just that"IBM has it since 2002 ... ;)

BTW it was the main reason IMB did not jump on Opteron so eagerly. They have a chipset hugely hugely superior to Itel's Truland since 2003. Game over period.

That snoop cache is the thing which brought SC Nocona Xeons on par with SC Opterons in 4P-8P scenarios!!!

First Intel DC Smithfield _IS_ single-die, it is just glued together but single-die. The reason being MCM puts huge strain on FSB so they put an arbitter on a glued chip, to help achieve even mediocre 800FSB on their chipsets of the time.

mino - Tuesday, September 26, 2006 - link

"Years ago Micron talked about equipping a chipset with an on-die L3 cache to help improve performance, and it's looking like Intel will be doing just that"IBM has it since 2002 ... ;)

BTW it was the main reason IMB did not jump on Opteron so eagerly. They have a chipset hugely hugely superior to Itel's Truland since 2003. Game over period.

That snoop cache is the thing which brought SC Nocona Xeons on par with SC Opterons in 4P-8P scenarios!!!

BTW First Intel DC Smithfield _IS_ single-die, it is just glued together but single-die. The reason being MCM puts huge strain on FSB so they put an arbitter on a glued chip, to help achieve even mediocre 800FSB on their chipsets of the time.

mino - Tuesday, September 26, 2006 - link

screwed title, if posiible please delete/vote out. Thanks.