The AMD Radeon R9 Fury X Review: Aiming For the Top

by Ryan Smith on July 2, 2015 11:15 AM ESTThe Fiji GPU: Go Big or Go Home

Now that we’ve had a chance to take a look at the architecture backing Fiji, let’s talk about the Fiji GPU itself.

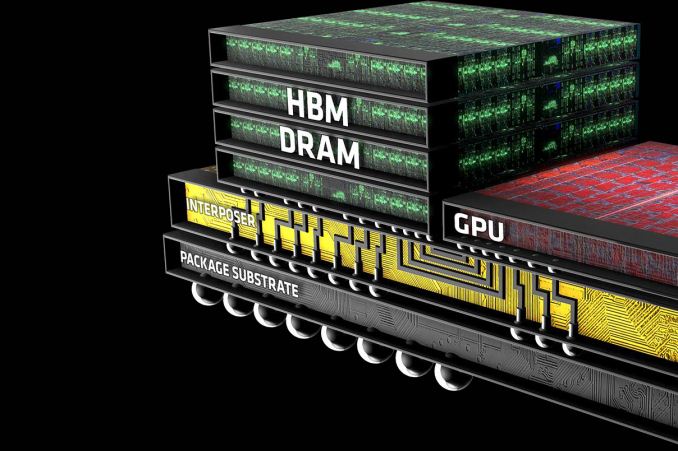

Fiji’s inclusion of High Bandwidth Memory (HBM) technology complicates the picture somewhat when talking about GPUs. Whereas past GPUs were defined by the GPU die itself and then the organic substrate package it sits on, the inclusion of HBM requires a third layer, the silicon interposer. The job of the interposer is to sit between the package and the GPU, serving as the layer that connects the on-package HBM memory stacks with the GPU. Essentially a very large chip without any expensive logic on it, the silicon interposer allows for finer, denser signal routing than organic packaging is capable of, making the ultra-wide 4096-bit HBM bus viable for the first time.

We’ll get to HBM in detail in a bit, but it’s important to call out the impact of HBM and the interposer early, since they have a distinct impact on how Fiji was designed and what its capabilities are.

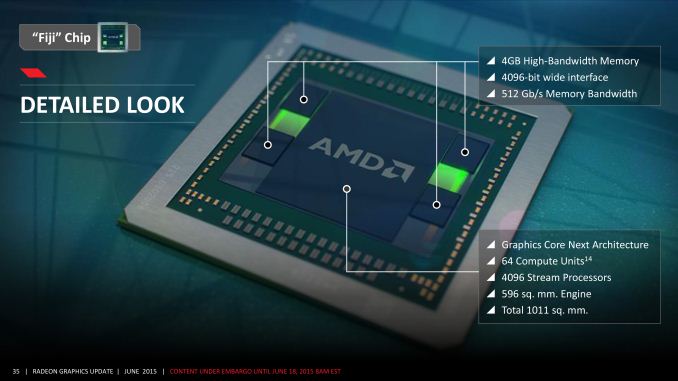

As for Fiji itself, Fiji is unlike any GPU built before by AMD, and not only due to the use of HBM. More than anything else, it’s simply huge, 596mm2 to be precise. As we mentioned in our introduction, AMD has traditionally shied away from big chips, even after the “small die” era ended, and for good reason. Big chips are expensive to develop, expensive to produce, take longer to develop, and yield worse than small chips (this being especially the case early-on for 40nm). Altogether they’re riskier than smaller chips, and while there are times where they are necessary, AMD has never reached this point until now.

The end result is that for the first time since the unified shader era began, AMD has gone toe-to-toe with NVIDIA on die size. Fiji’s 596mm2 die size is just 5mm2 (<1%) smaller than NVIDIA’s GM200, and more notably still hits TSMC’s 28nm reticle limit. TSMC can’t build chips any bigger than this; Fiji is as big a chip as AMD can order.

| AMD Big GPUs | ||||

| Die Size | Native FP64 Rate | |||

| Fiji (GCN 1.2) | 596mm2 | 1/16 | ||

| Hawaii (GCN 1.1) | 438mm2 | 1/2 | ||

| Tahiti (GCN 1.0) | 352mm2 | 1/4 | ||

| Cayman (VLIW4) | 389mm2 | 1/4 | ||

| Cypress (VLIW5) | 334mm2 | 1/5 | ||

| RV790 (VLIW5) | 282mm2 | N/A | ||

Looking at Fiji relative to AMD’s other big GPUs, it becomes very clear very quickly just how significant this change is for AMD. When Hawaii was released in 2013 at 438mm2, it was already AMD’s biggest GPU ever for its time. And yet Fiji dwarfs it, coming in at 158mm2 (36%) larger. The fact that Fiji comes at the latter-half of the 28nm process’s life time means that such a large GPU is not nearly as risky now as it would have been in 2011/2012 (NVIDIA surely took some licks internally on GK110), but still, nothing else we can show you today can really sell the significance of Fiji to AMD as much as the die size can.

And the fun doesn’t stop there. Along with producing the biggest die they could, AMD has also more or less gone the direction of NVIDIA and Maxwell in the case of Fiji, building what is unambiguously the most gaming/FP32-centric GPU the company could build. With GCN supporting power-of-two FP64 rates between 1/2 and 1/16, AMD has gone for the bare minimum in FP64 performance that their architecture allows, leading to a 1/16 FP64 rate on Fiji. This is a significant departure from Hawaii, which implemented native support for ½ rate, and on consumer parts offered a handicapped 1/8 rate. Fiji will not be a FP64 powerhouse – its 4GB of VRAM is already perhaps too large of a handicap for the HPC market – so instead we get AMD’s best FP32 GPU going against NVIDIA’s best FP32 GPU.

AMD’s final ace up their sleeve on die size is HBM. Along with HBM’s bandwidth and power benefits, HBM is also much simpler to implement, requiring less GPU space for PHYs than GDDR5 does. This is in part due to the fact that HBM stacks have their own logic layer, distributing some of the logic on to each stack, and furthermore a benefit of the fact that the signaling logic that remains doesn’t have to be nearly as complex since the frequencies are so much lower. 4096-bits of HBM PHYs still takes up a fair bit of space – though AMD won’t tell us how much – but it’s notably lower than the amount of space AMD was losing to Hawaii’s GDDR5 memory controllers.

The end result is that not only has AMD built their biggest GPU ever, but they have done virtually everything they can to maximize the amount of die space they get to allocate to FP32 and rendering resources. Simply put, AMD has never reached so high and aimed for parity with NVIDIA in this manner.

Ultimately this puts Fiji’s transistor count at 8.9 billion transistors, even more than the 8 billion transistors found in NVIDIA’s GM200, and, as expected, significantly more than Hawaii’s 6.2 billion. Interestingly enough, on a relative basis this is almost exactly the same increase we saw with Hawaii; Fiji packs in 43.5% more transistors than Hawaii, and Hawaii packed in 43.9% more transistors than Tahiti. So going by transistors alone, Fiji is very much to Hawaii what Hawaii was to Tahiti.

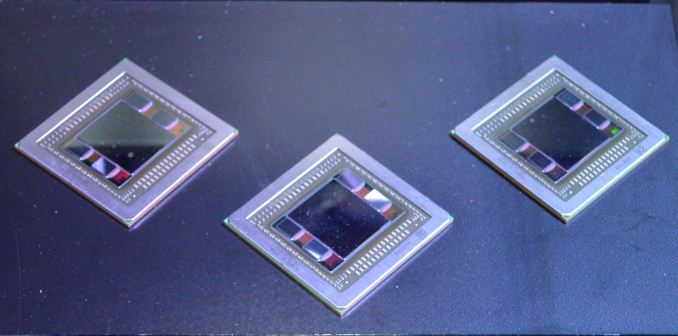

Finally, as large as the Fiji GPU is, the silicon interposer it sits on is even larger. The interposer measures 1011mm2, nearly twice the size of Fiji. Since Fiji and its HBM stacks need to fit on top of it, the interposer must be very large to do its job, and in the process it pushes its own limits. The actual interposer die is believed to exceed the reticle limit of the 65nm process AMD is using to have it built, and as a result the interposer is carefully constructed so that only the areas that need connectivity receive metal layers. This allows AMD to put down such a large interposer without actually needing a fab capable of reaching such a large reticle limit.

What’s interesting from a design perspective is that the interposer and everything on it is essentially the heart and soul of the GPU. There is plenty of power regulation circuitry on the organic package and even more on the board itself, but within the 1011mm2 floorplan of the interposer, all of Fiji’s logic and memory is located. By mobile standards it’s very nearly an SoC in and of itself; it needs little more than external power and I/O to operate.

458 Comments

View All Comments

Navvie - Thursday, July 2, 2015 - link

"Which is not say I’m looking" (paragraph 5, first line).Missing a "to" I think.

watzupken - Thursday, July 2, 2015 - link

Brilliant review. Well worth the wait. Thanks Ryan.Taracta - Thursday, July 2, 2015 - link

ROPs, ROPs, ROPs! Hows can they ~ double everything else and keep the same amount of ROPs and expect to win?Thatguy97 - Thursday, July 2, 2015 - link

maybe something to do with cost or yieldtipoo - Thursday, July 2, 2015 - link

They literally hit the size limits interposers can scale up to with this chip - so they can't make it any bigger to pack more transistors for more ROPs, until a die shrink. So they decided on a tradeoff, favouring other things than ROPs.Kevin G - Thursday, July 2, 2015 - link

They had a monster shader count and likely would be fine if they went to 3840 max to make room for more ROPs. 96 or 128 ROPs would have been impressive and really made this chip push lots of pixels. With HBM and the new delta color compression algorithm, there should be enough bandwidth to support these additional ROPs without bottle necking them.AMD also scaled the number of TMUs with the shaders but it likely wouldn't have hurt to have increased them by 50% too. Alternatively AMD could have redesigned the TMUs to have better 16 bit per channel texture support. Either of these changes would have put the texel throughput well beyond the GM200's theoretical throughput. I have a feeling that this is one of the bottlenecks that helps the GM200 pull ahead of Fiji.

tipoo - Friday, July 3, 2015 - link

Not saying it was the best tradeoff - just explaining. They quite literally could not go bigger in this case.testbug00 - Sunday, July 5, 2015 - link

the performances scaling as resolution increase is better than Nvidia, implying the ROPs aren't the bottleneck...chizow - Sunday, July 5, 2015 - link

No, that implies the shaders are the bottleneck at higher resolutions while ROP/fillrate/geometry remained constant. While Nvidia's bottleneck at lower resolutions isn't shader bound but their higher ROP/fillrate allows them to realize this benefit in actual FPS, AMD's ROPs are saturated and simply can't produce more frames.Ryan Smith - Thursday, July 2, 2015 - link

Right now there's not a lot of evidence for R9 Fury X being ROP limited. The performance we're seeing does not have any tell-tale signs of being ROP-bound, only hints here and there that may be the ROPs, or could just as well be the front-end.While Hawaii was due for the update, I'm not so sure we need to jump up in ROPs again so soon.