ARM Challenging Intel in the Server Market: An Overview

by Johan De Gelas on December 16, 2014 10:00 AM ESTIntel's Future: Xeon-D

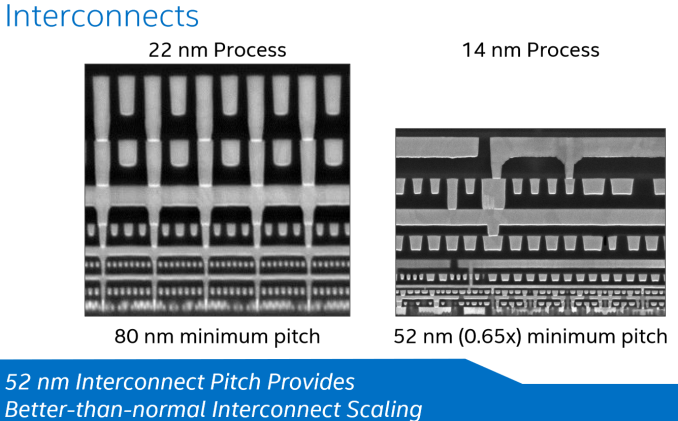

Intel's response to all of these competitors is relatively simple. The Atom C2000 might not be strong enough to turn the ARM tide and the Xeon E3 might lose a performance per watt battle here and there due to the extra PCH chip it needs. So take the two and unify the advantages of the Xeon E3 and Atom C2000 in one chip, the Xeon-D. Then use Intel's main industry advantage, the most advanced process technology, in this case the 14nm 2nd generation of trigate transistors.

The Xeon-D should have it all (almost): a Broadwell core that can go as low as 2W per core at 1.2GHz. It can also deliver great single-threaded performance if necessary, as one core can go as high as 2.9GHz! Some people have said that Intel will have a very hard time offering the same richness of integrated hardware blocks as the ARM licensees, but frankly the Xeon-D has almost everything a server application can need: several PCIe 3.0 root complex (24 lanes), 10GbE Ethernet, and PCH logic (6x SATA, USB 3.0/2.0, 8 lanes of PCIe 2.0 and 1GB Ethernet) are all integrated.

Eight of those Broadwell cores will find a place in a 45W SoC. Considering Intel needs 6W to run two cores (and a small integrated GPU) at 1.4GHz, we would not be surprised if the new Xeon-D could reach 1.8GHz or more and that Turbo Boost clocks will be above 3GHz.

The only disadvantage that the SoC has compared to some of the ARM SoCs is the dual-channel memory controller. The Xeon-D will be available in Q3 2015. While roadmaps should always be read with caution, it must be said that Intel rarely delays its products more than a few months. Intel has been executing very well, almost like clock work.

78 Comments

View All Comments

patrickjchase - Thursday, December 18, 2014 - link

It's been a while since I worked on this stuff, but I don't think that the statement that "CCN is very comparable to the ring bus found inside all Xeon processors beginning with Sandy Bridge" is quite right.CCN

patrickjchase - Thursday, December 18, 2014 - link

Finishing my comment:CCN

stefstef - Wednesday, December 17, 2014 - link

the idea of having an energy efficient design certainly will pay off. nvidia and samsung showed that having i.e. 4 cores and a fifth core dedicated to the energy management can be a good low cost solution. i dont often read the articles at anandtech because they are usually boring. although i am happy to place a coment here. arm rules in certain fields but in a couple of years only because intel will allow them to do so. every company needs a room to live in. another american breakfast for the chinese who will get their share in the processor market as well.milli - Thursday, December 18, 2014 - link

I don't understand how ARM is suddenly going to succeed while MIPS and PowerPC have already tried and failed. I feel that ARM is more of a market trend than anything else (in the server market).Even the current ARM server SOC manufacturers have already tried to penetrate the server market. Cavium and Broadcom already had custom designed low-power MIPS SOCs. IBM, Applied Micro and Freescale have had a bunch of low-power PowerPC options.

By the time any of these products is released, Intel is going to have a better alternative thanks to their process advantage. No IT manager is going to manage to convince any of the corporate fat-cats that a huge overhaul is needed. Same story over again.

yuhong - Friday, December 19, 2014 - link

"Unfortunately their 16GB DIMMs will only work with the Atom C2000, leading to the weird situation that the Atom C2000 supports more memory than the more powerful Xeon E3."I think the reason is software related. More precisely, the Memory Reference Code (MRC).

intiims - Tuesday, December 30, 2014 - link

If You want to know something about External Hard Drives visit http://www.hddmag.com/adrian1987 - Monday, January 5, 2015 - link

Hi. The Haswell core can actually have a max IPC of 6 instructions per cycle using macro-fusion not 5 as listed here (assuming the code is ideal). It has 2 execution units that can handle fused ALU and branch instructions. Source: http://www.anandtech.com/show/6355/intels-haswell-...aaronjoue - Tuesday, April 7, 2015 - link

Here is the real micro server. http://www.ambedded.com.tw/pt_list.php?CM_ID=20140...http://wiki.ambedded.com.tw/index.php?title=MicroS...

7 & 21 nodes in a chassis

It support Ubuntu and open source Ceph.