The Google Nexus 9 Review

by Joshua Ho & Ryan Smith on February 4, 2015 8:00 AM EST- Posted in

- Tablets

- HTC

- Project Denver

- Android

- Mobile

- NVIDIA

- Nexus 9

- Lollipop

- Android 5.0

The Secret of Denver: Binary Translation & Code Optimization

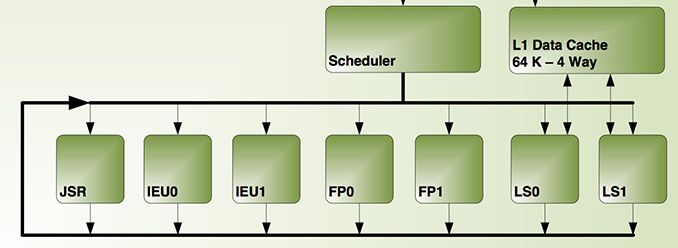

As we alluded to earlier, NVIDIA’s decision to forgo a traditional out-of-order design for Denver means that much of Denver’s potential is contained in its software rather than its hardware. The underlying chip itself, though by no means simple, is at its core a very large in-order processor. So it falls to the software stack to make Denver sing.

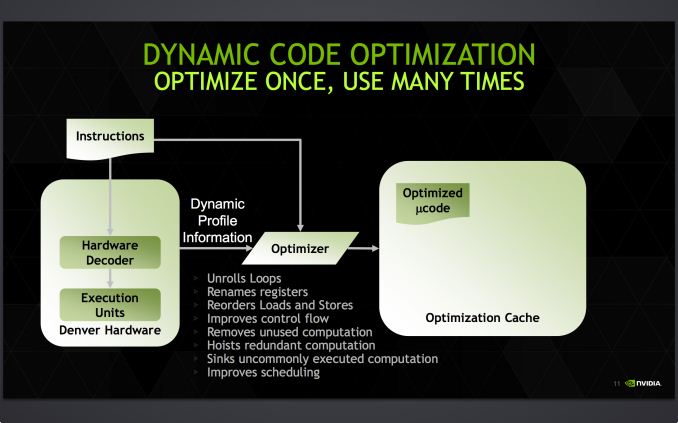

Accomplishing this task is NVIDIA’s dynamic code optimizer (DCO). The purpose of the DCO is to accomplish two tasks: to translate ARM code to Denver’s native format, and to optimize this code to make it run better on Denver. With no out-of-order hardware on Denver, it is the DCO’s task to find instruction level parallelism within a thread to fill Denver’s many execution units, and to reorder instructions around potential stalls, something that is no simple task.

Starting first with the binary translation aspects of DCO, the binary translator is not used for all code. All code goes through the ARM decoder units at least once before, and only after Denver realizes it has run the same code segments enough times does that code get kicked to the translator. Running code translation and optimization is itself a software task, and as a result this task requires a certain amount of real time, CPU time, and power. This means that it only makes sense to send code out for translation and optimization if it’s recurring, even if taking the ARM decoder path fails to exploit much in the way of Denver’s capabilities.

This sets up some very clear best and worst case scenarios for Denver. In the best case scenario Denver is entirely running code that has already been through the DCO, meaning it’s being fed the best code possible and isn’t having to run suboptimal code from the ARM decoder or spending resources invoking the optimizer. On the other hand then, the worst case scenario for Denver is whenever code doesn’t recur. Non-recurring code means that the optimizer is never getting used because that code is never seen again, and invoking the DCO would be pointless as the benefits of optimizing the code are outweighed by the costs of that optimization.

Assuming that a code segment recurs enough to justify translation, it is then kicked over to the DCO to receive translation and optimization. Because this itself is a software process, the DCO is a critical component due to both the code it generates and the code it itself is built from. The DCO needs to be highly tuned so that Denver isn’t spending more resources than it needs to in order to run the DCO, and it needs to produce highly optimal code for Denver to ensure the chip achieves maximum performance. This becomes a very interesting balancing act for NVIDIA, as a longer examination of code segments could potentially produce even better code, but it would increase the costs of running the DCO.

In the optimization step NVIDIA undertakes a number of actions to improve code performance. This includes out-of-order optimizations such as instruction and load/store reordering, along register renaming. However the DCO also behaves as a traditional compiler would, undertaking actions such as unrolling loops and eliminating redundant/dead code that never gets executed. For NVIDIA this optimization step is the most critical aspect of Denver, as its performance will live and die by the DCO.

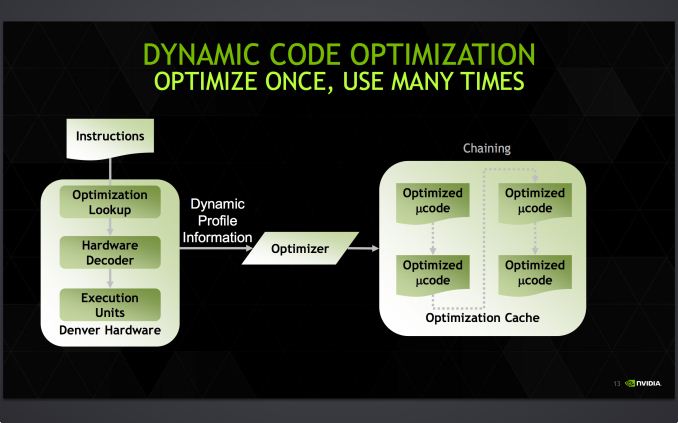

Denver's optimization cache: optimized code can call other optimized code for even better performance

Once code leaves the DCO, it is then stored for future use in an area NVIDIA calls the optimization cache. The cache is a 128MB segment of main memory reserved to hold these translated and optimized code segments for future reuse, with Denver banking on its ability to reuse code to achieve its peak performance. The presence of the optimization cache does mean that Denver suffers a slight memory capacity penalty compared to other SoCs, which in the case of the N9 means that 1/16th (6%) of the N9’s memory is reserved for the cache. Meanwhile, also resident here is the DCO code itself, which is shipped and stored as already-optimized code so that it can achieve its full performance right off the bat.

Overall the DCO ends up being interesting for a number of reasons, not the least of which are the tradeoffs are made by its inclusion. The DCO instruction window is larger than any comparable OoOE engine, meaning NVIDIA can look at larger code blocks than hardware OoOE reorder engines and potentially extract even better ILP and other optimizations from the code. On the other hand the DCO can only work on code in advance, denying it the ability to see and work on code in real-time as it’s executing like a hardware out-of-order implementation. In such cases, even with a smaller window to work with a hardware OoOE implementation could produce better results, particularly in avoiding memory stalls.

As Denver lives and dies by its optimizer, it puts NVIDIA in an interesting position once again owing to their GPU heritage. Much of the above is true for GPUs as well as it is Denver, and while it’s by no means a perfect overlap it does mean that NVIDIA comes into this with a great deal of experience in optimizing code for an in-order processor. NVIDIA faces a major uphill battle here – hardware OoOE has proven itself reliable time and time again, especially compared to projects banking on superior compilers – so having that compiler background is incredibly important for NVIDIA.

In the meantime because NVIDIA relies on a software optimizer, Denver’s code optimization routine itself has one last advantage over hardware: upgradability. NVIDIA retains the ability to upgrade the DCO itself, potentially deploying new versions of the DCO farther down the line if improvements are made. In principle a DCO upgrade not a feature you want to find yourself needing to use – ideally Denver’s optimizer would be perfect from the start – but it’s none the less a good feature to have for the imperfect real world.

Case in point, we have encountered a floating point bug in Denver that has been traced back to the DCO, which under exceptional workloads causes Denver to overflow an internal register and trigger an SoC reset. Though this bug doesn’t lead to reliability problems in real world usage, it’s exactly the kind of issue that makes DCO updates valuable for NVIDIA as it gives them an opportunity to fix the bug. However at the same time NVIDIA has yet to take advantage of this opportunity, and as of the latest version of Android for the Nexus 9 it seems that this issue still occurs. So it remains to be seen if BSP updates will include DCO updates to improve performance and remove such bugs.

169 Comments

View All Comments

lucam - Thursday, February 5, 2015 - link

Next time you will write the article for Anand.tuxRoller - Thursday, February 5, 2015 - link

Just tested on my N7 2013. Results were far higher than shown in the chart.SR:64.2->76.1

SW:18.4->30.1

RR:11.2->13.4

RW:0.7->3.1

mpokwsths - Thursday, February 5, 2015 - link

Well, your results are far far more improved than 10% Andrei says.3 devices by 2 different users, all showed vast improvements (10-500%).

Only they refuse to acknowledge it.

Who knows, it seems Anandtech guys are on Apple's payroll...

eiriklf - Thursday, February 5, 2015 - link

Just wanted to note that on the NAND performance front, I believe the android devices which beat the nexus 9 in sequential speed use emmc 5.0 while the nexus uses a high quality emmc 4.5. I think this is because the tegra K1 SoC does not support emmc 5.0.tviceman - Wednesday, February 4, 2015 - link

Better late than never, although being this late is indeed a big letdown.Onto the hardware, looks like Denver is an interesting first custom SoC from Nvidia. Solid in some respects, lacking in others. I think it's a solid building block from which to work on and improve. I hope Nvidia continues the custom ARM core path and gets more design wins (if warranted) moving forward.

kepstin - Wednesday, February 4, 2015 - link

The Denver chip design is pretty interesting, but it reminds me very strongly of another mobile-targeted chip that didn't do well in the marketplace; the Transmeta Crusoe.Both are VLIW designs with in-order execution, both rely on software code translation that runs on the CPU itself. Both even used a partitioned section of system ram as a translated ops cache.

The most significant difference that I see between them is the addition of a native ARM decoder to the Denver CPU; the Crusoe didn't have a native X86 decoder and relied on the dynamic translation for all code that it executed.

I had a Crusoe for a while in a Sony Vaio; it was used in some of the very small/lightweight ultraportable laptops by Japanese manufacturers for a while.

phoenix_rizzen - Wednesday, February 4, 2015 - link

Didn't a large group of Transmeta devs get hired by Nvidia?ABR - Thursday, February 5, 2015 - link

Crusoe lost because Transmeta woke the sleeping giant Intel to the value of low-power, and then a group of 100 people couldn't keep up the resulting engineering race. The x86 world would be a pretty different place today if that hadn't occurred. But I'd say the jury is still out on the overall capability of the VLIW + morphing approach.frenchy_2001 - Thursday, February 5, 2015 - link

I would second that. A quick search returned a licensing agreement where nvidia licensed Transmeta's technology.This could be a good part of Denver.

About in order execution, the biggest experiment was from intel: itanium.

kgh00007 - Wednesday, February 4, 2015 - link

It's 3 months late, the nexus 9 was released on the 3rd of November!!No excuses, but it's just too late to help people make an informed decision!! Just like dog years, one year for a tablet is like 7 technology(dog) years!!