ADATA Premier SP610 SSD (256GB & 512GB) Review: Say Hello to an SMI Controller

by Kristian Vättö on June 27, 2014 2:00 PM EST- Posted in

- Storage

- SSDs

- ADATA

- SP610

- Silicon Motion

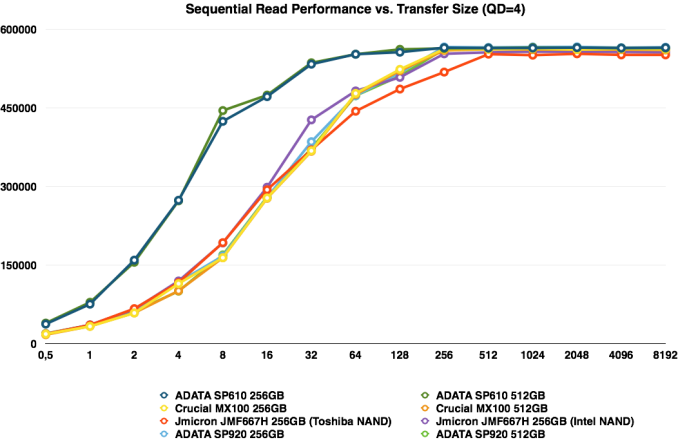

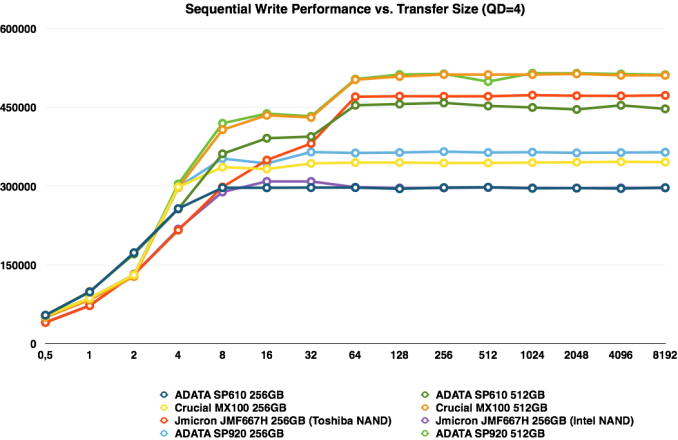

Performance vs. Transfer Size

ATTO is a useful tool for quickly benchmarking performance across various transfer sizes. You can get the complete data set in Bench. Read performance is again excellent and beats all the other value SSDs. I'm surprised by how good the read performance actually is. I'm guessing the custom RISC CPU helps with its more efficient design but it could simply be a matter of firmware design as well. Write performance, on the other hand, is average and comparable to the JMF667H. I wonder if Crucial's advantage in write performance is due to higher binned NAND because generally speaking Micron and other NAND manufacturers keep the best NAND to themselves.

Click for full size

24 Comments

View All Comments

skiboysteve - Sunday, June 29, 2014 - link

Very very cool. Thanks for sharingshodanshok - Sunday, June 29, 2014 - link

Really interesting. How can we help in benchmarking?smadhu - Sunday, June 29, 2014 - link

WE are trying to get a benchmarking setup on a Zync zedboard card first. It is a partially simulated environment. That PCIe and the NAND flash are simulated using RAM but the controller and the CPU is the actual IP. Most universities want this setup first since it assumes an infinite source and sink and let you tune the protocol and the controller.We will also simultaneously release using the Xilinx AC701 card. This is a PCIe card but has no bulitin NAND modules. We are working with Xilinx to get a NAND module done ASAP. But even without it at lease the env. get more real in the sense that now the IP and PCIe are actual IP and only NAND is simulated.

Once proven on this card, we are creating a dedicated PCIe SSD card that will also be open sourced. That will a full fledged card with user replaceable NAND modules and will also be cost optimized. Hopefully Asian vendors will clone those in large quantities to being down cost. We neither charge any royalty nor do we apply for patents on an of our IP. Since the NAND modules are standard, we hope to create a 3rd party eco-system for NAND modules. So you can upgrade your PCIe card when you run out of storage space or when new NAND tech is available.

This effort is actually kind of a trojan horse for our larger project, the SHAKTI open source CPU. We have about 6 classes/families of CPU being developed, ranging from Cortex M-3 level microcontrollers to Xeon class 16-24 core server parts. HPC variants will have 512 bit SIMD with 64-100 cores (NoC fabric). All BSD licensed open source of course. We are running GCC on the cores now and wrapping up SoC integration for the lower end cores. Hope to get Linux running by Christmas. Low end target is the Diglinet Nexus 4 FPGA board

Th cores are important for Storage since we allows us to do the following

- modify the ISA for storage specific operations and remove instructions that is not needed for storage

- allow user defined code to run on the storage controllers

- add functional units for database acceleration

All SoC integration is via AXI framework, so vendors can easily use this IP without retraining their engineers. WE are not alone in such cores, Cambridge just released their MIPS compatible secure CPU.

see beri-cpu.org.

UCB will also shortly release its full blown cores.

Somebody asked me why we did such massive open source HW IP without expecting monetary returns. My answer was simple, I could either build a billion dollar startup or remove a few billion dollars from the IP market ! I chose the latter !

Beagus - Monday, June 30, 2014 - link

Page one Table MB/GB/TB.As always - Good work