Intel Unveils Meteor Lake Architecture: Intel 4 Heralds the Disaggregated Future of Mobile CPUs

by Gavin Bonshor on September 19, 2023 11:35 AM ESTSoC Tile, Part 1: Low-Power Island E-Cores, Designed for Ultimate Efficiency

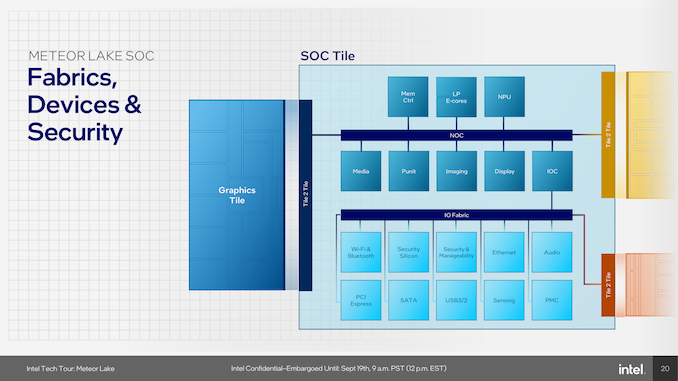

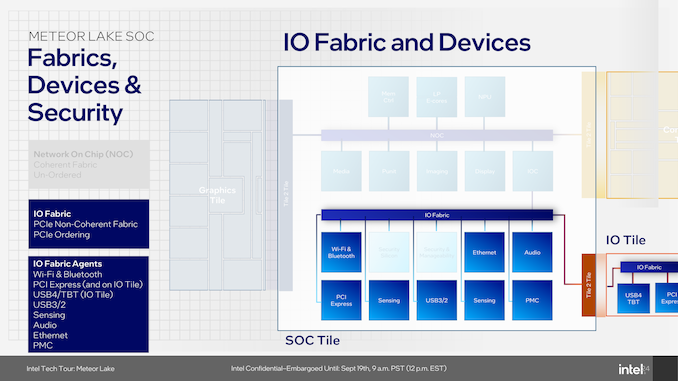

Diving a little deeper into the SoC tile within Intel's Meteor Lake architecture, Intel hasn't just opted for a minor change but has made a significant leap forward, especially regarding I/O fabric scalability. The SoC tile itself isn't built on Intel 4 like the compute tile but is made by TSMC on their N6 node. Intel has ditched the old limitations of mesh routing by implementing a Network-On-Chip (NOC) on the silicon. This isn't just about making data lanes faster; it's about outlining smarter and more power-efficient access to memory. Likely an innovation from Intel's acquisition of NetSpeed back in 2018, which specialized in NoC and Fabric IP for SoCs, Intel opting for a physical NOC allows Intel to reduce the limits on bandwidth. Using EMIB and the nature of 2D scaling, the data paths are a lot shorter, translating into less power loss, but shorter wires also help reduce overall latency penalties.

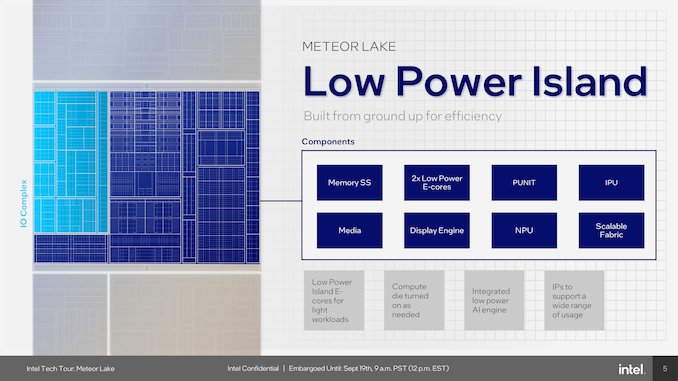

Switching gears to low-power workload efficiency, Meteor Lake incorporates E-cores directly into the SoC tile, which Intel calls Low Power Island (LP) E-cores. Think of it as Intel's way of saying, "Why use a sledgehammer when a scalpel will do?". This means that the LP E-Cores are driven purely from a power-saving perspective. Having these LP E-cores available for workloads with the aid of Intel's Thread Director means lighter threads and background tasks that don't require the grunt of the P and E-cores on the compute tile can be directed onto the lower-powered LP E-cores.

While both the E and LP E-cores are based on the same Crestmont microarchitecture, the E-cores on the compute tile are built on Intel 4, along with the P-cores. The LP E-cores are made on TSMC's N6 node, like the rest of the SoC tile. These low-power island E-cores are tuned for finer-grained voltage control through an integrated Digital Linear Voltage Regulator (DLVR), and they also have a lower voltage-to-frequency (V/F) curve than the big E-cores on the compute tile, meaning they can operate with a lower power cost, thus saving power when transitioning low-intensity workloads off of the compute tile and onto the LP E-cores.

Part of the disaggregated nature of Foveros combined with individual power management controllers (PMC) within each tile means that IP blocks can be independently powered on or off when required.

SoC Tile: Bandwidth Scalability, Can't Stop The NOC

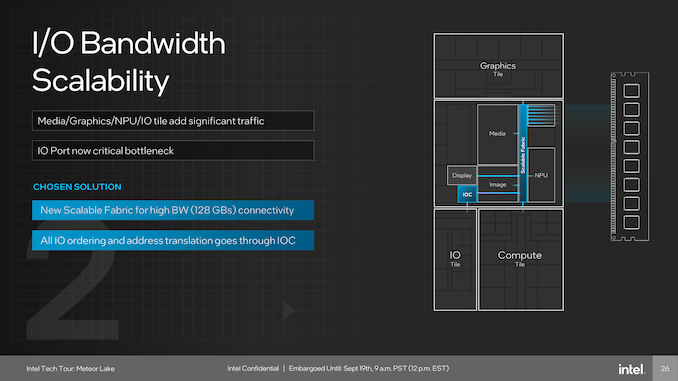

So adding a variety of tiles requires a highly competent pathing to ensure bandwidth is adequately structured. As I/O bandwidth bottlenecking was a major concern in previous iterations, Intel aims to solve bandwidth flow restrictions with a couple of solutions.

The first is through the scalability of the I/O bandwidth, which Intel does by adding what it calls 'Scalable Fabric,' which is configured for up to 128 GB/s of bandwidth throughput. All of the I/O ordering and address translation is fed through the IOC, while Intel has implanted a Network-on-Chip (NOC) to interconnect many of the different areas of the SoC.

The Network-on-Chip or NOC is designed to be coherent, and for Meteor Lake on Intel 4, this uses unordered processing, which moves data in an unordered fashion. Connecting all the tiles together through the NOC and independently through the IOC gives plenty of bandwidth headroom for devices or agents requiring it. The NOC is directly connected to the compute and graphics tile, while other elements, including the traffic fed directly through the LP E-cores on the SoC tile, media, display, the NPU, and the imaging processing unit (IPU), all going through the NOC. In terms of the connection to the I/O tile, this is connected directly to the IO fabric and then is fed through the IOC, which then goes directly to the NOC.

The SoC tile also integrates Wi-Fi 6E and can be made to support the latest Wi-Fi 7 standard. Having a future-proof method of including Wi-Fi 7 and Bluetooth 5.4 can add the next level of wireless connectivity to Intel's mobile platform. Wi-Fi 7 offers 320 MHz of bandwidth, doubling the channel width compared to its predecessor, Wi-Fi 6. It also uses 4096-QAM (4K QAM) to enable transmission speeds capable of hitting 5.8 Gbps.

We're still waiting for clarification on what this actually means. Whether it's supportive of Wi-Fi 7 or if there's some underlying compatibility within the Wi-Fi MAC integrated into the silicon. One option could be that Intel is adding a full external controller into the silicon to get to Wi-Fi 7 instead of CNVio splitting up parts of the radio stack. We have asked Intel for more details and will update you when we have a response.

That being said, Intel discloses 'support' for Wi-Fi 7 and BT 5.4, but there's a chance Intel could differentiate which wireless MAC is implemented into different chip segments. An example would be an Intel 9 Ultra SKU, bolstered by Wi-Fi 7 support, whereas a lower-end SKU like a Core 3 might utilize Wi-Fi 6E to save on cost.

Additional features include Multi-Resource Unit (RU) Puncturing and Military-grade security with WPA3 that supports GCMP-256 encryption to ensure both speed and security when connected to a wireless network. Unique features like Multi-Link Operation (MLO) in Wi-Fi 7 are designed to reduce latency and jitter by up to 60%, making it a competent solution for various user's connectivity needs. Adding Bluetooth 5.4 further complements this by improving audio quality, and it is claimed to offer up to 50% lower power consumption for longer battery life.

Also present on the SoC tile is the display controller and the media engine from the GPU. These are always-on (or at least, mostly-on) blocks that do not need to be built on a cutting-edge process node, making them good candidates to place on the SoC tile. Meteor Lake offers support for 8K HDR and AV1 video playback and contains native HDMI 2.1 and DisplayPort 2.1 connectivity.

Finally, the SoC tile also includes other key platform components, such as PCIe lanes, which are integral for connectivity to external devices such as discrete graphics cards and the platform's I/O capabilities, such as USB 4 and 3, as well as offering a direct interconnect to a separate I/O tile with Thunderbolt 4 and additional PCIe lanes. While we've touched on wireless connectivity, the SoC tiler also includes Ethernet support, although Intel hasn't disclosed yet which PHY will be included; it is likely to be capable of 2.5 GbE at the minimum.

A Note on Meteor Lake's Security Features: New Silicon Security Engine (ISSE)

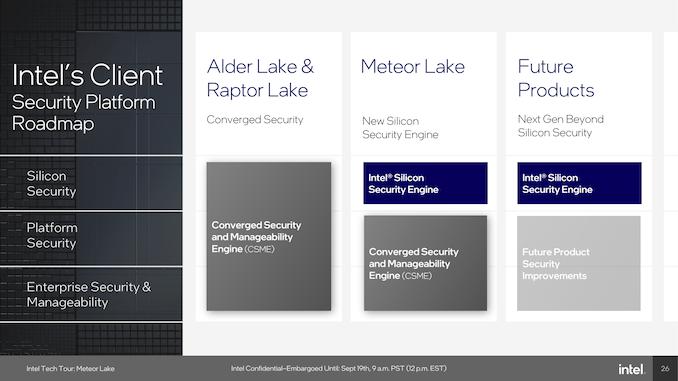

Security has also been given closer attention in Meteor Lake. The architecture introduces the Intel Silicon Security Engine (ISSE), a dedicated component focused solely on securing things at a silicon level. Various vulnerabilities have been at the forefront of media over the last few years, including Meltdown, Spectre, and Foreshadow.

With real threats around the world, securing data is ever prevalent, and CPU architects and designers not only need to consider performance and efficiency, but security and doing some architecturally is just as important as a competent software stack. The Converged Security and Manageability Engine (CSME) has also been partitioned to further enhance platform security. These features collectively work to give a wide range of on-chip and off-chip securities designed to mitigate attacks on multiple fronts.

107 Comments

View All Comments

kwohlt - Tuesday, September 19, 2023 - link

The market for people who find TB4 to be insufficient is too small to delay MTL for themExotica - Wednesday, September 20, 2023 - link

Source or market research please ? I have the feeling that many enthusiasts will not be interested. Because of missing TB5. And also because of its ipc improvements (or lack thereof) vs raptor lake.Meteor lake certainly is impressive. But it seems to be less about raw performance and more about the process improvement. Foveros. Chiplets. Euv. New manufacturing abilities. AI engine. Power efficiency. Newish gpu.

But from a generational uplift perspective, from a raw cpu performance to the thunderbolt io, I t’s not much of an upgrade for enthusiasts. Intel should’ve just launched MTL in Dec and then announced TB5 in January. What was the reason to announce TB5 before the MTL reveal?

I guess we will have to wait on arrow lake mobile (if that’s a thing) or lunar lake for TB5 on laptops.

kwohlt - Wednesday, September 20, 2023 - link

You need Market Research to tell you TB4 bandwidth is sufficient for majority of users? 40Gb/s can drive easily gigabit interent and multiple monitors. Most jobs do not require more. At the Fortune 500 I manage IT for, we still haven't even switched to thunderbolt as 3.1 docks are more than sufficient.There's market research on TB4 trends for purchase, that i'm not going to pay for, so we'll just have to settle on "Intel's market research determined that delaying their next gen product line for this 1 feature, potentially causing delays across OEMs 2024 product lines in the process, was not worth it"

PeachNCream - Thursday, September 21, 2023 - link

"...many enthusiasts..."While that segment might be outspoken, the percentage of the overall market is tiny and the percentage that cares among that fraction is even smaller. Basement dweller computer nerds and the e-sports people they idolize don't buy the hundreds of thousands of units that a computer manufacturer purchases. Sure, they get a minor head nod from the company to keep them from slobbering and raving about being ignored, but that's done because it's cheap to coddle them with marketing speak and make them believe features are targeted at them so their ego balloons aren't popped and sites like this have a bone or two to throw them once in a while, but ultimately, no one cares what they want as long as they fanboy argue in favor of their preferred brand with other nerds that like the competition.

TheinsanegamerN - Thursday, September 21, 2023 - link

Exactly. TB5 is exciting and meteor lake is mostly DoA without it. Who would invest thousands into a machine that cant make use of newer functionality?KaarlisK - Tuesday, September 19, 2023 - link

Was this just written by having an AI interpret the slides? And then OCR failed?"This means that higher Out-of-Service (OoS) work is allocated to P-cores for more demanding and intensive workloads, while lower Quality-of-Service (QoS) workloads are directed to E-cores, primarily to save power"

Ryan Smith - Tuesday, September 19, 2023 - link

No, it was done by a sleep-deprived human.KaarlisK - Tuesday, September 19, 2023 - link

Thank you for the explanation.The problem is, I caught at least three more mistakes like this, where a wrong assumption is made about what the text on a slide actually means. In which case (knowing that I'm not an expert), how can I be certain that there aren't many more mistakes that I haven't spotted?

We do come to Anandtech for in-depth analysis, which requires that trust.

Ryan Smith - Tuesday, September 19, 2023 - link

The blunt answer is that we're imperfect (to err is human). We've made mistakes in the past and will continue to do so in the future. But we always own up to those mistakes, and will correct anything if we catch it (or if it gets pointed out).DannyH246 - Tuesday, September 19, 2023 - link

Wow! Intel have some revolutionary ideas here!! Their chiplet approach will change the industry.Would be what i'd have said if they'd have presented this 6 years ago. My response today is...meh.