AMD Zen 4 Ryzen 9 7950X and Ryzen 5 7600X Review: Retaking The High-End

by Ryan Smith & Gavin Bonshor on September 26, 2022 9:00 AM ESTZen 4 Execution Pipeline: Familiar Pipes With More Caching

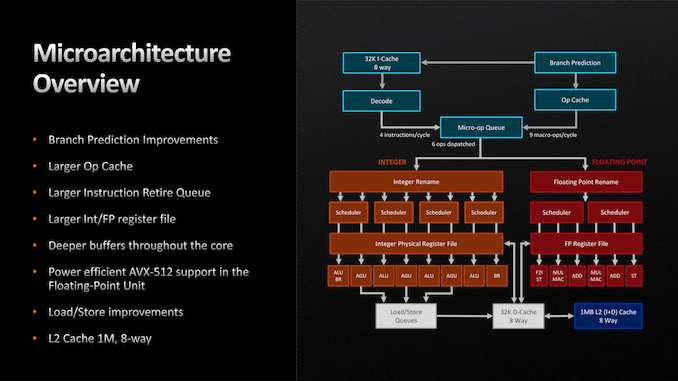

Finally, let’s take a look at the Zen 4 microarchitecture’s execution flow in-depth. As we noted before, AMD is seeing a 13% IPC improvement over Zen 3. So how did they do it?

Throughout the Zen 4 architecture, there is not any single radical change. Zen 4 does make a few notable changes, but the basics of the instruction flow are unchanged, especially on the back-end execution pipelines. Rather, many (if not most) of the IPC improvements in Zen 4 come from improving cache and buffer sizes in some respect.

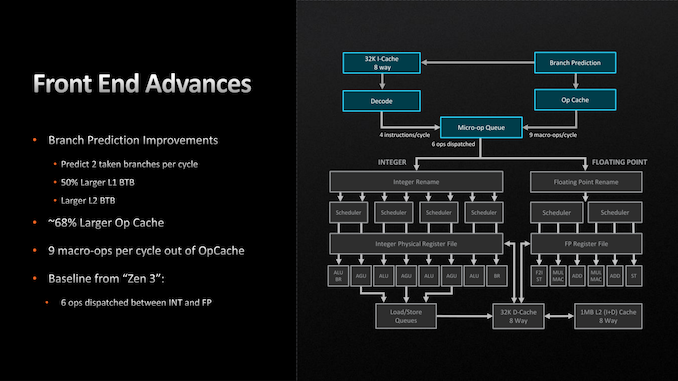

Starting with the front end, AMD has made a few important improvements here. The branch predictor, a common target for improvements given the payoffs of correct predictions, has been further iterated upon for Zen 4. While still predicting 2 branches per cycle (the same as Zen 3), AMD has increased the L1 Branch Target Buffer (BTB) cache size by 50%, to 2 x 1.5k entries. And similarly, the L2 BTB has been increased to 2 x 7k entries (though this is just an ~8% capacity increase). The net result being that the branch predictor’s accuracy is improved by being able to look over a longer history of branch targets.

Meanwhile the branch predictor’s op cache has been more significantly improved. The op cache is not only 68% larger than before (now storing 6.75k ops), but it can now spit out up to 9 macro-ops per cycle, up from 6 on Zen 3. So in scenarios where the branch predictor is doing especially well at its job and the micro-op queue can consume additional instructions, it’s possible to get up to 50% more ops out of the op cache. Besides the performance improvement, this has a positive benefit to power efficiency since tapping cached ops requires a lot less power than decoding new ones.

With that said, the output of the micro-op queue itself has not changed. The final stage of the front-end can still only spit out 6 micro-ops per clock, so the improved op cache transfer rate is only particularly useful in scenarios where the micro-op queue would otherwise be running low on ops to dispatch.

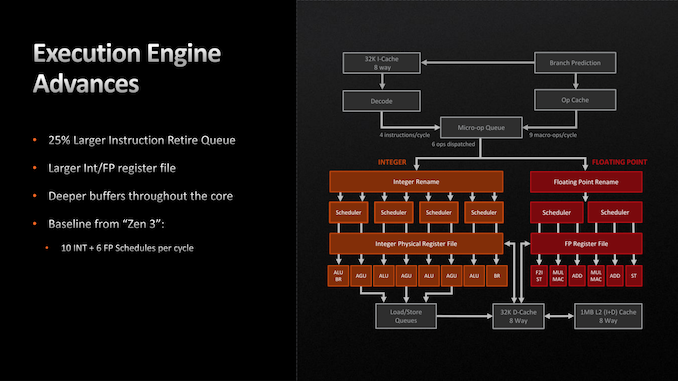

Switching to the back-end of the Zen 4 execution pipeline, things are once again relatively unchanged. There are no pipeline or port changes to speak of; Zen 4 still can (only) schedule up to 10 Integer and 6 Floating Point operations per clock. Similarly, the fundamental floating point op latency rates remain unchanged as 3 cycles for FADD and FMUL, and 4 cycles for FMA.

Instead, AMD’s improvements to the back-end of Zen 4 have here too focused on larger caches and buffers. Of note, the retire queue/reorder buffer is 25% larger, and is now 320 instructions deep, giving the CPU a wider window of instructions to look through to extract performance via out-of-order execution. Similarly, the Integer and FP register files have been increased in size by about 20% each, to 224 registers and 192 registers respectively, in order to accommodate the larger number of instructions that are now in flight.

The only other notable change here is AVX-512 support, which we touched upon earlier. AVX execution takes place in AMD’s floating point ports, and as such, those have been beefed up to support the new instructions.

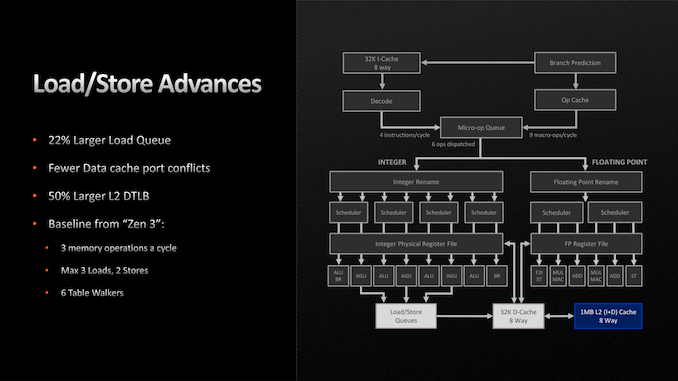

Moving on, the load/store units within each CPU core have also been given a buffer enlargement. The load queue is 22% deeper, now storing 88 loads. And according to AMD, they’ve made some unspecified changes to reduce port conflicts with their L1 data cache. Otherwise the load/store throughput remains unchanged at 3 loads and 2 stores per cycle.

Finally, let’s talk about AMD’s L2 cache. As previously disclosed by the company, the Zen 4 architecture is doubling the size of the L2 cache on each CPU core, taking it from 512KB to a full 1MB. As with AMD’s lower-level buffer improvements, the larger L2 cache is designed to further improve performance/IPC by keeping more relevant data closer to the CPU cores, as opposed to ending up in the L3 cache, or worse, main memory. Beyond that, the L3 cache remains unchanged at 32MB for an 8 core CCX, functioning as a victim cache for each CPU core’s L2 cache.

All told, we aren’t seeing very many major changes in the Zen 4 execution pipeline, and that’s okay. Increasing cache and buffer sizes is another tried and true way to improve the performance of an architecture by keeping an existing design filled and working more often, and that’s what AMD has opted to do for Zen 4. Especially coming in conjunction with the jump from TSMC 7nm to 5nm and the resulting increase in transistor budget, this is good way to put those additional transistors to good use while AMD works on a more significant overhaul to the Zen architecture for Zen 5.

205 Comments

View All Comments

RomanPixel - Tuesday, September 27, 2022 - link

Me too! Replykmalyugin - Monday, September 26, 2022 - link

Wow, this article is almost unreadable. Was spellchecker turned off? Replyjonkullberg - Monday, September 26, 2022 - link

Gaming benchmarks with DDR5-6000 CL30 please! ReplyBushLin - Monday, September 26, 2022 - link

Exactly Replyxol - Monday, September 26, 2022 - link

wtf am I reading (context a part with tdp up to 170W from 105W) :"This has been possible through superior power efficiency, as Zencally a Zen 3 refinement, but on the new TSMC 5 nm process node (from TSMC 7 nm). This efficiency has allowed AMD to increase the overall TDP to 170 W from the previous 105 W but without too much penalty."

I can't even .. "too much penalty" ??

.. Looks like Zen has reached the end of the road imo (it had a good run) - none of the improvements here are from AMD - new DDR5, new 5nm node. The rest is "increase clocks/tdp" just like when Intel was stuck on 14nm.

I just don't know where they are going from here Reply

Threska - Monday, September 26, 2022 - link

Well we have " While Ryzen 7000 can drive a 2 DPC/4 DIMM setup, you’re going to lose 31% of your memory bandwidth if you go that route. So for peak performance, it’ll be best to treat Ryzen 7000 as a 1 DPC platform." and " Unfortunately, the compatibility situation is essentially unchanged from the AM4 platform, which is to say that while the CPU supports ECC memory, it’s going to be up to motherboard manufacturers to properly validate it against their boards.". The memory situation seems like a sticking point for a good while till things mature. ReplyBushLin - Monday, September 26, 2022 - link

Did you read the article? Put it in eco mode (105W for a 170W part) and it still stomps over everything in MT performance. Zen 4 is more about platform improvements, Zen 5 will be the microarchitecture overhaul. ReplyBushLin - Monday, September 26, 2022 - link

Stomping everything at 65W even! Replyxol - Tuesday, September 27, 2022 - link

Impressed that it's nominally $100 cheaper than a 5950X .Got to admit that. Replyxol - Tuesday, September 27, 2022 - link

Eco mode does perform better eg cinebench- b maybe +23% compared to 5950X, but it's using DDR5 5200 vs DDR4-3200 (?), and the power advantage can be assumed to come from 5nmMy original point still stands for me- 90% of benefits are from node and memory and allowing clocks as high as Tjunction allows - I don't think that is a great showing for AMD Reply